ESE370: Circuit-Level for Digital Systems Transmission Line

advertisement

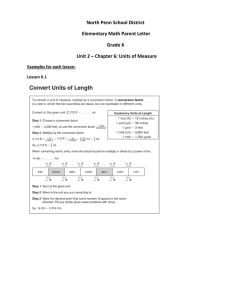

ESE370: Circuit-Level Transmission Line Agenda Modeling, Design, and Optimization for Digital Systems Day 38: December 4, 2013 Transmission Lines Implications 1 Penn ESE370 Fall2013 -- DeHon Transmission Line • Data travels as waves • Line has Impedance • May reflect at end of line € € Penn ESE370 Fall2013 -- DeHon w= Z0 = 1 c0 = LC ε r µr • • • • • • • • • Where arise? General wire formulation Lossless Transmission Line See in action in lab Impedance End of Transmission Line? Termination Implications Discuss Lossy Penn ESE370 Fall2013 -- DeHon 2 Series Termination • What happens here? L C ⎛ R − Z 0 ⎞ Vi ⎜ ⎟ = Vr ⎝ R + Z 0 ⎠ ⎛ 2R ⎞ Vi ⎜ ⎟ = Vt ⎝ R + Z 0 ⎠ 3 € Penn ESE370 Fall2013 -- DeHon 4 € Simulation Series Termination • Rseries = Z0 • Initial voltage divider – Half voltage pulse down line • End of line open circuit – sees single transition to full voltage • Reflection returns to source and sees termination Rseries = Z0 • No further reflections Penn ESE370 Fall2013 -- DeHon 5 Penn ESE370 Fall2013 -- DeHon 6 1 Termination Cases CMOS Driver / Receiver • Driver: What does a CMOS driver look like at the source? • Parallel at Sink – Id,sat=1200µA/µm @ 45nm • Receiver: What does a CMOS inverter look like at the sink? • Series at Source 7 Penn ESE370 Fall2013 -- DeHon 8 Penn ESE370 Fall2013 -- DeHon Coaxial Cable • Inner core conductor: radius r • Insulator: out to radius R • Outer core shield (ground) Some Transmission Lines ⎛ µ ⎞ ⎛ R ⎞ L = ⎜ ⎟ ln⎜ ⎟ ⎝ 2π ⎠ ⎝ r ⎠ Characteristics arise form their geometry (don’t expect you to know these equations – look them up [or given]) • RG-58 Z0= 50Ω – networking, lab • (RG-59 Z0= 75Ω – video) 9 Penn ESE370 Fall2013 -- DeHon Penn ESE370 Fall2013 -- DeHon € Printed Circuit Board • Microstrip line – Trace between planes – Trace over single supply plane w t b ε0 εr εr ⎛ 1 ⎞⎛ µ ⎞ ⎛ 1+ W b ⎞ ⎟ Z 0 = ⎜ ⎟⎜ ⎟ ln⎜ ⎝ 4 ⎠⎝ ε ⎠ ⎜⎝ t + W ⎟⎠ b b € 10 € Printed Circuit Board • Stripline Penn ESE370 Fall2013 -- DeHon ⎛ 1 ⎞⎛ µ ⎞ ⎛ R ⎞ Z 0 = ⎜ ⎟⎜ ⎟ ln⎜ ⎟ ⎝ 2π ⎠⎝ ε ⎠ ⎝ r ⎠ ⎛ 1 ⎞⎛ Z 0 = ⎜ ⎟⎜⎜ ⎝ 2π ⎠⎝ 11 Penn ESE370 Fall2013 -- DeHon w t h ⎞ ⎛ ⎞ µ 4h ⎟ ln⎜ ⎟ ⎟ ⎝ ⎠ 0.536W + 0.67t 0.475 ε + 0.67 ε ( ) 0 ⎠ r 12 € 2 Twisted Pair • Category 5 ethernet cable – 100Ω – V=0.64c0 Implications (you should be able to reason about this) Source: http://en.wikipedia.org/wiki/File:Cat_5.jpg Penn ESE370 Fall2013 -- DeHon 13 14 Penn ESE370 Fall2013 -- DeHon Example Pipeline Bits • 25meter category-5e cable (100Ω, 0.64c) • Supporting 1Gb/s ethernet – 4 pairs at 250Mb/s • For properly terminated transmission line – Do not need to wait for bits to arrive at sink – Can stick new bits onto wire • Time to send data from one end to the other? • Time between bits at 250Mb/s? • Bits in the cable? Penn ESE370 Fall2013 -- DeHon 15 16 Penn ESE370 Fall2013 -- DeHon Eye Diagrams Limits to Bit Pipelining • Watch bits over line on scope – Look at distortion – “open” eye clean place to sample • What limits? (why only 250Mb/s) • Consistent timing of transitions • Well defined high/low voltage levels – Risetime/distortion – Clocking http://en.wikipedia.org/wiki/File:On-off_keying_eye_diagram.svg • Skew • Jitter http://focus.ti.com/analog/docs/gencontent.tsp?familyId=361&genContentId=41762&DCMP=ESD_Solutions&HQS=Other+OT+esd – For bus • Wire length differences between lines Penn ESE370 Fall2013 -- DeHon 17 Penn ESE370 Fall2013 -- DeHon 18 3 Bad “eye” Termination / Mismatch • Wires do look like these transmission lines • We are terminating them in some way when we connect to chip (gate) – Need to be deliberate about how terminate, if we care about high performance http://archive.chipcenter.com/knowledge_centers/asic/todays_feature/showArticle.jhtml?articleID=12800254 Penn ESE370 Fall2013 -- DeHon 19 Where Mismatch? • • • • • • Vias Wire corners? Branches Connectors Board-to-cable Cable-to-cable Penn ESE370 Fall2013 -- DeHon Lossy Transmission Line • How do addition of R’s change? http://www.fpga4fun.com/Hands-on_Flashy.html – Concretely, discretely think about R=0.2Ω every meter on Z0=100Ω • what does each R do? http://wiki.altium.com/display/ADOH/An+Overview+of+Electronic+Product+Development+in+Altium+Designer Penn ESE370 Fall2013 -- DeHon 21 Lossy Transmission Line Penn ESE370 Fall2013 -- DeHon 22 Impedance Change • R’s cause signal attenuation (loss) • What happens if there is an impedance change in the wire? Z0=75Ω, Z1=50Ω – Voltage divider R Z0 – Reduced signal swing at sink – Limits length of transmission line before need to restore signal Penn ESE370 Fall2013 -- DeHon 20 – What reflections and transmission do we get? 23 Penn ESE370 Fall2013 -- DeHon 24 4 Impedance Change Z0=75, Z1=50 Z0=75, Z1=50 • At junction: – Reflects • Vr=(50-75)/(50+75)Vi – Transmits • Vt=(100/(50+75))Vi ⎛ R − Z 0 ⎞ Vi ⎜ ⎟ = Vr ⎝ R + Z 0 ⎠ ⎛ 2R ⎞ Vi ⎜ ⎟ = Vt ⎝ R + Z 0 ⎠ 25 Penn ESE370 Fall2013 -- DeHon € 26 Penn ESE370 Fall2013 -- DeHon € What happens at branch? Branch • Transmission line sees two Z0 in parallel – Looks like Z0/2 27 Penn ESE370 Fall2013 -- DeHon 28 Penn ESE370 Fall2013 -- DeHon End of Branch Z0=50, Z1=25 • What happens at end? • If ends in matched, parallel termination • At junction: – Reflects – No further reflections • Vr=(25-50)/(25+50)Vi – Transmits • Vt=(50/(25+50))Vi ⎛ R − Z 0 ⎞ Vi ⎜ ⎟ = Vr ⎝ R + Z 0 ⎠ 29 Penn ESE370 Fall2013 -- DeHon € ⎛ 2R ⎞ Vi ⎜ ⎟ = Vt ⎝ R + Z 0 ⎠ Penn ESE370 Fall2013 -- DeHon 30 € 5 Branch Simulation Branch with Open Circuit? • What happens if branch open circuit? Penn ESE370 Fall2013 -- DeHon 31 Branch with Open Circuit 32 Penn ESE370 Fall2013 -- DeHon Open Branch Simulation • Reflects at end of open-circuit stub • Reflection returns to branch – …and encounters branch again – Send transmission pulse to both • Source and other branch • Sink sees original pulse as multiple smaller pulses spread out over time Penn ESE370 Fall2013 -- DeHon 33 34 Penn ESE370 Fall2013 -- DeHon Open Branch Simulation Bus http://en.wikipedia.org/wiki/File:DIMMs.jpg • Common to have many modules on a bus – E.g. PCI slots – DIMM slots for memory • High speed bus lines are trans. lines Penn ESE370 Fall2013 -- DeHon 35 Penn ESE370 Fall2013 -- DeHon 36 6 Multi-Drop Bus Multi-drop Bus • Impact of capacitive load (stub) at drop? • Ideal – If tight/regular enough, change Z of line – Open circuit, no load Z0 = L C € 37 Penn ESE370 Fall2013 -- DeHon 38 Penn ESE370 Fall2013 -- DeHon Multi-Drop Bus Transmission Line Noise • Long wire stub? • Frequency limits • Imperfect termination • Mismatched segments/junctions/vias/ connectors • Loss due to resistance in line – Looks like branch • may produce reflections – Limits length 39 Penn ESE370 Fall2013 -- DeHon Idea Admin • Transmission lines – high-speed – high throughput – long-distance signaling • Termination • Signal quality Penn ESE370 Fall2013 -- DeHon 40 Penn ESE370 Fall2013 -- DeHon 1 c0 = LC ε r µr L Z0 = C w= € ⎛ R − Z 0 ⎞ Vr = Vi ⎜ ⎟ € ⎝ R + Z 0 ⎠ 41 • • • • • HW8 due Thursday Last Andre lecture Friday Spencer Review Monday (12/9) Final (12/13) noon Towne 307 Real Genius (Saturday 12/14 2pm) – Levine 307 Penn ESE370 Fall2013 -- DeHon 42 € 7