2-bit ALU and 7-Segment Display - University of Nevada, Las Vegas

advertisement

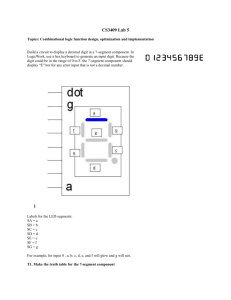

CPE 100L LOGIC DESIGN I CPE 100L LOGIC DESIGN I LABORATORY 7: 2-BIT ALU AND 7-SEGMENT DISPLAY BY GRZEGORZ CHMAJ DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING UNIVERSITY OF NEVADA, LAS VEGAS GOALS: Design a 1-Bit and 2-Bit arithmetic logic units and implement the circuits on the DE0 board. Learn how to use DE0’s 7-segment display. BACKGROUND: ARITHMETIC-LOGIC UNIT (ALU) Arithmetic logic unit is the most important element of microprocessor which performs both math and logic functions. An ALU loads data from input registers, an external Control Unit then tells the ALU what operation to perform on that data, and then the ALU stores its result into an output register. ALU takes many operands as input data, then depending on the operation which is currently programmed in operation selector, it performs this operation on input operand and produces the result. The result is presented on the ALU’s output. Figure 1. Block schematic of ALU DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 1 CPE 100L LOGIC DESIGN I a) logic operation b) arithmetic operation Figure 2. Logic and arithmetic operation in ALU In this lab, we will be working on ALU which performs three functions: logical AND: y = ab logical OR: y = a+b arithmetic addition: y = a+b Figure 3. Implementation of 1-bit ALU While 1-bit ALU, takes 1-bit numbers as arguments (each operand contains 1-bit number), the 2-bit ALU takes two 2-bit operands as inputs. Let’s take the following notation: a0 – first (less significant) bit of first argument a1 – second (most significant) bit of first argument b0 – first (less significant) bit of second argument b1 – second (most significant) bit of second argument y0 – first (less significant) bit of the output result y1 – second (most significant) bit of the output result Then the operations could be expressed as: logic AND – bitwise operation: o y0 = a0 AND b0 o y1 = a1 AND b1 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 2 CPE 100L LOGIC DESIGN I logic OR – bitwise operation: o y0 = a0 OR b0 o y1 = a1 OR b1 arithmetic add: o a1a0 + b1b0 = y1y0 (x1x0 are 2-bit binary numbers) 7-SEGMENT DISPLAY Binary coded decimal (BCD) numbers are often displayed on seven segment display using BCD to seven segment decoder such as 7447, which we use in this lab. Figure 6-3 illustrates BCD to seven segment display circuit. a) 7-segment display segments b) photo of 7-segment display Figure 4. 7-segment display Truth table of BCD to seven segment display decoder is as follows: Table 1. 7-segment display truth table Inputs b3 b2 b1 b0 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Outputs abcdefg 0000001 1001111 0010010 0000110 1001100 0100100 0100000 0001111 0000000 0000100 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 3 CPE 100L LOGIC DESIGN I Inputs representing BCD numbers from 10 to 15 are don’t cares. There are 2 types of 7-segment display: common anode (logical 0 lights up the segment) and common cathode (logical 1 lights up the segment). The schematic of common-anode 7-segment is shown in Fig. 5. Figure 5. Common anode 7-segment display circuit BCD to 7-segment display decoder is the circuit that converts BCD number into its 7-bit representation. We can say, that decoder realizes the truth table shown above. The examples of such decoder are: 7447, 7449. The example circuit of converting BCD into 7-segment is shown in Fig. 5. Figure 6. Example of decoding BCD number using 7447 IC. DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 4 CPE 100L LOGIC DESIGN I LAB DELIVERIES: PRELAB: 1. 7-segment display 1. Apply the rules of K-map to find the expression of the each of the seven outputs. 2. 1-bit ALU: 1. Create 1-bit ALU schematic in Quartus (Figure 3). 2. Perform functional simulation 3. 2-bit ALU: 1. Based on 1-bit ALU, design 2-bit ALU 2. Draw the schematic in Quartus 3. Perform functional simulation Prelab deliveries Include in the report document: 1. Schematics created in Quartus 2. Simulation waveform generated by Quartus 3. Answer the question: what is bitwise operation? Give an example. LAB EXPERIMENTS: 1. Experiment 1: 7-segment display 1. Implement the circuit, which represents 3-bit BCD number on DE0’s board 7-segment display a. Connect 3 bits of a number to switches SW0, SW1, SW2 b. Use HEX0 to display the number a0 a1 decoder a2 2. Demonstrate the circuit to the TA 2. Experiment 2: 1-bit ALU 1. Implement your 1-bit ALU on the DE0 board a. Connect input a to KEY3 b. Connect input b to KEY2 c. Connect selectors to the switches SWx of your choice d. Connect outputs to LEDs of your choice 2. Demonstrate the circuit to the TA DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 5 CPE 100L LOGIC DESIGN I 3. Experiment 3: 2-bit ALU 1. Implement your design of 2-bit ALU on the DE0 board a. Connect input a1 to KEY3 b. Connect input a0 to KEY2 c. Connect input b1 to KEY1 d. Connect input b0 to KEY0 e. Connect selectors to the switches SW0 and SW1 f. Connect outputs to LEDs of your choice. 2. Extra credit: represent the state of pushbuttons and switches on neighboring LEDs. 3. Demonstrate the circuit to the TA 4. Experiment 4: 2-bit ALU and 7-segment display 4. Use circuits from experiments 3 and 1, and represent the result of 2-bit ALU on 7-segment display. POSTLAB REPORT: Include the following elements in the report document: Section 1 Element Theory of operation Include a brief description of every element and phenomenon that appears during the experiments. 2 3 4 5 Prelab report Results of the experiments Experiment Experiment Results a. Schematic of the circuit doing translation of BCD to 7-segment 1 b. Picture of the 7-segment displaying a number of your choice a. Schematic from Quartus 2 b. Simulation waveforms a. Schematic from Quartus 3 b. Simulation waveforms 4 a. Schematic from Quartus Answer the questions Question no. Question 1 Does Table 1. represent common anode or common cathode display? 2 Pick two simple ALU chips and list their most important functions. 3 What is LED? Conclusions Write down your conclusions, things learned, problems encountered during the lab and how they were solved, etc. 6 Attachments Zip your projects. Send through email as attachments, or provide link to the zip file on Google Drive / Dropbox, etc. List of attachments to deliver: 1. Quartus project for experiment 4 DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 6 CPE 100L LOGIC DESIGN I References: 1. DE0 pin table: http://faculty.unlv.edu/eelabs/docs/guides/DE0_Pin_Table.pdf 2. Altera DE0 Introduction / User Manual http://faculty.unlv.edu/eelabs/docs/guides/DE0_CV_User_Manual.pdf 3. Altera DE0 Computer System http://faculty.unlv.edu/eelabs/docs/guides/DE0_CV_Computer.pdf 4. Simulating Design in Quartus 13.1 http://faculty.unlv.edu/eelabs/docs/guides/Simulating_Design_in_Quartus_13_1.pdf 5. Datasheets of 7400 series chips: http://faculty.unlv.edu/eelabs/index.html?navi=main_icdatasheets DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING 7