ECE 85L Digital Logic Design Laboratory Fresno State, Lyles

advertisement

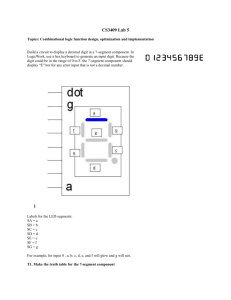

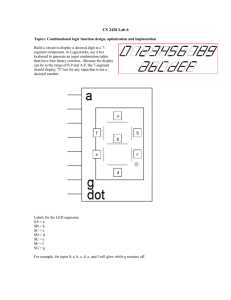

ECE 85L Digital Logic Design Laboratory Fresno State, Lyles College of Engineering Electrical and Computer Engineering Department Spring 2015 Laboratory 7 – Programmable Logic Device (PLD) BCD Design Problem 1. OBJECTIVES • Complete the design of a combinatorial 7-Segment Decoder from written specifications • Minimize the design equations using K-Maps • Implement the minimized functions using a Programmable Logic Device • Test, demonstrate, and document the resulting design • Integrate a 7447 IC BCD-to-Seven-Segment Decoder/Driver with a 7330 IC SevenSegment Display 2. DISCUSSION 2.1 7-Segment Displays A 7-Segment Display is used to display the decimal numbers 0-9 using a set of 7 Light Emitting Diode (LED) segments. The device usually accepts 7 inputs (a, b, c, d, e, f, and g), which select the corresponding segments to be illuminated on the display. An additional eighth LED is sometimes used to illuminate a decimal point. Figure 2.1 shows a typical seven-segment display. Figure 2.1: 7-Segment Display Page 1 of 10 7-segment displays are designed to be either Common Cathode (CC) or Common Anode (CA). In a common cathode display, all of the cathode connections from the LED segments are joined together and tied to Ground (0 V). Individual segments are therefore illuminated by applying a Logic HIGH (typically 5 V) to the inputs, which are directly connected to the anodes of the individual LEDs. In a common anode display, all of the anode connections from the LED segments are joined together and tied to Logic HIGH (again, typically 5 V). Individual segments are illuminated by applying a Logic LOW (Ground) to the inputs, which are directly connected to the cathodes of the individual LEDs. In general, common anode displays are more common because most logic circuits are able to sink more current than they can source. Figure 2.2 shows the internal connections for common cathode and common anode devices. Figure 2.2: Common Cathode and Common Anode 7-Segment Displays Figure 2.3 shows the segments that need to be illuminated to display decimal digits 0-9. Figure 2.3: Segments illuminated to display Decimal Digits 0-9 Finally, a BCD-to-7-Segment Decoder is a combinatorial circuit that decodes a 4-bit BCD input to the 7 outputs that can be used to drive the a-g LED segments on a 7-Segment Display, as appropriate. Page 2 of 10 2.2 Programmable Logic Devices (PLDs) In this laboratory, you will implement the entire BCD-to-7-Segment Decoder on a single Programmable Logic Device (PLD) chip. The process involves both software and hardware with the following general steps: 1. 2. 3. 4. 5. Develop Boolean Expressions for a Combinatorial Logic Design Develop Source Code to implement the Boolean Expressions with a PLD Compile the Source Code and Download the Compiled Program onto the PLD Test and Verify the Circuit Implementation on the PLD Modify the Design and Repeat the Steps, If Necessary The program to be used for Steps 2 and 3 (source code development and compilation) in this laboratory is called WINCUPL. A Block Diagram of a typical PLD is shown in Figure 2.4: Figure 2.4: Block Diagram of a PLD using AND-OR Logic for SOP Implementation The structure can be used to implement combinatorial Boolean Functions using Sum-ofProduct (SOP) expressions. The Inverters provide the Boolean Variables and their Complements. The AND gates generate the product terms, and the OR gate generates the SUM of the product terms – thereby creating the desired Boolean SOP Expression. The Programmable Array makes the required connections between the inputs and the Product Terms. As an example, the desired connections to implement the function: F = ABC* + A*BC Page 3 of 10 is shown in Figure 2.5. Figure 2.5: Interconnections on the Programmable Array Implement F = ABC* + A*BC Group P/C Lab Bench PC Device Programmer Figure 2.6: PDL Device Programmer Page 4 of 10 The PLD program (sometimes called a “fuse map”) makes the required connections. The PLD we will be using employs Electrically Erasable technology so the device may be reprogrammed or erased several times using a special Device Programmer, as shown in Figure 2.6. A general description of the development process follows. 1. On the computer at your lab station, create the source code in CUPL format in accordance with the tutorial ( e.g. DESIGN.PLD). 2. Compile the source code to produce the fuse map file (DESIGN.JED). 3. Place the fuse map file on an EEPROM and carry it to the burner. 4. Obtain the chip from the lab and carry it to the burner. 5. Open the burner’s program on the Lab Bench P/C, select the device (the PLD), and load the DESIGN.JED file into memory. 6. Download the file into the chip. 7. Remove the chip, insert it into your prototype board, and test. 3. PRELAB 3.1 WINCUPL Tutorial 1. Download and study the WINCUPL tutorial from the website, or examine it on one of the computers in the ECE 85L laboratory (the WINCUPL tutorial.doc in the WINCUPL folder on the Desktop). Pay particular attention to the development example (a 2-input OR Gate), along with the CUPL syntax. 3.2 BCD7-Segment Decoder Design 1. Derive the Truth Table for a 4-bit BCD to 7-Segment Decoder, assuming a Common Anode 7-Segment Display. Note that the BCD code words corresponding to the decimal numbers from 10 to 15 correspond to “Don’t Care” states. 2. Using Karnaugh maps, derive a set of Boolean equations that implement a Common Anode 7-Segment Decoder using only SOP expressions. 3.3 Mapping Boolean Equations to WINCUPL Format Page 5 of 10 1. Based upon the tutorial in Section 3.1 and your design in 3.2, map the Boolean Equations from your design into WINCUPL format. As described in the tutorial, pay close attention to the identifiers you use to make sure they are NOT WINCUPL reserved words. 2. Following the tutorial, create the source file for an ATMEL ATF750C PDL to implement your BCD-to-7-Segment Decoder. Use the following pinouts in Figure 3.1 to assign inputs and outputs. Make sure you do NOT use any of the restricted pins, such as Power, Ground, Clock. The IN designation on the device indicates that the pin may only be used as in Input, while the I/O designation indicates that the pin may be used for either input or output. Figure 3.1: Pin Assignment for the ATMEL ATF750C PLD 4. LAB ASSIGNMENT 4.1 Testing the PLD Process In this lab assignment, you will be given a compiled JEDEC file for the two-input OR gate. From the JEDEC file, you will complete the chip programming and testing. A source file called OR GATE.PLD has been placed in the CUPL folder on the desktop of each lab computer. This file is identical to that described in the tutorial. As review, open WINCUPL, load this file, and note the pin configuration (input and output pin assignments) which you will need later for testing. A compiled file called OR.JED also has been placed in the CUPL folder on the desktop of each lab computer. 1. Copy the OR.JED file to a USB, and carry it to one of the burner stations at the rear of the laboratory. Page 6 of 10 2. Obtain an ATMEL ATF750C PLD chip from the cabinet. The chip must be kept in an anti-static “pouch” to be carried to the Device Programming area and kept on its antistatic mat (the rectangular black mat to which the chip is housed) at your lab station when it is not being programmed. The PLD is quite sensitive to static electricity and should be kept on the mat as long as possible. When the chip is at the programming station, the student performing the programming must clip a ground band (connected to the programming computer’s ground) around the wrist of the arm holding the chip. When the chip is to be placed in the Programmer, attempt to hold the device by the two ends of the device that do NOT contain pins. The PLD should be placed in the Programmer with the pins oriented as shown on the icon on the Programmer (Pin 1 at the top left), and the chip located at the bottom of the socket. 3. Make sure the programmer (the “burner”) and the programming computer are ON, and open the program WELLON. The communications between the burner and the computer will be tested automatically. After a short period of time you should see a message indicating the successful connection test. DO NOT PROCEDE UNTIL THIS MESSAGE APPEARS. IF YOU CONTINUE TO GET AN ERROR MESSAGE CALL YOUR INSTRUCTOR. 4. From WELLON, select the device (the chip) Device > Select > ATMEL ATF750C > OK. 5. Load the chip into the burner as described in instruction 2 and close the socket clamp. 6. Insert the USB into the computer and load the file into the WELLON buffer. File > Load File > Select the File OR.JED and Enter. At this point the PLD should be programmed. 7. Open the socket clamp, remove the PLD from the burner, place it back on the antistatic mat and carry it to your lab computer station. 8. Insert (carefully!) the chip into the proto board, wire the chip and test the circuit. Demonstrate your working PLD circuit (an OR Gate) to your instructor. 4.2 7-Segment Decoder Design Implementation 1. Verify the source code you developed in Prelab for your 7-Segment Decoder design. a. Compile your program for the ATF750C. When it compiles cleanly (no errors or warnings), a fuse-map (JEDEC) file will be produced. Page 7 of 10 b. Copy your JEDEC file onto a USB and take it and your PLD to the device programmer. c. As you did in the Section 4.1, insert the PLD and program the device. 2. Examine the data sheet for a 7730 Common Anode 7-Segment Display. Determine how the outputs of your PLD 7-Segment Decoder circuit should be applied to the 7730 to implement your design. The input at Pin 14 on the 7730 is the common anode (CA) for all LED segments. A 47 Ω resistor should be placed in series between Pin 14 and Vcc to supply the proper current to the selected LED segments. Note: Other equivalent 7-segment display circuits may have differing anode terminals that require different resistor values. 3. Create a test environment on your protoboard using 4 switches to drive the 4-bit BCD inputs. Make careful connections to Vcc and GND – erroneous connections will most likely destroy the PLD and 7730 chips. a. Test your circuit, confirming that it matches your Truth Table. If not, you must return to Step 1 in Section 4.2. b. Observe and record the output that is displayed for all used (0-9) and unused (10-15) input combinations. c. Show your working circuit to your instructor. 4.3 7-Segment Display with the 7447 7-Segment Decoder 1. Replace your 7-Segment Decoder PLD implementation with a 7447 BCD-to-7Segment Decoder/Driver, as shown in Figure 4.1. The device has 4 inputs for the BCD input. Input D is the Most Significant Bit, descending down to Input A, which is the Least Significant Bit. Examine the data sheet for a 7447 IC for details. The 7447 outputs are active-low since they are connected to the LED’s cathode pins on each of the corresponding segments of the 7-segment display. The activelow Lamp Test (LT) input of a 7447 may be used to turn on all 7 segments to check if any are burnt out. The active-low Ripple-Blanking Input (RBI) is used to blank (turn off) the display if the BCD input is 0000. These functions may be disabled by tying them to Logic Level HIGH. The Blanking Input/Ripple-Blanking Output pin (BI/RBO) can be used as either input or output control. If a Logic Level LOW is applied to the pin, the display will be blanked, regardless of the BCD input value. Page 8 of 10 Figure 4.1: 7447 7-Segment Decoder with a 7730 7-Segment Display 2. Build and debug your circuit, using 4 switches to drive the 4-bit BCD inputs. Verify its operation with your Truth Table by measuring all input and output combinations. Does your measured Truth Table differ from that which you derived in Prelab? If so how? Also observe and record the output that is displayed for each of the six unused input combinations (10-15). 3. Demonstrate your working circuit to the Lab Instructor. 4.3 Extra Credit Modify your BCD-to-7-Segment Decoder design to implement a Hex-to-7-Segment Decoder for a Common Anode Display. See Figure 4.2 for details. Again, minimize the number of gates needed to implement your design. Page 9 of 10 Figure 4.2: 7-Segment Display used to display HEX values 0-F. 5. REVIEW QUESTIONS 1. Explain the difference between a Common Anode and Common Cathode display. 2. Explain why a straight set of SOP or POS Boolean Expressions does not necessarily minimize the gate count for a 7-Segment Decoder. 3. If you do not try to minimize the number of gates used, explain why a Common Cathode device naturally lends itself to a SOP implementation, while a Common Anode device lends itself to a POS implementation. Page 10 of 10