Linearized Di erential Transconductors in Subthreshold

advertisement

Linearized Dierential Transconductors in

Subthreshold CMOS

Paul M. Furth and Andreas G. Andreou

Department of Electrical and Computer Engineering

The Johns Hopkins University, Baltimore MD 21218, USA

(410)516-8361 (410)516-5566(FAX) furth@olympus.ece.jhu.edu

Indexing Terms - Transconductors, Subthreshold CMOS, Diusor.

Abstract

Three schemes for linearizing the transconductance of the basic dierential

pair in subthreshold CMOS are examined: 1) multiple asymmetric dierential

pairs, 2) source degeneration via symmetric diusors, and 3) source degeneration via a single diusor. Using a maximally at optimizing criterion, the linear

range of the basic dierential pair can be increased by four-to-eight times.

1 Introduction

Analog circuits implemented in subthreshold CMOS are attractive because they

consume little power and are compatible with standard CMOS processes [7, 4].

Continuous-time linear ltering of audio signals, for applications such as hearing

aids, is one class of analog circuits for which subthreshold CMOS poses a particular

challenge. The reason is that subthreshold current in a CMOS device depends exponentially on the gate voltage. Indeed, a model for the current in an NMOS device

operating below threshold is [7, 4, 1]

IDS = I0Se

VGB

Ut

VSB

(e, Ut , e,

1

VDB

Ut

)

(1)

where VGB is the gate to bulk voltage, VSB the source to bulk voltage, VDB the drain

to bulk voltage, S W=L the width to length ratio, I0 the zero-bias current, the

electrostatic coupling coecient between the gate and channel, and Ut kT=q the

thermal voltage. We ignore the eect of a nonzero drain conductance on IDS . If

VSB > VDB + 5Ut , the transistor is said to be in saturation.

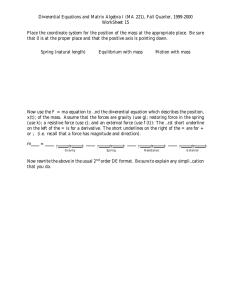

The basic dierential pair (Fig. 1(a)) consists of two matched transistors and a

current source Ib. Let the dierential input voltage VDM V1 ,V2, and the dierential

output current IDM I1 , I2. IDM can be written as

VDM (2)

IDM = Ib tanh 2U

t

Dene the transconductance of the dierential pair as G @IDM =@VDM . Normalize G by dividing by its maximum value Gmax. In this work, distortion is dened

as the largest deviation of the normalized transconductance from unity. Then the

linear range is the continuous set of values of VDM for which the distortion is equal

to a constant. For Ut = 25:7 mV, = 0:7, and 1% distortion, the linear range of the

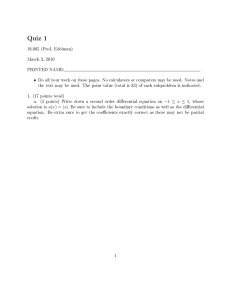

basic dierential pair is 14.7 mV. Fig. 2(a) plots normalized G as a function of VDM .

2 Three Linearization Techniques

I. A transconductor with two asymmetric dierential pairs is shown in Fig. 1(b).

The eect of unequal sizing of the transistor pairs is to create an intentional voltage

oset [5]. The total dierential current is given by

!

!

I

V

I

V

b

DM ln m

b

DM ln m

IDM = 2 tanh 2U + 2 + 2 tanh 2U , 2

(3)

t

t

The relative width-to-length ratio m of the transistor pairs is used to aect the shape

of the transconductance function.

Two possible criteria for optimizing the linear range are equiripple and maximal

atness [5]. Maximal atness is perhaps the best choice, since it provides for a more

robust design strategy against device mismatch. With one degree of freedom, the rst

nonzero derivative of G will be set to zero. Setting the second derivative equal to zero,

p

we nd that the only positive root that is greater than one occurs at m = 2 + 3,

independent of Ib, , and Ut. For the same parameter values as before, the linear

range is 58.4 mV, or approximately four times that of the basic dierential pair. In

Fig. 2(b) we plot normalized G as a function of VDM .

II. The diusor, proposed in [2], is discussed extensively in [1]. Fig. 1(c) shows a

dierential pair with source degeneration via symmetric diusors. The topology for

this circuit is derived from [3]. An equation for the dierential output current is

VDM

1

VDM ,

1

IDM = Ib tanh 2U , tanh 4m + 1 tanh 2U

(4)

t

t

Setting the second derivative of G equal to zero, we nd the only positive root occurs

at m = 0:5. For the same circuit conditions, the linear range is identical to that of

the transconductor with two asymmetric dierential pairs. A plot of normalized G is

given in Fig. 2(c).

III. A dierential pair with source degeneration via a single diusor is shown in

Fig. 1(d). The same circuit topology, as applied to above threshold CMOS, can be

found in [6]. The conductivity of the diusor is determined by the relative width-tolength ratio and the applied gate potential VGC . For simplicity, we assume that VGC

is exactly the average voltage of the input signals. An expression for IDM is

VDM 31

0

2

sinh

V

DM

2Ut

VDM 5A

(5)

IDM = Ib tanh @ 2U , tanh,1 4

t

2m + cosh 2Ut

Setting the second derivative equal to zero, the only positive root occurs at m = 0:25.

For the same circuits conditions, the linear range is 116.8 mV, or double the rst

two linearization schemes. Fig. 2(d) shows normalized G as a function of VDM . A

disadvantage of this linearizing technique is that it requires common-mode circuitry

to ensure that the input signals operate around VGC .

3 Experimental Results and Conclusions

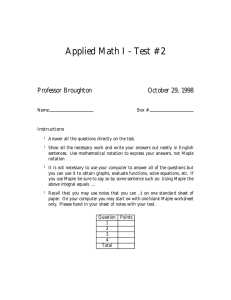

The transconductance functions of the basic dierential pair and the dierential pair

with a single diusor were measured using an SR850 lock-in. All transistors had

a width of 1377.6 m and length of 4.8 m. Chips were fabricated in a standard

1.2 m n-well process. We varied VGC at the gate of the diusor in Fig. 1(d) in

order to control its conductivity. Fig. 3 shows experimental data. The linear range of

the basic dierential pair is measured as 18.6 mV, while that of the transconductor

with a single diusor is 133.6 mV. The improvement in linear range is approximately

seven times, or roughly ten percent lower than that predicted. This discrepancy may

be attributed to such non-idealities as a nonzero drain-to-source conductance and

variations in .

Three linearizing techniques have been described, analyzed, and, optimized for use

in subthreshold CMOS circuit design. These linearizing schemes oer signicantly

higher linear range than the basic transconductor. The single diusor yields the

highest linear range (116.8 mV); however, it requires extra common-mode voltage

circuitry. The symmetric diusors and two asymmetric dierential pairs oer half

the linear range, but no common-mode circuitry is required. One useful property

of the subthreshold transconductors analyzed in this work is that optimal transistor

scaling is independent of the bias current.

This work was supported in part by NSF grant ECS-9313934.

References

[1] A.G. Andreou and K.A. Boahen. Neural information processing II. In M. Ismail

and T. Fiez, editors, Analog VLSI Signal and Information Processing. McGrawHill, 1994.

[2] K.A. Boahen and A.G. Andreou. A contrast sensitive silicon retina with reciprocal

synapses. In J.E. Moody, S.J. Hanson, and R.P Lippmann, editors, Advances in

Neural Information Processing Systems 4, pages 764{772. Morgan Kaufmann, San

Mateo, CA, 1992.

[3] F. Krummenacher and N. Joehl. A 4-MHz CMOS continuous-time lter with onchip automatic tuning. IEEE J. Solid-State Circuits, 23(3):750{758, June 1988.

[4] C.A. Mead. Analog VLSI and Neural Systems. Addison-Wesley, Reading, MA,

1989.

[5] H. Tanimoto, M. Koyama, and Y Yoshida. Realization of a 1-V active lter using

a linearization technique employing plurality of emitter-coupled pairs. IEEE J.

Solid-State Circuits, 26(7):937{945, July 1991.

[6] Y. Tsividis, A. Czarnul, and S.C. Fang. MOS transconductors and integrators

with high linearity. Electron. Lett., 22:245{246, February 1986. Errata, vol. 22,

p. 619, May, 1986.

[7] E.A. Vittoz. Micropower techniques. In J. Franca and Y.P. Tsividis, editors,

Design of MOS VLSI Circuits for Telecommunications and Signal Processing.

Prentice-Hall, 2nd edition, 1994.

I1

I2

V1

V2

1:1

I1

I2

V1

m:1

V2

1:m

Ib

0.5 Ib

0.5 Ib

(a)

(b)

I1

I2

I1

V1

1:m:m:1

V2

V1

I2

1:m:1

V2

VGC

0.5 Ib

0.5 Ib

(c)

0.5 Ib

0.5 Ib

(d)

Figure 1: (a) The basic dierential pair and three linearizing techniques: (b) two

asymmetric dierential pairs, (c) source degeneration via symmetric diusors, and

(d) source degeneration via a single diusor.

Normalized G

1

0.995

(a)

0.99

(b),(c)

(d)

0.985

0.98

-1.5

-1

-0.5

0

0.5

1

1.5

2

Vdm, Ut/kappa

Figure 2: Normalized transconductance as a function of VDM in units of Ut= for (a)

the basic dierential pair, (b) two asymmetric dierential pairs, (c) source degeneration via symmetric diusors (identical to (b)), and (d) source degeneration via a

single diusor.

G, Normalized to gm(0)

1

0.995

0.99

(a)

(b)

0.985

0.98

−75

−50

−25

0

Vdm, mV

25

50

75

Figure 3: Experimental data of the normalized transconductance as a function of VDM

for (a) the basic dierential pair and (b) the dierential pair with source degeneration

via a single diusor.