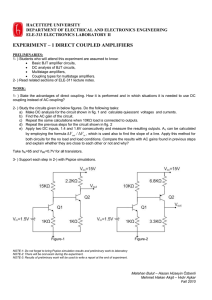

7. Differential and Multistage IC Amplifier

advertisement

7. Differential and Multistage IC Amplifier 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 1 7.1 Design Rules for Discrete and Integrated Circuits Discrete circuits: the elements are manufactured separately and are mounted on a printed circuit board. Integrated circuit: the elements and their interconnections are manufactured in a single semiconductor crystal. The elements in an integrated circuit and the interconnections are realized by applying of a sequence of processing steps like : photolithography, doping, diffusion. Strong restrictions about the values of the available elements in integrated circuit. See table 1. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 2 Components and practical values of discrete circuits compared with those for IC Discrete Circuits Integrated Circuits Resistors: • 1Ω .. 20MΩ; • Tolerances ±1% or ±5% • High power and low-temperature coefficient types available Capacitors • 1pF .. 0.1F; • Tolerances ±1% to ±20% • 0.1pF .. 100pF • Tolerances ±20%; good matching between C’s in a chip • Special types not available • Low-temperature coefficient types available Inductors • 10nH .. 1H • Tolerances ±1% to ±20% • 1nH .. 1µH; large area consuming • Tolerances: max few percents BJTs and FETs • Wide variety of types • Large unit-to-unit parameter variation 7. Differential and Multistage IC Amplifiers • 1Ω .. 100kΩ; • Tolerances ±30%; less than ±2% between R’s in a chip • Special types not available • Restricted types available • Good matching between devices in a chip TLT-8016 Basic Analog Circuits 2005/2006 3 Process Complexity Matching of Device Parameters Process: combination of steps for manufacturing of the IC. More processing steps increase the price of the IC but gives high-quality IC. Chip Area Very good matching between device parameters and characteristics in one chip. Relative variations not more that 2%. FETs Versus BJTs Small chip area ⇒ cheaper IC. BJT typically provide higher gain. Smallest chip area is consumed from the transistors. Largest area is consumed from inductors and capacitors. FET consume less chip area and static power dissipation is very small. BiCMOS process. Special circuit design is implemented, which avoids the capacitors and resistors. Inductors are used as exceptions – only in RF oscillators for GHz range. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 4 7.2 IC Biasing with BJTs The Current Mirror Figure 7.1 The current mirror. I C1 = I C 2 = vBE of Q1 = vBE of Q2. Thus I B1 = I B 2 (7.1) I C1 = I C 2 = β I B1 (7.2) I ref = I C1 + I B1 + I B 2 (7.3) 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits I ref 1+ 2 / β I C1 = I C 2 ≅ I ref I ref = VCC − VBE R 2005/2006 (7.4) (7.5) (7.6) 5 Compliance Range and Dynamic Output Resistance Figure 7.1 The current mirror. Compliance range: the range of the voltage in the flat part of the V-A characteristics of the current mirror, in which the current is approximately constant. Dynamic output resistance: ∂I ro = C 2 ∂VCE 2 7. Differential and Multistage IC Amplifiers −1 TLT-8016 Basic Analog Circuits (7.7) 2005/2006 6 An Example: Biasing of the Emitter Follower Figure 7.2 Emitter follower with bias current source. The high dynamic resistance of the current mirror gives high input impedance of the emitter follower. The major restriction for the input impedance comes the load resistance RLoad. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 7 Effects of the Transistor Area IC 2 = A2 I C1 A1 (7.8) Figure 7.4 Doubling the junction area of a BJT is equivalent to connecting two of the original BJTs in parallel. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 8 Exercise 7.2 Assuming identical npn transistors having equal areas, design a 1mA current mirror. The supply is VCC=15 V. Solution: I C ,Q1 = I C ,Q 2 = 1mA R1 = VCC − 0.7 15 − 0.7 = = 14.3kΩ −3 1× 10 I C ,Q1 Figure 7.13 Answer for Exercise 7.2. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 9 7.2 IC Biasing with FETs Figure 7.15 NMOS current mirror. 7. Differential and Multistage IC Amplifiers Figure 7.14 JFET as a current source. Since the device can operate with zero VGS, the fixed VGS is achieved by short connection between gate and source. TLT-8016 Basic Analog Circuits 2005/2006 10 7.4 Large-Signal Analysis of the Emitter-Coupled Differential Pair Basic Operation Differential and common mode input signals: vid = vi1 − vi 2 vicm 1 = (vi1 + vi 2 ) 2 vo1 = VCC − RC iC1 (7.23) vo 2 = VCC − RC iC 2 (7.24) vod = vo1 − vo 2 (7.25) vod = RC (iC 2 − iC1 ) (7.26) Figure 7.22 Basic BJT differential amplifier (emitter-coupled pair). 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 11 Operation with Pure Common-Mode Input Signal Because of the symmetry of the circuit, IEE splits equally between Q1 and Q2: iE1 = iE 2 = I EE / 2 iC1 = iC 2 = α I EE / 2 (7.27) (7.28) vod = RC (iC 2 − iC1 ) = 0 Figure 7.23 Basic BJT differential amplifier with waveforms. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 12 Operation with a Pure Differential Input Signal Pure differential signal: vi2 = -vi1. When vi1 > 0, vi2 < 0, thus iB1 increases and iB2 decreases. iC = β i B Thus iC1 increases and iC2 decreases. v o1 = VCC − iC 1 RC v o 2 = VCC − iC 2 RC Thus vo1 decreases and vo2 increases. v od = v o1 − v o 2 The amplitude of vod is doubled amplitude of vo1 and vo2. Figure 7.23 Basic BJT differential amplifier with waveforms. 7. Differential and Multistage IC Amplifiers Detailed small-signal analysis shows that the differential voltage gain of the emitter-coupled pair is equal to the voltage gain of a single CE amplifier having the same BJT and RC. TLT-8016 Basic Analog Circuits 2005/2006 13 The Large - Signal Transfer Characteristic iC 2 = iC1 = α I EE (7.44) α I EE (7.45) 1 + exp(vid / VT ) 1 + exp(− vid / VT ) Figure 7.25 Collector currents versus differential input voltage. 7. Differential and Multistage IC Amplifiers −v vod = α I EE RC tanh id 2VT (7.46) Figure 7.26 Voltage transfer characteristic of the BJT differential amplifier. Approximately linear dependence vod(vid) takes place for |vid| < VT (26mV). TLT-8016 Basic Analog Circuits 2005/2006 14 Emitter Degeneration Figure 7.27 Differential amplifier with emitter degeneration resistors. Figure 7.28 Voltage transfer characteristic with emitter degeneration resistors. REF = 40(VT/IEE). The amplifier is linear for |vid| < 20VT. Emitter degeneration improves the linearity but decreases the gain. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 15 Balanced Versus Single - Ended Output Figure 7.29 Either a balanced or single-ended output is available from the differential amplifier. Balanced output requires next stage to be differential too. Single ended output permits next stage to have a grounded input. The gain of the differential amplifier in this case is twice less. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 16 Common-Mode Rejection Ratio (CMRR) Accurate analysis shows that the differential emitter-coupled pair has small gain for the common-mode signal. CMRR = Avd r + (β + 1)(REF + 2 REB ) (7.69) = π Av cm rπ + (β + 1)REF Emitter degeneration worsens CMRR. If REF = 0, the common-emitter gain β improves CMRR. The dynamic resistance REB of the current mirror improves CMRR too and must be higher. rπ - from the small-signal equivalent circuit of the BJT; β - common-emitter current gain; REF – emitter degeneration resistors; REB – equivalent dynamic resistance of the current mirror. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 17 7.8 Examples of Multistage IC Amplifiers A BJT Op Amp Four stage dc coupled amplifier. 1st stage: differential pair with balanced output. High input impedance, high gain and high CMRR. 2nd stage: differential pair with single-ended output. Collector currents are 5 times more than in the 1st stage. Provides high output amplitude of the signal. 3rd stage: CE amplifier with pnp transistor. Small gain (~3.5). High linearity. It restores the dc level at its output to be approximately 0.7V. 4th stage: emitter follower. Buffer amplifier, no voltage gain. It provides low output impedance of the whole amplifier. Figure 7.55 A BJT op amp. 7. Differential and Multistage IC Amplifiers TLT-8016 Basic Analog Circuits 2005/2006 18