Optimization of Device Performance Using Semiconductor TCAD

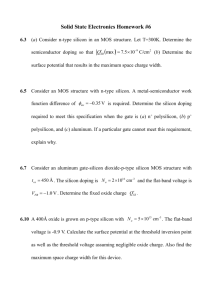

advertisement