elec2103c-electronic circuits and design

advertisement

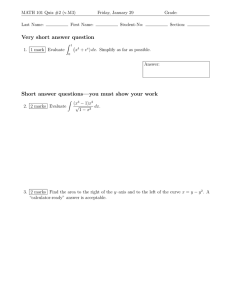

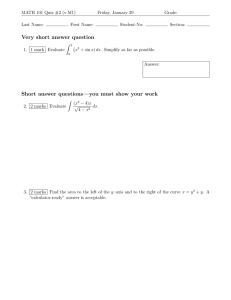

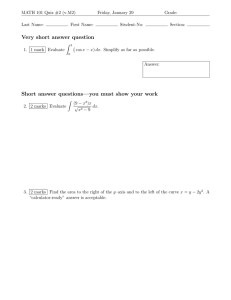

BEng. (Hons) Electronic Engineering Cohort: BEE/12/FT Examinations for 2013-2014/ Semester 2 MODULE: ELECTRONIC CIRCUITS AND DESIGN MODULE CODE: ELEC 2103C Duration: 3 Hours Instructions to Candidates: 1. Answer ALL 4 (four) questions. 2. Questions may be answered in any order but your answers must show the question number clearly. 3. Calculators are allowed 4. Always start a new question on a fresh page. 5. All questions carry equal marks. 6. Total marks 100. This question paper contains 4 questions and 10 pages. Page 1 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 ANSWER ALL 4 (FOUR) QUESTIONS QUESTION 1: (25 MARKS) a) The four stages of digital logic design are: design, synthesis, place and route, implement. i) Very briefly describe each of these stages. (4 marks) ii) What problem would occur if the “place and route” stage is wrongly tackled? (2 marks) b) Boolean algebra lie at the heart of logic designs and have a number of theorems that provide a valuable framework to deal with Boolean problems. The Factoring theorem is one of them and is given by: (X + Y) • (X' + Z) =X • Z + X' • Y i) By expanding the left hand side, prove the theorem. (4 marks) ii) How is the dual of a Boolean expression derived? (2 marks) iii) State the dual of the factoring theorem provided in i) (1 mark) c) Suppose a Boolean function F is given by F = A'B'C + A'BC + AB'C + ABC' + ABC P.T.O Page 2 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 i) Show that F can be minimized to F = AB + C using Boolean minimization. (3 marks) ii) Draw a truth table for F (2 marks) iii) From the truth table, write down the Product-of-Sum (PoS) form of P. (2 marks) iv) Assuming that the minimized PoS of F is given by F = (A + C)(B + C), what is the number of gates (exclude NOT gates) required to build each of the four expressions for F. What conclusion can be drawn? (4 + 1 marks) QUESTION 2: (25 MARKS) a) Since minimization of Boolean functions is an important element in the design of electronic systems, visual methods such as Boolean cubes and Karnaugh maps were invented. Consider the truth table of a full adder as shown below: A B Cin Cout 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 P.T.O Page 3 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 i) Draw a Boolean cube for the full adder, and hence minimize the function of the full adder (4 marks) ii) Draw a Karnaugh map for the full adder and verify the answer of i) (2 marks) b) Consider the diagram in Fig 2.1 which depicts a two-bit comparator. Fig 2.1: Two-bit comparator with A and C as most significant bits and B and D as least significant bit. i) Draw the truth table for the two-bit comparator (3 marks) ii) Use Karnaugh maps to minimize the expressions for LT, EQ and GT. (3 x 3 marks) c) Explain the following terms: Prime implicant, essential prime implicant. (2 marks) d) Use the principles of the essential prime implicants to find a minimum cover for the map of Fig 2.2: P.T.O Page 4 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 A X 1 0 1 C 0 1 1 1 D 0 X X 0 0 1 1 B 0 Fig 2.2: Karnaugh map for which minimum cover is to be found. (5 marks) QUESTION 3: (25 MARKS) a) VHDL is a hardware description language that can be used to program hardware. A very important principle behind the design process using VHDL is the use the black box approach. i) Briefly explain the black box approach and its advantages. (4 marks) ii) Briefly differentiate between the “entity” and the “architecture” in VHDL. (3 marks) b) Consider the VHDL code of Fig 3.1: P.T.O Page 5 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 entity my_circuit is Port ( A : in STD_LOGIC; B : in STD_LOGIC; C : in STD_LOGIC; F : out STD_LOGIC;) end my_circuit; architecture arch_circuit of my_circuit is signal D, E: std_logic; Begin A1<= (not A) and (not B) and C; A2<= B and C; F<= D or E; end arch_circuit; Fig 3.1: VHDL code of “my_circuit” i) There is one syntax error in the VHDL code of Fig 3.1. Identify it. (1 mark) ii) Draw a black box representation of the code. (2 marks) iii) The mode of signals D and E are not specified. Briefly explain why? (1 mark) iv) The architecture of a circuit can vary for the same entity. Write another architecture VHDL code lines for the circuit. (2 marks) c) Once a circuit has been designed using the ISE Webpack tool, two methods to test the design are: test bench and implementation. P.T.O Page 6 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 i) Which additional file is required when implementing the design in hardware? Briefly describe the function of this file. (1 + 2 marks) ii) Which additional file is required when testing the design in software using the Isim tool? Briefly describe the function of this file. (1 + 2 marks) d) Consider the code of Fig 3.2: Fig 3.2: VHDL code of a 4: 1 multiplexer. Assuming that the code of Fig 3.2 is to be implemented on a NEXYS 2 board (see Fig 3.3), write down the code for the additional file required for the “place and route” stage. You may assume that a typical line of code is usually of the form: NET "xx" LOC = "yy"; (6 marks) P.T.O Page 7 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 Fig 3.1: NEXYS 2 board schematic Fig 3.3: NEXYS 2 Board layout Page 8 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 QUESTION 4: (25 MARKS) a) Consider the circuit of Fig 4.1: Fig 4.1: SR Active high latch i) Draw the truth table of the above latch. (2 marks) ii) One problem with this latch is the race condition. Briefly explain. (2 marks) iii) By adding two AND gates in front of the latch of Fig 4.1, transform the latch into a gated latch with an enable line, such that when the enable line is activated, the circuit latches. Provide a drawing with your answer. (2 marks) iv) The circuit of iii) still have the race condition problem. By making an appropriate use of a NOT gate, transform the gated SR latch into a Dlatch. Draw the truth table of the resulting D-latch with the Enable line. (2 + 2 marks) P.T.O Page 9 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2 b) Consider the latch of Fig 4.2. Fig 4.2: D-latch with Enable line. i) By making use of two latches as shown in Fig 4.2, sketch the schematic of a positive-edge triggered D flip flop. (3 marks) ii) Briefly describe how the circuit sketched in i) will act as a positive-edge triggered D-flip flop? (3 marks) c) A J-K flip flop can be generated from a D-flip flop. i) Draw the truth table and state diagram for a J-K flip flop. (2 + 2 marks) ii) From the truth table, provide a minimized expression for Qnext in terms of Q, J, and K. Hence sketch the additional combinational circuit that needs to be added to the D flip flop to transform it to a J-K flip flop. (3 + 2 marks) ***END OF QUESTION PAPER*** Page 10 of 10 Electronic Circuits and Design (ELEC2103C) SITE/VK 2013-2014 S2