Small-Signal Analysis of a Differential Two-Stage Folded

http://dx.doi.org/10.5573/JSTS.2014.14.6.768 JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.6, DECEMBER, 2014

Small-Signal Analysis of a Differential Two-Stage

Folded-Cascode CMOS Op Amp

I.

I NTRODUCTION

Sang Dae Yu

Abstract—Using a simplified high-frequency smallsignal equivalent circuit model for BSIM3 MOSFET, the fully differential two-stage folded-cascode CMOS operational amplifier is analyzed to obtain its smallsignal voltage transfer function. As a result, the expressions for dc gain, five zero frequencies, five pole frequencies, unity-gain frequency, and phase margin are derived for op amp design using design equations. Then the analysis result is verified through the comparison with Spice simulations of both a high speed op amp and a low power op amp designed for the 0.13 μm CMOS process.

Index Terms—Differential two-stage folded-cascode

CMOS op amp, equation-based circuit design, high speed, low power, pole and zero frequency, smallsignal transfer function, frequency response, BSIM3.

Operational amplifiers have been used in a variety of analog circuits such as instrumentation amplifiers, continuous-time or switched-capacitor filters, analog-todigital or digital-to-analog converters, voltage regulators, and waveform generators. As a result, these op amps are essential analog circuit cells in many mixed-signal integrated circuits. In particular, the differential twostage folded-cascode op amp is needed to obtain high dc gain and wide output swing at low supply voltage in deep submicron technology [1]. For example, this op amp is

Manuscript received Jul. 3, 2014; accepted Sep. 14, 2014

School of Electronics Engineering, Kyungpook National University

1370 Sankyuk-dong, Buk-gu, Daegu 702-701, Korea

E-mail : sdyu@mail.knu.ac.kr used in high speed pipeline analog-to-digital converters and high frequency switched-capacitor filters [2-4].

Design of such high speed and high frequency complementary metal-oxide-semiconductor (CMOS) op amps becomes more critical in low power and low voltage circuits. In addition, transistor models have become more complex to characterize the physical behavior of submicron devices at high frequencies [5, 6].

Thus analog circuit design consumes a significant portion of total design time for mixed-signal integrated circuits.

So this is called analog design bottleneck. In order to enhance design productivity, various computer-aided design (CAD) approaches have been presented for op amp design or analog circuit design [7-14].

The small-signal design equations for dc gain, pole and zero frequencies, unity-gain frequency, and phase margin of op amps are required in manual design as well as equation-based and mixed CAD. So the pole and zero frequencies can be designed to achieve the stable transient response of operational amplifiers. Moreover, pole-zero doublets in the passband should be controlled through the design equations. Otherwise these doublets may seriously deteriorate the settling time. Such polezero control is an important advantage of equation-based design compared to simulation-based design. Thus it will be desirable that design equations of all op amps should be available. But in spite of the fact that the differential two-stage folded-cascode CMOS op amp is used in various analog circuits, its small signal design equations have not yet been derived analytically. In this paper, the transfer function of such an op amp will be analyzed to obtain its small-signal design equations. Then the analysis result will be verified through the comparison with Spice simulations of both a designed high speed

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.6, DECEMBER, 2014 769

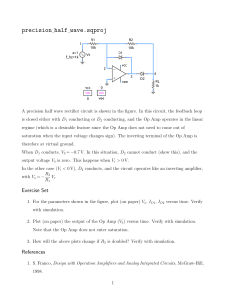

Fig. 1.

An MOSFET high-frequency small-signal equivalent circuit model with the complex transconductance g

* m

.

CMOS op amp with a unity-gain frequency of 576 MHz and a designed very low power CMOS op amp with a quiescent power dissipation of 2.5 μW.

II.

MOSFET S

MALL

-S

IGNAL

M

ODEL

Spice solves directly for small-signal voltages and currents using the large-signal equations of BSIM3. As a result, BSIM3 guarantees that the results from ac and transient simulation are entirely consistent because the two simulations use the same set of governing transistor equations. Naturally, there is no BSIM3 small-signal equivalent circuit model generated independently from the large-signal equations. But a small-signal circuit model of MOSFETs is needed to obtain the frequency responses of CMOS op amps for their design. A simplified high-frequency small-signal model shown in

Fig. 1 has been derived from the large-signal model used by BSIM3 [6]. It will be used in the small-signal analysis of the two-stage folded-cascode op amp circuit.

In this model, the complex transconductance or transadmittance is defined by g

* m

= g m

sC m

where the transcapacitance C m

is given by

( C dg

C gd

)

. Also

C dg

is defined by -¶ q d

/ ¶ v g which represents the effect of the gate voltage v g

on the charge q d associated with drain. On the other hand,

C gd

is defined by

-¶ q g

/ ¶ v d

which represents the effect of the drain voltage v d

on the gate charge q g

. If the drain and gate are the two terminals of a parallel-plate capacitor,

C dg

and

C gd

would have been equal like in the Meyer model. In general, these two transcapacitances are not the same. For example, consider a long-channel transistor in saturation. Because of pinchoff at the drain

Table 1.

Typical parameter values of an n MOS transistor with width 9 μm and length 0.49 μm for the 0.13 μm CMOS process

Parameter Strong Moderate Parameter Strong Moderate g m m m g mb m m

14.7 fF 1.5 fF m m C m

C gs

C gb

40.5 fF 8.5 fF

2.1 fF 7.2 fF g ds

C gd

C dg

5.0 fF

19.7 fF

4.6 fF

6.1 fF

C bs

10.5 fF 12.3 fF C bd

9.2 fF 10.1 fF end, the drain voltage will not affect the gate charge.

Thus

C gd

will be zero. However, the gate voltage will greatly affect the inversion charge associated with the drain charge q d

. Thus C dg

will have a large value. As a result,

C dg

is always greater or equal to

C gd

under all operating regions, and then C m

will be greatest in the saturation region [5, 6].

Finally, the capacitances of five physical capacitors shown in the small-signal model should include extrinsic capacitances like overlap or junction capacitances. In the small-signal analysis, each capacitor is treated as an ordinary circuit element with the given capacitance.

Usually Spice reports these total capacitances at a bias point in the operating point printout. For the IBM 0.13

μm CMOS process, typical small-signal parameters of an n MOS transistor operating in the strong or moderate inversion region are given in Table 1.

III.

S

MALL

-S

IGNAL

A

NALYSIS

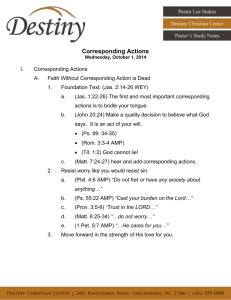

In this section, we analyze and verify the small-signal operation of a fully differential two-stage folded-cascode

CMOS op amp to determine its voltage gain in response to the input voltage. Fig. 2 shows this operational amplifier fed by a differential input signal V i

that is applied in a complementary or balanced manner [1-4].

That is, the gate of M

1

is increased by V i +

= + V i

/ 2 and the gate of M

2

is decreased by V i -

= V i

/ 2 . To enhance gain with body effect, the body terminals of

M

6

and M

7

are connected to the power supply V

DD

, whereas those terminals of M

8

and M

9

to the power supply V

SS

. Because of the circuit symmetry and balanced driving, a signal ground as a sort of virtual

770 SANG DAE YU : SMALL-SIGNAL ANALYSIS OF A DIFFERENTIAL TWO-STAGE FOLDED-CASCODE CMOS OP AMP

Fig. 2.

A fully differential two-stage folded-cascode CMOS op amp with common-mode feedback circuit model and node numbers.

Fig. 3.

A high frequency equivalent circuit for the differential half circuit of the two-stage folded-cascode CMOS op amp.

(1)

( ) =

( g m 1

sC dg 1

) ( g

21

sC m 6

) g

33

+ (

3

C m 8

) { g m 13

+ s C c

( g m 13

R c

1 ) C dg 13

s C dg 13

R C c

}

(2) ground is established at the source terminals of the input differential pair. As a result, the output conductance of the current source M

3

will have no effect on the small signal operation. Thus a differential half circuit of the op amp can be obtained by excluding M

3

for differential signal operation. Fig. 3 shows the equivalent half circuit.

Here V n

is the voltage of node n and the differential input voltage is given by V i

º ( V i +

V i -

) . In addition, the capacitances C

1

, C

2

, C

3

, and C

4

represent the total node capacitances at the drains of M

1

, M

6

, M

10

, and M

13

respectively. From this half circuit, the differential voltage gain of the op amp can be determined directly [15, 16]. The nodal equations for this circuit can be written in a matrix form as (1). The conductances g jk

and capacitances

C jk

used in this equation are defined in Table 2 using the transconductance g mi

, body transconductance g mbi

, output conductance g dsi

, transcapacitance C mi

, parasitic capacitances C gbi

,

C gsi

,

C gdi

, C bsi

, and C bdi

of each transistor M i

, and the load capacitance C

L

at each output node. In order to reduce the number of nodal equations, sC

24

has been used as an equivalent admittance between node 2 and node 4.

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.6, DECEMBER, 2014 771

Table 2.

Definition of each conductance and capacitance used in the Eq. (1) for the equivalent small-signal half circuit g

11

º g ds 1

+ g ds 4

+ g

21

, g

22

º g ds 6

+ g ds 8 g

21

º g m 6

+ g mb 6

+ g ds 6

, g

23

º g m 8

+ g mb 8

+ g

33

º g ds 10

+ g

23

,

C

11

º C

1

+ C gd 1

C m 6

, C

24 g

44

º g ds 13

+ g ds 15

º C gd 13

+ C c

/ (1 + g ds 8

)

C

1

= C gs 6

C

2

= C bd 6

+ C bs 6

+ C gd 6

+ C bd 1

+ C bd 4

+ C bd 8

+ C gd 8

+ C gd 4

+ C gs 13

+ C gb 13

C

3

= C gs 8

+ C bs 8

+ C gd 10

+ C bd 10

C

4

= C

L

+ C bd 13

+ C gd 15

+ C bd 15

Using the output voltage V

4

of the equivalent half circuit, the differential output voltage of the op amp can be expressed as V o

º V o +

V o -

= 2 V

4

. Therefore, the differential voltage gain A d

º V o

/ V i

can be written as a rational fraction

A d

( ) º = A

0

Õ

5 i = 1

( 1 + s /

Õ

5 i = 1

(

1 + s / w zi w pi

)

)

(3) where A

0 is the dc gain, w zi is the frequency of zero z i

, and w pi is the frequency of pole p i

. From symbolic analysis for the circuit Eq. (1), the numerator can be exactly obtained as a factored form like (2).

Assuming that and

(1 + +

2

2

) ; (1 + b s )(1 + /

1

) c

( m 13

R c

1 ) ?

C dg 13

, the numerator polynomial can be approximately factored as

( ) ; g m g g m g

æ

1

è

sC dg 1 g m 1

÷

ø

ö æ

÷ ç

è

1 sC m 6 g

21

ö

÷

ø

ê

ë

é

1 +

(

3

C m 8 g

33

ê

ë

é

1 -

( g sR C dg m 13

R c

13

1)

ù

ú

é

ê 1

û ë

+ sC c

( g m 13

R c

1 ) ù

ú g m 13

) ù

ú

(4)

The denominator of the differential voltage gain A d consists of 226 terms and is given by a fifth-order polynomial

( ) = a

0

+ a s + a s

2

+ a s

3

+ a s

4

+ a s

5

(5) where the coefficient a

0 can be arranged as a

0

= g

44

ë

11 ds 8 g ds 10

+ g g ds 6

( g ds 1

+ g ds 4

)

û

(6)

As a result, the dc gain A

0

º A d

(0) can be found as

A

0

= g m g g m g a

0

= g m g g m 13 where output conductance of the first stage is given by

(7) g o 1

= g ds 8 g ds 10 g

33

+ g ds 6

( g ds 1

+ g

11 g ds 4

)

(8)

In general, the coefficient a

1

is related to the opencircuit time constants and the frequencies of poles as follows [17].

a

1 a

0

º a

11

+ a

12

+ L + a

15 a

0

=

5 5 i

å

= 1

R C i

=

å

i = 1

1 w pi

(9)

Typically op amps are designed so as to have a dominant pole p

1

. Hence its frequency w p 1

is much smaller than all other pole frequencies. In the two-stage op amp, this pole is realized by a large compensation capacitance C c

.

As a result, the dominant pole will be related to opencircuit time constants ( a

11

/ a

0

) associated with C c

.

The terms a

11

usually consist of the largest term with

C c

and additional terms. Among 25 terms of a

1

, the candidates for these terms a

11

can be arranged as

(1 + g R c

) g g ds 8 g ds 10

+ g

33

( g ds 1

+ g ds 4

) g ds 6

C c

+ g g ( g m 13

+ g

44

)( C c

+ C gd 13

)

(10) where the largest term is ( g g g m 13

C c

) . The other additional terms for the dominant pole can be found from the terms of (10) by insight for circuit and process of trial and error. As a result, the final major terms a

11

are found as a

11

; g g ( g m 13

+ g

44

)( C c

+ C gd 13

)

(11)

Thus the dominant pole frequency is approximated as

772 SANG DAE YU : SMALL-SIGNAL ANALYSIS OF A DIFFERENTIAL TWO-STAGE FOLDED-CASCODE CMOS OP AMP a

5

= C C

11

( C

3

C m 8

)

4

(

2

+ C gd 13

) + C gd 13

( C

2

C m 13

) R c

; C C

11

( C

3

C m 8

) (

C

4

+ C gd 13

) c

(13) w p 1

= a

0 a

11

;

( g m 13

+ g

44

)( C c

+ C gd 13

)

(12)

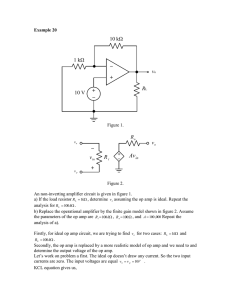

For a two-stage folded-cascode op amp designed for the IBM 0.13 μm CMOS process, the comparison between a transfer function with the dominant pole and

Spice simulation is shown in Fig. 4. It can be seen that

(12) is an accurate model of the dominant pole and that the nondominant poles are needed to reduce the phase difference at the unity-gain frequency f t

. Because the phase margin is a critical performance in reducing power dissipation, accurate estimation of the phase at f t

is quite important in low power op amp design.

The nondominant poles can be found by factoring the coefficient a

5

with 8 terms that are obtained from the symbolic analysis of (1). Assuming that C

2

is sufficiently greater than C gd 13

and C m 13

, the factored form of a

5

can be obtained as (13). Here the factors

( C

4

+ C gd 13

) C

2

have been approximated from the factor

ë 4

(

2

+ C gd 13

) + C gd 13

( C

2

C m 13

) . If we compare coefficients between the denominator of (3) and (5), it follows that

5 i

Õ

w

= 1 pi

= ( a

0

/ a

5

) . Thus the product of all nondominant pole frequencies can be written as

Fig. 4.

Comparison between a dominant-pole transfer function model A = A

0

/ (1 + s / w p 1

) and Spice simulation for a high speed CMOS op amp with a unity-gain frequency of 576 MHz. p 2 p 3 p p 5

= a

0 w p a

= a

11 a

5

; g g ( g m 13

+ g

44

)( C c

+ C gd 13

)

C C

11

( C

3

C m 8

) ( C

4

+ C gd 13

)

2 c

(14)

When C

2

is not sufficiently greater than

C gd 13

and

C m 13

, the above approximation makes slight differences between model and simulation in high frequency region.

But such differences can be reduced by using factors

( C

4

+ C gd 13

)( C

2

+ C gd 13

)

. Therefore, the denominator polynomial of the voltage gain can be expressed as

D ; a

0

æ

1 +

è s w p 1

ö é

1 +

( g m 13

+

(

4

+ C gd 13

) g

44

)(1 + C gd 13

/ C c

)

ù

ú

û

(15) where the last factor is exactly equal to the third factor of the numerator. These factors may give rise to a pole-zero doublet. If this doublet is in the passband, it may cause severe degradation of settling time while only causing minor changes in the frequency response [18]. Besides, the doublet near the unity-gain frequency w t

may give rise to errors in estimating w t

and the phase margin. To enhance stability and accuracy, it is desirable to impose a design constraint w p 5

> w t

.

The unity-gain frequency of the two-stage foldedcascode op amp is an implicit nonposynomial [19]. Using

A d

( j w t

) º 1 and t

/ p 1

?

1, the unity-gain frequency can be modeled as w t

= A

0 w p 1

H ( w t

) º k t g m 1

C c

H ( w t

) º

Õ

5 i = 1

é

ë

Õ

5 i = 2

é

ë

+ w t

/ w zi

)

2 ù

û

+ w t

/ w pi

)

2 ù

û

(16)

(17) where k t

is a modeling parameter. Since this design equation is nonlinear and nonposynomial for w t

, it

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.6, DECEMBER, 2014 773 should be solved or designed iteratively. In Fig. 4, f t was found by iteration. In such an iterative design process, k t

can be considered as an updating parameter.

The phase margin of the op amp is also a complicate nonposynomial. Using arctan( )

; x for x < 0.5

, the phase margin PM can be approximately obtained from

PM 90 °

;

180 ° w t p

é

ê i

5

å

= 1 w

1 zi

-

5

å i = 2

1 w pi

ú

û

ù

(18)

Here it can be seen that a right-half-plane (RHP) zero with negative frequency w zi

gives rise to decrease in

PM like a left-half-plane pole with positive frequency.

Small PM leads to excessive gain peaking in the closedloop frequency response and undesirable ringing in the step response. As a result, the RHP zero will cause degradation of op amp stability. On the contrary, a lefthalf-plane zero increases the phase margin.

IV.

D ESIGN AND V ERIFICATION

In this section, the transfer function will be compared with Spice simulations of the two op amps designed by sequential geometric programming. Table 3 shows the design specifications of op amp 1 and 2. To enlarge the performance difference between two op amps, the op amp 1 was designed as a high speed op amp while the op amp 2 was designed as a low power op amp. In general, because op amp design is a nonlinear optimization problem, we have to solve it using an iterative approach.

This is naturally compatible with updating parameters.

Typically the design equations consist of the transistor parameters. Thus the nonposynomial parameters and equations are updated through modeling parameters from operating point simulation [11]. In this respect, the used design paradigm can be called a mixed approach utilizing both bias simulations and design equations. Finally, it takes 46 and 17 iterations to design the op amp 1 and op amp 2 respectively.

The basic specifications for op amp design are the constraints on dc gain, unity-gain frequency, and phase margin. In addition to these signal constraints, bias constraints should be imposed to ensure that all transistors remain in saturation for the input commonmode voltage v

CM and output voltage v

O

. These

Table 3. Design constraints and objective of the two-stage folded-cascode CMOS op amp 1 and 2 for the 0.13 μm process

Performance

A

0

(dB)

Specification for op amp 1

³ 60

Specification for op amp 2

³ 70 f t

(MHz)

PM ( ° )

CMR (V)

OS (V)

SR (V/ μs)

P

D

(mW)

³ 570

³ 60

0.1 / 0.7

0.3 / 0.3

³ 500

£ 0.85

³ 4.8

³ 60

0.1 / 0.7

0.3 / 0.3

³ 1

£ 2.5 10

3 minimize minimize Area ( μm )

Power supply = ± 0.6 V, C c

= 0.15 pF, C

L

= 0.2 pF constraints are expressed by the common-mode range

(CMR) and output swing (OS). The lower and upper limits of CMR and OS are given by v

CM min

= V

SS

+ V ov 3

+ V ov 1

+ V t 1

(19) v

CM max

= V

DD

V ov 5

+ V t 1 v

O min

= V

SS

+ V ov 15

(20)

(21) v

O max

= V

DD

V ov 13

(22)

To operate properly for the circuit connection obtaining the unity-gain amplifier, there must be a substantial overlap between the allowable ranges of v

CM

and v

O

. For maximum output swing, the three bias voltages shown in Fig. 2 can be expressed as

V

B 5

= V ov 5

V t 5

V

B 7

= V

DD

V ov 5

V ov 7

V t 7

V

B 9

= V

SS

+ V ov 11

+ V ov 9

+ V t 9

(23)

(24)

(25)

The slew rate taking into account C

L

can be obtained as

SR = min

æ

ç

è

I

D 3

,

I

C c

D 15

-

C

L

I

D 3

The active area of the op amp is written as

ö

÷

ø

(26)

Area = a R c

+ a C c

+

16

å

(27) i = 1 and the quiescent power dissipation is given by

774 SANG DAE YU : SMALL-SIGNAL ANALYSIS OF A DIFFERENTIAL TWO-STAGE FOLDED-CASCODE CMOS OP AMP

Fig. 5.

Comparision of the transfer function model to Spice simulation for high speed op amp 1. Mark ‘x’ indicates a pole frequency, ‘o’ a zero frequency, and ‘z’ a pole-zero doublet.

P

D

= ( V

DD

+ V

SS

) é

ë

I

B

+ 2

(

V

D 5

+ I

D 13

) ù

û

(28)

In order to get the op amp operating in strong inversion, a bias constraint for the overdrive voltage

V ov

³ V ov min

was imposed on each transistor of the op amp 1. For this high speed op amp, the comparison between the transfer function and Spice simulation is shown in Fig. 5. Because the small-signal model is valid up to about 10 GHz, the frequency is driven to that frequency. Although a pole and three zeros exceed the frequency limit of validity, their marks were indicated to show the relative positions of the pole and zeros. This op amp with C

L

of 0.2 pF dissipates a quiescent power of

0.82 mW at supply voltages ± 0.6

V and has a unitygain frequency of 576 MHz. It can be seen that the Eqs.

(3), (4), and (15) is an accurate model for the transfer function of the op amp in which all transistors are operating in strong inversion.

Finally, Fig. 6 shows the comparison between the transfer function and Spice simulation for the op amp 2 in which all transistors are operating in moderate inversion. In order to realize this operation, a special constraint for channel width

W ≥ 0.65 μm was imposed on two transistors M

4

and

M

5

. This op amp has a unity-gain frequency of 4.8 MHz but operates with a very low power dissipation of 2.5 μW. It can be also seen that the derived transfer function is a good model even for the op amp operating in moderate inversion.

For these two-stage folded-cascode op amps, the values of

P

D

, f t

, PM, dc gain, pole and zero frequencies are shown in Table 4.

Fig. 6.

Comparision of the transfer function model to Spice simulation for low power op amp 2 with dissipation of 2.5 μW.

Table 4.

Values of power dissipation, unity-gain frequency, phase margin, dc gain, pole frequencies, and zero frequencies for high speed and low power 2-stage folded-cascode op amps

Performances, poles, and zeros

Power dissipation P

D

Op amp 1 Op amp 2

0.82 mW 2.5

m W

Unity-gain frequency f t

Phase margin PM

576 MHz 4.8 MHz

60.0

o

89.6

o

A

0

= g m g g m 13

60.7 dB 69.5 dB w p 1

=

( g m 13

+ g

44

)( C c

+ C gd 13

) w p 2

=

( g m 13

+ g

44

)(1 + C gd 13

/ C c

)

C

4

+ C gd 13 w p 3

= g

11

C

11

1 w p 4

=

R C

2 w p 5

= g

33

C

3

C m 8 w z 1

=

( g m 13 g m 13

R c

1) C c w z 2

= g m 1

C dg 1 w z 3

= g m 13

R c

1

R C

13 w z 4

= w p 5 w z 5

= g

21

C m 6

556 kHz 1.61 kHz

1.3 GHz 11 MHz

1.9 GHz 236 MHz

4.1 GHz 356 MHz

19 GHz 295 MHz

1.2 GHz 10.2 MHz

–6.2 GHz –2.1 GHz

–18 GHz –3.4 GHz

19 GHz 295 MHz

–34 GHz –9.8 GHz

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.14, NO.6, DECEMBER, 2014 775

V.

C ONCLUSIONS

Using a high-frequency small-signal equivalent circuit with the complex transconductance, the fully differential two-stage folded-cascode CMOS operational amplifier was analyzed to obtain its small signal transfer function.

As a result, the expressions for dc gain, five zero frequencies, five pole frequencies, unity-gain frequency, and phase margin were derived for op amp design using design equations. From comparing with Spice analysis, the good agreement between the transfer function model and simulation result has been observed for two op amps operating in either moderate or strong inversion. Thus the proposed transfer function could be usefully used in accurately designing the differential two-stage foldedcascode CMOS operational amplifiers.

A

R EFERENCES

CKNOWLEDGMENTS

This study was supported by the BK21 Plus project funded by the Ministry of Education, Korea. (21A20131600011)

[1] R. Castro-López, O. Guerra, E. Roca, and F. V.

[2] H. Ishii, K. Tanabe, and T. Iida, “A 1.0 V 40 mW

[3] J. Shen and P. R. Kinget, “A 0.5-V 8-bit 10-MS/s

[4]

[5]

Fernández, “An integrated layout-synthesis approach for analog ICs,”

Aided Design of Integr. Circuits and Syst.

, vol. 27, pp. 1179–1189, July 2008.

10 b 100 MS/s Pipeline ADC in 90 nm CMOS,”

Proc. of the IEEE Custom Integrated Circuits

Conference , pp. 395–398, Sep. 2005.

Pipelined ADC in 90-nm CMOS,” IEEE J. Solid-

State Circuits , vol. 43, pp. 787–795, April 2008.

S. Xiao, J. Silva, U.-K. Moon, and G. Temes, “A tunable duty-cycle-controlled

University Press, 2011.

IEEE Trans. Computerswitched-R-

MOSFET-C CMOS filter for low-voltage and highlinearity applications,” Proceedings of 2004 IEEE

International Symposium on Circuits and Systems , pp. I-433–I-436, May 2004.

Y. Tsividis and C. McAndrew, Operation and

Modeling of the MOS Transistor . Oxford

[6] W. Liu, MOSFET Models for SPICE Simulation,

Including BSIM3v3 and BSIM4 . John Wiley &

Sons, 2001.

[7] G. G. E. Gielen and R. A. Rutenbar, “Computeraided design of analog and mixed-signal integrated circuits,” Proceedings of The IEEE , vol. 88, pp.

1825–1852, Dec. 2000.

[8] G. G. E. Gielen, “CAD tools for embedded analogue circuits in mixed-signal integrated systems on chip,” IEE Proc. Comput. Digit. Tech.

, vol. 152, pp. 317–332, May 2005.

[9] M. M. Hershenson, S. P. Boyd, and T. H. Lee,

“Optimal design of a CMOS op amp via geometric programming,” IEEE Trans. Computer-Aided

Design of Integrated Circuits and Systems , vol. 20, pp. 1–21, Jan. 2001.

[10] P. Mandal and V. Visvanathan, “CMOS op-amp sizing using a geometric programming formulation,”

IEEE Trans. Computer-Aided Design of Integrated

Circuits and Systems , vol. 20, pp. 22–38, Jan. 2001.

[11] S. D. Yu, “Design of CMOS op amps using adaptive modeling of transistor parameters,”

Journal of Semiconductor Technology and Science , vol. 12, pp. 75–87, March 2012.

[12] A. K. Singh, K. Ragab, M. Lok, C. Caramanis, and

M. Orshansky, “Predictable equation-based analog optimization based on explicit capture of modeling error statistics,” IEEE Trans. Computer-Aided

Design of Integr. Circuits and Syst.

, vol. 31, pp.

1485–1498, Oct. 2012.

[13] X. Li, P. Gopalakrishnan, Y. Xu, and L. T. Pileggi,

“Robust analog/RF circuit design with projectionbased performance modeling,” IEEE Trans.

Computer-Aided Design of Integrated Circuits and

Systems , vol. 26, pp. 2–15, Jan. 2007.

[14] W. Daems, G. Gielen, and W. Sansen, “Simulationbased generation of posynomial performance models for the sizing of analog integrated circuits,”

IEEE Trans. Computer-Aided Design of Integrated

Circuits and Systems , vol. 22, pp. 517–534, May

2003.

[15] A. S. Sedra and K. C. Smith, Microelectronic

Circuits . Oxford University Press, 2011.

[16] S. M. Mallya and J. H. Nevin, “Design procedures for a fully differential folded-cascode CMOS operational amplifier,” IEEE J. Solid-State Circuits , vol. 24, pp. 1737–1740, Dec. 1989.

[17] P. E. Gray and C. L. Searle, Electronic Principles .

776 SANG DAE YU : SMALL-SIGNAL ANALYSIS OF A DIFFERENTIAL TWO-STAGE FOLDED-CASCODE CMOS OP AMP

John Wiley & Sons, 1969.

[18] B. Y. Kamath, R. G. Meyer, and P. R. Gray,

“Relationship between frequency response and settling time of operational amplifiers,” IEEE J.

Solid-State Circuits , vol. 9, pp. 347–352, Dec. 1974.

[19] R. J. Duffin, E. L. Peterson, and C. Zener,

Geometric Programming—Theory and Application .

New York: Wiley, 1967.

Sang Dae Yu was born in Ulsan,

South Korea on February 12, 1958.

He received the B.S. degree in electronics engineering from Kyung- pook National University, Korea in

1980, and the M.S. degree and the

Ph.D. degree in electrical engineering from Korea Advanced Institute of Science and

Technology in 1982 and 1998, respectively. Since 1982, he has been with the School of Electronics Engineering,

Kyungpook National University, Korea, where he is currently a Professor. His current interests include integrated circuit design, computer aided design, semiconductor device modeling, surface acoustic wave devices, and embedded Linux systems. Prof. Yu is a member of the Institute of Electronics and Information

Engineers of Korea and the Korean Sensors Society.