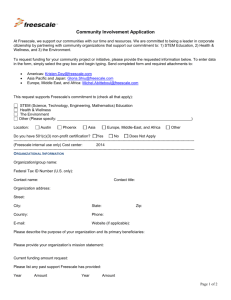

Hardware Techniques - PCB Design

advertisement

November 2010

AMF-IND-T1119

Introductory Class on EMC/EFT with a

Focus on Susceptibility

Michael Steffen

Senior Field Applications Engineer – EMC Expert

TM

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

How good is your susceptibility?

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

1

GOFSL

G – Ground and Power Planes

► O – Oscillator layout

► F – Filtering

► S – Software Techniques

► L – LUCKY!!!!!!!

►

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

2

Who am I?

Freescale Field Apps Engineer 8-bit / Sensor Specialist

EMC/EFT Specialist

Appliance EMC Expert 12+ years

Design Engineer 10+ Years in Applicance and Customer

MCU applications

► EMC Global Swat Team Member

► Published

► Authored Several Application Notes

► Consulted / Troubleshoot EMC designs for many MAJOR

appliance companies

►

►

►

►

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

3

Agenda

►EMC

Overview

►Standards and Test Methods

►System Design Best Practices

•

•

•

•

•

•

Review theory

Guidelines

Hardware design methodology

Customer examples

Software best practices

References

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

4

EMC/EFT Overview

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks

of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007.

What is EMC?

►

Electromagnetic Compatibility (EMC) Definition

“ Ability of an electronic system/device to function satisfactorily in an

electromagnetic environment without introducing intolerable

electromagnetic disturbances to anything in that environment ”

• Every system that generates, consumes, modifies, or processes

electrical power/signals generates electromagnetic emissions and is

susceptible to electromagnetic disturbance.

•

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

6

Basic EMC Categories

►

Four basic EMC categories, combinations of:

•

•

Radiated (air)/Conducted (physical medium)

Emissions (out)/Susceptibility (in)

►

Components of an EMC issue

•

•

•

Source (a perpetrator)

Medium

Receiver (a victim)

Noisy

component

Noisy

component

Conducted Emissions

Radiated Emissions

Potentially

susceptible

component

Potentially

susceptible

component

Conducted Susceptibility

Radiated Susceptibility

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

7

What does FSL do to enable customers to meet EMC

standards?

►

Incorporate design methods

•

►

To minimize emissions, strengthen immunity in MCU’s we supply

Test EMC on MCU’s

Capture data for customer communications

• Insure certain minimum criteria achieved

•

Respond to EMC questions/issues from applications using FSL

MCU’s

► Participate in EMC standards committees

►

Improve existing standards

• Extend standards to Integrated Circuits

•

►

Communicate EMC basics and best practices

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

8

Specifications and Testing

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks

of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007.

IEC IC Conducted Transient Immunity EMC Measurement Methods

►IEC

61000-4-4 Fast Transient Conducted

Immunity

• True 61000-4-4 System Level Testing

• EFT, Langer Probe

• EFT, FSL Probe

EFT, Mains Injection

EFT, Langer Probe

EFT, FSL Probe

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

10

Fast Transient Testing – IEC 61000-4-4 EFT

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

11

Electrical Fast Transient (EFT) Testing – IEC 61000-4-5 Surge Test

•

•

•

•

•

Power System Switching transients (e.g., capacitor banks switching)

Load Changes

Resonating circuits associated with switching devices such as thyristors

System Faults (e.g., shorts, arcing faults to ground)

Lightning strikes (direct, indirect, or direct to earth)

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

12

Fast Transient Testing – IEC 61000-4-12 Ringwave

Trise = 0.5uS

Oscillation Frequency = 100kHz

Generator Voltage to 4kV

1-60 Transients / Minute

The ring wave is a typical oscillatory transient, induced in low-voltage

cables due to the switching of electrical networks and reactive loads,

faults and insulation breakdown of power supply circuits or lightning.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

13

Langer Diagnostic Probe

IMPROPER

USE

|

B

-

B=

µo |

4ΩR2

∫

wL

-

-

-

- ++++++++ - -

-

-

-

|

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

14

Langer Diagnostic Probe

Induced Voltage as Function of Area - Circular Loops

70

60

Induced Voltage

50

10% Output

30% Output

40

40% Output

30

50% Output

90% Output

20

10

6.

86

70

4.

16

31

1.

06

.0

3

20

95

.5

4

78

.6

2

63

.2

7

50

.2

7

.6

3

.4

8

38

28

19

.5

7

12

7.

07

0

Test Loop Area (m m ^2)

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

15

Creative

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

16

Next Generation Fast Transient Test?

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

17

System Design and Best Practices

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks

of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007.

GOFSL

G – Ground and Power Planes

► O – Oscillator layout

► F – Filtering

► S – Software Techniques

► L – LUCKY!!!!!!!

►

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

19

Theory

Electromagnetic theory is well understood

► The problem is that not everyone understands it

► So, a quick review of Maxwell’s equations…

►

wikipedia.org

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

20

Guidelines

Todd Hubing, Clemson U

•

•

•

•

•

Use common sense

Visualize signal current paths

Locate antennas and crosstalk paths

Be aware of potential EMI sources

Ask other engineers to review your designs

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

21

Hardware Techniques – Design Methodology

► Goals

• Attenuate transients to prevent performance

degradation or reliability issues.

• Maximize use of hardware techniques before using

software techniques.

► Design for EMC should be considered from

the beginning of a project.

► Design for EMC is a complex task

•

•

•

System Power & Signal Entry

System Connectors

& Cable Routing

System & PCB

Power Supply

PCB Floorplan

Use a methodical strategy

Be prepared for many iterations

Employ experts, if necessary

PCB Power Distribution

PCB Decoupling & Filtering

► Design for EMC compliance

• Do not limit design to maintain a cost target

• The design can be cost-reduced later

► Success requires attention to detail and

MCU Oscillator

Input Filtering & Protection

close coordination with other disciplines.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

Iteration Start

Iteration Complete

TM

22

Hardware Techniques – Design Methodology

►Tools

•

for application transient immunity

Block transient currents

The goal is to limit transient currents.

Series impedance

Physical isolation

•

Resistors

Inductors

Ferrites

CM chokes

Shunt transient currents

The goal is to limit transient voltages.

Parallel conductance

Physical shielding

Capacitors

Varistors

Zener Diodes

TVS Devices

•

Make IC insensitive to transients

The goal is to minimize voltage differences between any pins of the IC and

the reference (typically VSS) during and shortly after a transient event.

Ideally, keep ∆(VDD-VSS) and ∆(VI/O-VSS) less than 8V. Using external

Zener or TVS clamp might help. Keep ∆|VSS-VSSA| less than 0.3V

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

23

Hardware Techniques – System Design

►Power Entry Filtering

• First opportunity to eliminate conducted

transients.

• Unfiltered power

•

Radiated

Conducted

Allows unimpeded access to the system.

Requires complex solutions for PCB and cables.

PCB1

Power entry filtering at point of entry .

PCB2

No Filter – Conducted immunity signal

propagates to PCB1 and radiates to

couple to PCB2 and interior cables.

Reduces complexity of system design.

PCB design and layout are less critical.

Cable routing is less critical.

Improves radiated and conducted emissions

performance.

PCB2

Conducted

Filter

PCB1

Filtered – Conducted immunity signal

suppressed. Clean power supplied to

PCB1 and no internal radiation.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

24

Hardware Techniques - PCB Design

►PCB Power Distribution

• The basis for effective EMC design.

• Layout guidance

Ground (reference)

–

–

–

–

–

Power

–

–

Route parallel to ground on same or adjacent layers.

Use wide traces (or planes).

Data

–

–

•

Prioritize ground routes over all other routes.

Do not use wire jumpers and minimize layer transitions.

Where layer transitions occur, use multiple vias.

Use planes (or wide traces).

Minimize impedance between VSS pin and clock source, decoupling, bypassing

and filtering components. Use a plane where possible.

Lowest priority for routing.

Use wire jumpers and vias for connectivity.

Decouple regulated and filtered power routed off the PCB (to sensors,

displays, etc).

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

25

Hardware Techniques - PCB Design

►Bypassing

• Definition

•

Bypassing is the reduction of HF current flow in a

high impedance path by shunting that path with a

bypass component, typically a capacitor.

Purpose

Bypassing prevents unwanted communications

between different components (or different power

domains) that share the same power rail. This

effect is called common-impedance coupling.

Bypassing provides a local source of charge to limit

voltage variations on the power and ground rails.

Bypassing improves noise margins and stability.

•

VDD

0.1uF

Minimal

Loop

MCU

VSS

Criteria

The capacitance must be sufficient to provide the

needed

transient current to the load.

The impedance between the bypass and the load

must be very low.

The loop area of the layout must be as small as

possible.

Caps need to be located close to micro to be

effective

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

Bypass capacitor is

between supply and load

– effective HF shunt

TM

26

Hardware Techniques - PCB Design

►Decoupling

•

Definition

•

Decoupling is the isolation of two circuits on a common power supply to

prevent the transmission of noise between the two circuits using a

combination of blocks, and optionally shunts, typically in the form of a low

pass filter.

Purpose

Decoupling prevents unwanted communications between different

components (or different power domains) that share the same power rail.

This effect is called common-impedance coupling.

Decoupling provides increased isolation over bypassing.

Decoupling improves noise margins and stability.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

27

Hardware Techniques - PCB Design

►Decoupling

•

Implementation

Place the decoupling circuit at the entry point of the power domain to be

filtered.

Decoupling is not always used.

–

There is always some decoupling built into any circuit.

–

•

Decoupling is typically used as a last resort if bypassing fails

to give the wanted power-supply isolation.

Conductors act as decoupling inductors. Although short trace lengths are

desirable, the power lead being long can sometimes help improve decoupling.

Examples:

VDD

Note: Bulk cap

needed on each

side of decoupling

element.

VDD_ISO

Unfiltered

DC Input

VDD

7805

VDD_ISO

Filtered

DC Output

VSS

VSS_ISO

Generic decoupling filter

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

VSS

VSS

Voltage regulator

TM

28

Hardware Techniques - PCB Design

►Inputs

See recommendations in AN2764

• Place filter cap as close to MCU as possible, referenced to a solid MCU

ground.

•

10kΩ

VDD

VDD

1kΩ

Input

RESET/IRQ

100nF

100nF

VSS

MCU

VSS

MCU

►High

Speed/Programming Pins – 10k pullup if suspected noise on

this line, no caps.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

29

Hardware Techniques - PCB Design

•

•

•

•

Relay

MCU

Relay

Power

Supply

Outputs

Inputs

Outputs

EMI

Filter

Relay

Floorplan example

Inputs

►

Analog

Sensors

Identify element function and power domain.

Group PCB elements by power domain.

Decouple and bypass power domains.

Filter inputs and outputs.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

30

Hardware Techniques - PCB Design

►Route

Power connections

EMI

Filter

Power

Supply

Domain

Digital DC Power

Domain

DF

Outputs

BP

Analog

BP

Relay

Relay

Relay

AC Power Domain

DF Analog DC Power

BP

MCU

Sensors

LPF

LPF

Outputs

Inputs

Inputs Inputs

•

Ground and Power first

DF : Decoupling filter [Typically L = 100uH-100mH, C = 1uF-100uF.]

BP : Bypass capacitor [Typically 0.1uF connected between power/ground pins.]

LPF : Low-pass filter [Typically R = 1kΩ

Ω , C = 100nF (10nF for fast signals).]

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

31

Hardware Techniques - PCB Design

Then route I/O

•

I/O connections

EMI

Filter

Power

Supply

Domain

Digital DC Power

Domain

DF

Outputs

BP

Analog

BP

Relay

Relay

Relay

AC Power Domain

DF Analog DC Power

BP

MCU

Sensors

LPF

LPF

Outputs

Inputs

Inputs Inputs

►

DF : Decoupling filter [Typically L = 100uH-100mH, C = 1uF-100uF.]

BP : Bypass capacitor [Typically 0.1uF connected between power/ground pins.]

LPF : Low-pass filter [Typically R = 1kΩ

Ω , C = 100nF (10nF for fast signals).]

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

32

Hardware Techniques - PCB Design

►

Floorplan example

Analog

inputs

Isolation – series

impedance

Power supply

& EMI filter

Filter

components

close to MCU

MCU &

Digital I/O

Relays

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

33

Hardware Techniques - PCB Design

►Oscillator

•

EMC characteristics of clock sources

Clock Source

Advantages

Disadvantages

Ceramic Resonator

Lower cost

Sensitive to EMI, humidity and vibration.

Drive circuit matching.

Crystal

Low cost

Sensitive to EMI, humidity and vibration.

Drive circuit matching.

Crystal Oscillator Module

Insensitive to EMI and humidity. No

additional components or matching

issues.

High cost. High power consumption.

Large size. Sensitive to vibration.

RC Oscillator

Lowest cost.

Sensitive to EMI, humidity and vibration.

Poor temperature and supply voltage

rejection. Poor freq control & accuracy.

Silicon Oscillator

(INTERNAL OSCILLATOR)

Insensitive to EMI, humidity, and

vibration. Fast startup. Small size. No

additional components or matching

issues.

Temperature sensitivity generally worse

than crystal and ceramic resonator.

Some have high power consumption.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

34

Hardware Techniques - PCB Design

►Oscillator

•

Configuration

Use higher frequency signal source (4MHz vs. 32kHz crystal) for immunity

Use high-gain oscillator option for immunity

Use low power oscillator option for emissions

Use internal oscillator, if possible.

•

Layout

Highest layout priority after power distribution system and MCU decoupling.

Implementation must be controlled to prevent susceptibility.

–

–

–

–

–

Group components tightly

Locate next to oscillator pins

Use short traces

Surround with guard trace

Isolate from other I/O

Do not route functional currents using oscillator reference GND.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

35

Hardware Techniques – GOOD PCB Design

VDD is on bottom

layer to show

multiple via layer

transition.

Parallel

VDD and

GND Traces

BEST LAYOUT – 2 LAYER, TOP AND BOTTOM

MOUNT COMPONENTS

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

Hardware Techniques – BEST PCB Design

VDD is on bottom

layer to show

multiple via layer

transition.

LAYERS:

Red – Top

Green – Bottom

Orange – TOP/Bottom

GND

(PLANE)

VCC

BEST LAYOUT – 2 LAYER, TOP AND BOTTOM

MOUNT COMPONENTS

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

Ground Planes

Find the ground plane

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

38

Software Techniques

►Overview

The structure and functionality of microcontroller software can have a

profound impact of transient immunity performance.

• Failure modes

•

False Signal Detection – The MCU detects a change in an input signal that

was induced by a transient or other noise. The MCU then operates on or

responds to the signal as if it were real.

Code Runaway – The MCU software execution flow is disrupted. The MCU

begins to execute code out of sequence or from incorrect areas of memory.

The impact on software is managed through defensive software design.

Software does not eliminate the transient or noise. It can only attempt

to control the MCU response to the transient or noise.

• Long-term issues due to exposure to transients remain.

•

•

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

39

Defensive Software Contents

►Digital Input Pins

►Interrupt Pins

►Unused Pins

►Critical I/O Registers

►Program Flow

►Token Passing

►Frequency of Interrupts (too few, too

►Code Runaway – Watchdogs

►CPU Clock

►Watchdog Reset Timeout Test

►CRC check on Flash Integrity

►Unused Program Memory locations

►RAM Testing

►Unused Interrupt Vectors

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

many)

TM

40

Digital Input Pins

►In

the majority of all MCU’s the digital input pins are

accessed generally by a parallel read by the CPU via it’s

data bus. This access is normally captured on the edge

of the CPU system clock. Thus if a spurious glitch

occurs at exactly the time of reading the actual digital

port pin then a false state can occur.

►To overcome this spurious error condition, the user can

deploy a “polling” technique where the digital input pin is

read several times within a short time period and the

dominant average value is taken as the true level.

►In the majority of cases the CPU/System clock will be

working at a significantly higher frequency than the

expected external input signals. If this is not the case

and the external input signal can change multiple states

withing a CPU clock period, then hardware latching or

sample and hold circuits would be required to ensure a

state condition is not missed out.

Port x1

System clock

CPU Read

1!

Result (no polling)

1!

CPU Read

1!

Result (polling)

Read_portA_bit0 ()

{

Char True_read =0;

for (char count = 6; count!=0 ; count--)

{ unfiltered_read = porta

If (unfiltered_read&&0x01) true_read++; /* mask off all bits except bit 0

};

If (true_read > 2) return (1) ;

Else return(0);

}

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

1"

0!

1!

Polling

TM

41

Interrupt Pins

►In many MCUs external pins have interrupt capability

and in most cases will interrupt the CPU on a specific

rising or falling edge. To avoid a spurious noise glitch

being seen as a rogue interrupt, users should always

read the input signal pin to confirm that the input signal

has maintained it’s assertive state (eg if the PA0 pin

interrupts the CPU on a negative edge the ISR first

instruction should read the PA0 pin and if clear then

execute the interrupts subroutine, if set then take this as

a rogue interrupt.) Note: in most cases the ISR will take

several CPU clocks cycles after the input event has

occurred providing a delay. Depending on the

environment and the system design software delays can

also be implemented to act a sort of de-bounce circuit.

►For pins that have no “read access” deploying a

redundant digital input pin can provide this read after

event mechanism.

►In some cases the interrupt function may provide the

option of “edge & level sensitive”. In most cases the

hardware will still react to a rogue edge, as the edge&

level sensitive feature really provides an additional

interrupt if the input pin is held asserted after the ISR has

completed.

Port x1

System clock

CPU access

Lower priority code(lpc)

ISR

lpc

lpc

Interrupt latency

Verify read

Identifies bogus interrupt

Back to main program

Verify pin state using BIL BIH for IRQ, READ GPIO for KBI, ETC

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

42

Unused pins

►In some cases not all the input or I/O pins will be used

the MCU in the end application. Unused Input Only pins

need to be tied to either VDD or VSS. A floating high

impedance input pin will oscillate and provide an easier

coupling path into the MCU circuits for noise, and

additionally will consumer more current. ( If MCU in

STOP mode is consuming more current than expected

max. this indicates a floating input pin or pins)

►Unused I/O pins should be made outputs and drive a

logic state out. Software can regularly update the Data

and DDR to ensure the pin remains an output.

►Users of MCUs should also consider the package they

are using of the particular MCU as the multiple packages

are often served with the same silicon die, and on

smaller pinout versions some input/output pins are not

bonded out. Thus, the user must force these unused

input/output pads to output a static level.

►For non-bonded input pins, the MCU manufacturer

should have deployed a pull-up or pull-down device to

ensure these are not left floating. This might be

programmable via a special control register.

NC

PA6

PA7

Input only – pull up or pull down

Not used (NC) – output low

Not bonded – output low

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

43

Critical I/O Registers

►Critical

•

•

•

•

•

I/O Registers such as

Input/Output Data Ports

Data Direction Registers

Clock/PLL Set-up registers

Peripheral Set-up registers

User defined RAM locations – key parameters of the

application code.

►All

Refresh - safely

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

registers when you dig deep enough into the

design are basically flip flop latches that may be

flipped by a spurious noise passes through the

circuit.

►User software should regularly refresh the above

critical registers, within the main loop of the software,

to correct a possible flip of bit.

►For RAM locations where the variables are

dynamic, then utilizing a CRC signature of the array

of these locations can be saved and regularly

checked and verified. MCUs with hardware CRC

engines help provide a workable solutions. For

MCUs with no hardware CRC engine, executing

CRC in software will likely cost too much in execution

time.

►Avoid updating registers on peripherals that are in

mid operation (eg a transmitting SCI) or

corruption/loss of data will occur.

TM

44

Program Flow

Program flow check.

Program flow check.

CPU Access

Appl code

Appl code

Appl code

Appl code

Appl code

Periodic interrupt

Time-slot monitoring; a periodic check on program code flow

►Program flow

of the various software functions is a key requirement to ensure System Integrity.

Watchdog circuits provide hardware protection if program flow does not follow as expected, but are

generally should be deployed as the last chance mechanism.

►A

key measure to ensure correct Program flow is known as “time-slot monitoring”. Time-slot

monitoring describes the method of periodically checking the current status of where the program

counter is and is it performing as expected.

►For

example: Using a simple timer overflow interrupt set at ~100mS will interrupt the CPU and the

TOF ISR will be executed. Within this ISR the user can use a form of Token passing to 1) check

program flow and 2) check other interrupt usage.

Periodic status checks

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

45

Token Passing

►A

F{11}

F{12}

F{13}

Check

flow

COUNTBYTE=0x13;

COUNTBYTE=0x12;

COUNTBYTE=0x11;

simple form of token passing is that you

deploy a variable in RAM called COUNTBYTE

and for each significant function you increment

this COUNTBYTE by 1.

►On the knowledge of how long the program

takes to execute these various functions then the

COUNTBYTE can be read within the ISR, and

compared to previous captured value and if

within certain range will deem the program flow

to running as expected. If outwith this range then

program is performing not as expected and

mechanisms to reset or place the MCU in a safe

mode can be made.

►Caution: within each software function it is not

recommended that you increment the

COUNTBYTE by a certain value, but actually set

the COUNTBYTE to a fixed value.

►On real time embedded systems interrupts can

occur at any random time and therefore are more

difficult to monitor along with the program flow as

described above. Therefore only the frequency

of interrupts can be monitored then checked

within the same periodic ISR routine.

….

If (COUNTBYTE < (previousCOUNTBYTE+2)) Error;

If (COUNTBYTE > (previousCOUNTBYTE+6)) Error;

/* prrogram flow OK */

previousCOUNTBYTE = COUNTBYTE;

…..

Only proceed if conditions are as expected

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

46

Code Runaway - Watchdogs

►The

above two methods describe

methods to identify early warnings that

the application is not performing as

expected. In some cases interrupts could

be masked, and the program counter is

corrupted and gets caught in a small tight

loop that does not allow the unmasking

of the interrupts.

CPU access

Refresh

mechanism

clock

Counter

Reset on

overflow

basic watchdog

If CPU does not execute the

unique refresh mechanism before

counter times out then a reset to

the CPU and all peripherals occurs.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

►At

this point the use of a watchdog is

required to protect against this scenario.

►The

majority of MCUs have on-board

watchdogs that can be enabled to protect

against this scenario. Additionally the

user should test that the watchdog circuit

times out correctly and performs a reset

before executing the code

TM

47

Watchdog Reset Timeout Test

Detect POR (System Reset Reg.)

Enable WDOG

Write to wdog_tst_flag in RAM

reset

Read other timer value

Application code

CPU access

►Before

executing any application code the watchdog

should be tested it is functioning correctly.

►Some

MCUs have a System Reset Status Register

that allows the user to determine the cause of the reset.

On recognizing a Power on reset, the user can write a

specific word(16 or 32bits) to RAM location

(wdog_test_flag). After this the watchdog is enabled(if

not already ) another timer enabled, and then the

software sits in a small loop which reads the other

timer’s count value and stores it to another RAM

location. Eventually the watchdog will time out and

reset. The user code sees that the reset occurred due

to a WDOG timeout (from the System Reset Status

Register) so confirms if this is a test of the WDOG or a

genuine WDOG reset by reading wdog_test_flag. If it is

a WDOG test, we know the WDOG has timed out and

reset the MCU as expected, but we need to compare

with the captured other timer count value to ascertain if

the time-out period is within the expected range. If this

compares ok then the wdog has been tested and

application code can now be executed.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

Read Timer Counter value

Store in RAM

Detect WDOG reset (System Reset Reg.)

Quantify if WDOG test

Compare WDOG timeout with

expected Timer Counter value in RAM

Test the Watchdog

TM

48

CPU Clock

►

The CPU clock is generally sourced from

•

•

►

►

Internal RC oscillator, then multiplied( PLL/FLL) to higher frequency

External Crystal/Ceramic Resonator, then PLL/FLL to higher frequency

Most peripherals are clocked by the same source as CPU.

Thus if CPU clock stops for a particular reason

•

•

•

No interrupts will be requested

No peripherals will be clocked

No software will be executing.

► If

no CPU clock occurs in real time application then software cannot

overcome this issue.

► Thus a watchdog circuit using an alternative clock source will still

timeout and reset the key peripherals without CPU clock.

► User

watchdogs with independent clock source from CPU clock.

Clock Monitor

LOL, LOC

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

Watchdog with separate clock

TM

49

CRC check on Flash Integrity

►Verifying the

Start_addr

If Start_addr

< End_addr

N

Y

Main

Flash

Array

Update_CRC (char)* Start_addr

Start_addr ++

End_addr

System_error()

CRC_HI

CRC_LO

Update_CRC (char) *Start_addr

N

Compare

CRC_16==CRC_HI/LO

Y

golden_signature

Flash OK

memory is functioning correctly prior to executing

application code is recommended. For non-volatile memory such as

Flash or EEPROM then a CRC signature is a good approach in

providing a high diagnostic coverage.

►There are various different CRC signatures, and a common one is

CCITT-CRC16. This well understood polynomial equation that is

easily executed in both hardware and software. A software CRC

engine will take around 700-1000 CPU cycles to calculate a

modified CRC on the addition of 1 byte of data. ( a h/w CRC engine

will take 1 CPU cycle).

►The approach: Once the application code is completed and

working reliably and no changes are anticpated, then a CRC

signature is made of the total “used” memory array.

►Once this signature is completed, it is stored in another unused

nvm space, and referred to as the “golden_signature”.

►After reset the user code will execute a new CRC calculation on

the total “used” memory array then compare the new calculated

signature with the golden_signature. If it compares ok then the

memory and arguably the addressing mechanism are working

correctly.

►Note: In IEC 61508 CRC signature of NVM memory is taken to be

a more stringent measure than Error Code Correction (parity

checking) in hardware. This is because the CRC signature is

generally carried prior to executing application code, thus

identifying a fault before running with wrong code/data.

CRC engine complying to

CRC16-CCITT specification.

(x16 + x12 + x5 + 1 polynomial)

Better than checksum

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

50

Unused Program Memory

►If

there are unused memory locations in the NVM arrays it is

a good idea to fill these locations with instructions such as

SWI (software interrupt) thus on a runaway condition and the

program counter points to unused location it will force an

interrupt, which can then put the MCU and the application into

a safe state.

►If there is no Software Interrupt then by examining the

assembly code for JUMP(extended address) instruction and

the NOP instruction should be examined, and with careful

consideration you can fill the unused array with “jump to a

safe_location”.

►Eg. On the S08 CPU the JMP instruction is 0xCC, NOP is

0x9D. So if at address $9D9D we can place code that places

the MCU in a safe condition, then we can fill the array with

►CC,9D,9D,CC,9D,9D, CC,9D,9D, CC,9D,9D, CC,9D,9D,

CC,9D,9D, etc

►Thus if the Program Counter falls in any location it will either

execute a JMP instruction to $9D9D or a NOP, followed by

JMP $9D9D or NOP,NOP,JMP $9D9D.

►In most CPUs there are instruction op-codes that will do

minimal effect and allow the runaway program counter to go

to a known safe place.

►It should be noted that you should avoid filling the arrays

with NOPs, as this will provide further randomness to how the

MCU will perform.(unless the top of the unused array falls into

a usable array) If the program counter jumps to somewhere in

the unused array

►it will execute all the NOP instructions to the top then

execute possible what is in the next address location (could

be I/O register or an interrupt vector contents).

Unused Program Space

Addr

$E000

$E001

$E002

$E003

$E004

$E005

…….

Code

0x9D

0x9D

0xCC

0x9D

0x9D

0xCC

Instruction

NOP

NOP

JMP

If PC jumps into anywhere in

“unused program space” It will

execute a few NOP instructions

then jump to a safe_start

function.

$9D9D JMP Safe_start

• Block fill w/ SWI

• SWI ISR – force reset

• Jump to Safe_start

• Block fill w/ illegal opcode

• forces reset

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

51

Unused Interrupt Vectors

Unused interrupt vectors

should be programmed to point

to an individual ISR that will

ensure the MCU is placed into a

safe known state, as most

interrupts will require a clearing

mechanism.

►No interrupt vector location

should be left blank.

►

Void interrupt ISR_spare()

Void interrupt ISR_spare()

{ Void interrupt ISR_spare()

{

/*{called from unused vector */

/* called from unused vector */

Safe_mode();

/* called from unused vector */

Safe_mode();

} Safe_mode();

}

}

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

Each ISR clears respective flag

TM

52

Software Techniques

►Digital

•

or Analog Inputs

Boundary checking

Using the input capture function of a Timer module to measure the time

duration of the signal.

The captured value can be compared to the expected value.

The software can then react appropriately.

Example:

–

–

–

►Analog

•

Input signal specification requires a pulse width of 1ms to 10ms.

Input capture measures an input pulse width of 50ns, such as from an ESD

event. Input pulse is bad data.

Input capture measures an input pulse width of 5ms. Input pulse is good data.

Inputs

For ADC inputs, actively monitor converted values or apply averaging.

►For

other inputs, options vary by module functionality.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

53

Software Techniques

►Integrated Protection

•

•

Features

Enable all available built-in protection features.

Initialization

Enable hardware protection during software initialization.

–

–

Typically done by writing a configuration register.

These configuration bits are often “write once”.

Be sure to write these bits even if the default states are not changed. This

prevents accidentally disabling protection due to code runaway.

Disable hardware functions that are not used.

•

Low voltage detect (LVD) circuits

Resets the MCU in the event of sudden power loss.

Can be used to prevent code runaway.

May not detect very fast transients due to slow response time.

Operate at lower voltages than external voltage supervisor chips.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

54

Conclusions

►

►

►

►

►

►

Achieving transient immunity in low-cost applications can be

difficult and time-consuming, particularly if not addressed early

and often.

Employ a rigorous EMC design methodology.

Obtain the needed EMC expertise.

Leverage information from suppliers.

Understand the limits of “low cost”.

Save cost reduction for after EMC compliance is achieved.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

55

References

► Ronald

B. Standler, Protection of Electronic Circuits from Overvoltages,

John Wiley & Sons, 1989

► Ken Kundert, “Power Supply Noise Reduction”, The Designer’s Guide

(www.designers-guide.com), 2004

► Larry D. Smith, “Decoupling Capacitor Calculations for CMOS Circuits”,

Electrical Performance of Electrical Packages Conference, Monterey CA,

November 1994

► Clayton Paul, Introduction to Electromagnetic Compatibility, Wiley & Sons,

1992

► Bernard Keiser, Principles of Electromagnetic Compatibility, Artech House,

1987

► Howard Johnson, Martin Graham, High-Speed Digital Design, Prentice

Hall, 1993

► Ralph Morrison, Grounding and Shielding, John Wiley & Sons, 2007

► Freescale Semiconductor application note AN2764, “Improving the

Transient Immunity Performance of Microcontroller-Based Applications”,

www.freescale.com, 2005

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

56

High Speed Design Reading List

► Right

the First Time- A Practical Handbook on High Speed PCB and

System Design - Volumes I & II - Lee W. Ritchey (Speeding Edge)

- ISBN 0-9741936-0-7

► High Speed Digital System Design - A handbook of Interconnect

Theory and Practice - Hall, Hall and McCall (Wiley Interscience

2000) - ISBN 0-36090-2

► High Speed Digital Design- A Handbook of Black Magic - Howard

W. Johnson & Martin Graham (Prentice Hall) - ISBN 0-13-395724-1

► High Speed Signal Propagation- Advanced Black Magic - Howard W.

Johnson & Martin Graham - (Prentice Hall) - ISBN 0-13-084408-X

► Signal Integrity Simplified - Eric Bogatin (Prentice Hall) - ISBN 0-13066946-6

► Signal Integrity Issues and Printed Circuit Design - Doug Brooks

(Prentice Hall) - ISBN 0-13-141884-X

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

57

EMI Reading List

► PCB

Design for Real-World EMI Control - Bruce R. Archambeault

(Kluwer Academic Publishers Group) - ISBN 1-4020-7130-2

► Digital Design for Interference Specifications- A Practical Handbook

for EMI Suppression - David L. Terrell & R. Kenneth Keenan

(Newnes Publishing) - ISBN 0-7506-7282-X

► Noise Reduction Techniques in Electronic Systems - Henry Ott

(2nd Edition - John Wiley and Sons) - ISBN 0-471-85068-3

► Electromagnetic Compatibility Engineering – Henry Ott (John Wiley

and Sons) – ISBN 0-470-18930-6

► Introduction to Electromagnetic Compatibility - Clayton R. Paul

(John Wiley and Sons) - ISBN 0-471-54927-4

► EMC for Product Engineers - Tim Williams (Newnes Publishing) ISBN 0-7506-2466-3

► Grounding & Shielding Techniques - Ralph Morrison (5th Edition John Wiley & Sons) - ISBN 0-471-24518-6

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

58

GOFSL

G – Ground and Power Planes

► O – Oscillator layout

► F – Filtering

► S – Software Techniques

► L – LUCKY!!!!!!!

►

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

59

Hardware and Layout

Basic EMC/EFT Design Checklist – ONE PAGER

Power and Ground Routing done first

MCU VSS should be on ONE layer, no vias if possible, multiple vias if layer transitions

Connect VSS, VSSAD, VREFL pins together

Good Osc layout, Filter GND from VSS

Bypass caps for supply right at MCU pins, make bigger if possible. (0.1uF to 1uF if possible)

Reset and IRQ filtered with 0.1uF cap, 10k pull up at micro

BDM line needs a 10k pull up and some series resistance if brought out to a connector

Prevent over voltages on VDD (>8V) at micro; use a TVS or Zener at VDD, VSS of micro.

Prevent VSS differential (>0.3V) by connecting VSS pins together, good routing, limit vias, use continuous trace.

(See first three bullets)

► Decoupling on board edge if PS is off board for temp sensor, motor, etc.

► Keep VDD and VSS at micro as parallel as possible for mutual inductance

► Input filter caps located close to micro and tied back to micro’s VSS and VDD rails

► Interlace DC signals with fast switching signals (clocks, door lock, charge pumps, A2D, EEPROM)

► Include BDM connections for possible diagnostics during noise testing i.e., Hotsync and Programming

►

►

►

►

►

►

►

►

►

Software

►

►

►

Unused I/O – configure as outputs driving low

Unbonded I/O ports – configure as outputs driving low

Unused modules – write control registers to turn off

Clocks, order of operation

Set up system registers first: SOPT, SPMSC1, SPMSC2, SOPT2 registers (LVD, COP, low power)

Set up the oscillator: 1)read and write trim value, 2)write ICGC2 register first (multiplier, divider, LOx reset),

3) write ICGC1 (clock and mode), 4)wait for lock

►

►

•

•

►Set

Enable loss of clock reset (LOCRE=1)

Enable loss of lock interrupt (LOLRE=0); ICG interrupt should make sure it’s locked before returning.

up I/O

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are

the property of their respective owners. © Freescale Semiconductor, Inc. 2006.

TM

60