Low Noise Amplifier for 5 – 6 GHz

(WLAN/802.11a) Applications using the MGA-665P8

Application Note 5081

Introduction

Avago Technologies’ MGA‑665P8 is a low noise MMIC using

enhancement mode PHEMT technology. The MGA-665P8

requires a +3V at a nominal 20 mA and has a useful pow‑

erdown function. The device is ­designed predominantly

for the 5 to 6 GHz 802.11 and WLAN markets, but can be

applied to other applications in the 0.5 to 6 GHz frequency

range.

While the new Avago Technologies’ enhancement mode

technology provides excellent RF performance, it also sim‑

plifies MMIC design by only requiring a positive voltage on

the gate for normal FET operation. This allows sources to

be direct grounding without the customary source resistor

and associated source bypass capacitor.

The MGA-665P8 is housed in a miniature 2.0 x 2.0 x 0.75

mm 8 pin Leadless Plastic Chip Carrier (LPCC) package.

The compact low profile package offers a size advantage

for many applications.

MGA-665P8 Circuit Description

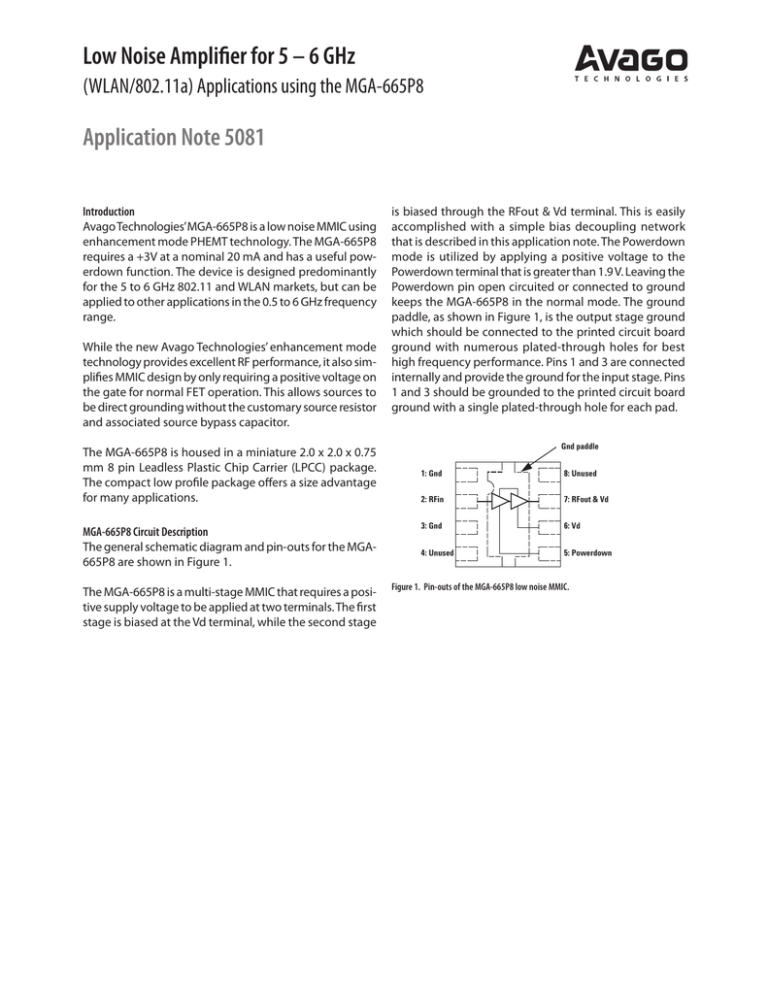

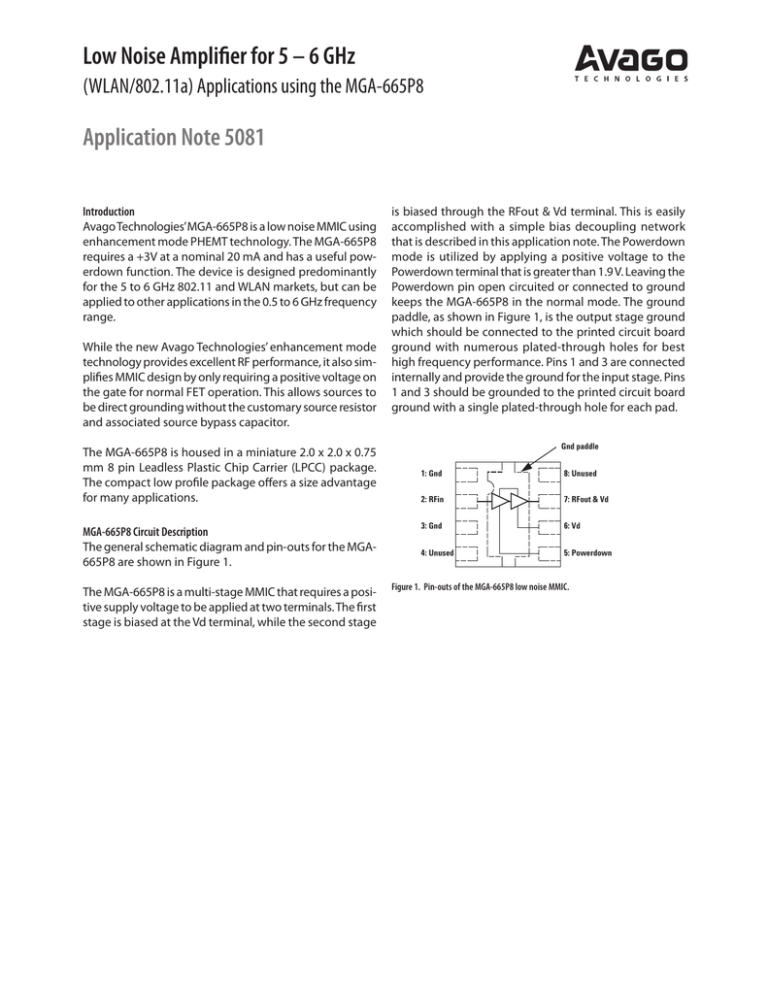

The general schematic diagram and pin-outs for the MGA665P8 are shown in Figure 1.

The MGA-665P8 is a multi-stage MMIC that requires a posi‑

tive supply voltage to be applied at two terminals. The first

stage is biased at the Vd terminal, while the second stage

is biased through the RFout & Vd terminal. This is easily

accomplished with a simple bias decoupling network

that is described in this ­application note. The Powerdown

mode is utilized by applying a positive voltage to the

Powerdown terminal that is greater than 1.9 V. Leaving the

Powerdown pin open circuited or connected to ground

keeps the MGA-665P8 in the normal mode. The ground

paddle, as shown in Figure 1, is the output stage ground

which should be connected to the printed circuit board

ground with numerous plated-through holes for best

high frequency performance. Pins 1 and 3 are connected

internally and provide the ground for the input stage. Pins

1 and 3 should be grounded to the printed circuit board

ground with a single plated-through hole for each pad.

Gnd paddle

1: Gnd

8: Unused

2: RFin

7: RFout & Vd

3: Gnd

6: Vd

4: Unused

5: Powerdown

Figure 1. Pin-outs of the MGA-665P8 low noise MMIC.

MGA-665P8 Demonstration Board

This application note describes the

use of the MGA-665P8 in a design

optimized for the entire 5 to 6 GHz

frequency range. One design can

thus cover both the 5.125 to 5.325

GHz and the 5.725 to 5.825 GHz

frequency ranges. The demonstra‑

tion board provides a nominal 15 dB

gain, a 1.8 dB noise figure, S11

greater than 10 dB, and S22 greater

than 20 dB over the 5 to 5.9 GHz fre‑

quency range. The OIP3 is a nominal

+18 dBm with a +7 to +8 dBm P1dB.

The schematic diagram describing

the MGA-665P8 amplifier is shown

in Figure 2. The parts list for the

demo board is shown in Table 1.

Standard 0402 chip components are

used in the assembly.

The input network consisting of C1

and L2 provide a broad band match

that provides a good noise figure

coincident with good input return

loss. C1 also provides a dc block for

the device. Inductor L2 is actually

a microstrip line whose length can

be varied to provide optimized

performance over a portion of the

5 to 6 GHz band. L2 also provides

improved ESD protection for the

amplifier by providing a dc short at

the input of the amplifier.

2

Table 1. Parts list for MGA-665P8 Demo Board.

C1

1 pF Phycomp 0402

C2

2.2 pF Phycomp 0402

C3

1000 pF Phycomp 0402

C4

10 pF Phycomp 0402

C6

.01 µF

J1, J2

E.F. Johnson SMA connector 142-0701-881

L1

1.8 nH Toco LL 1005-FH

L2

Short to ground at a point .100” away from

input line, adjust for best S11

R1

2.2 Ω

INPUT

C1

Zo

GND

RF IN

GND

J1

Unused

OUTPUT

C2

Unused

Zo

RFout & Vd

Vd

L1

Powerdown

L2

C4

C3

R1

C6

Vc

Figure 2. Schematic Diagram of the MGA-665P8 Amplifier.

Vd

J2

Performance

The performance of a typical dem‑

onstration board is now described.

The power supply voltage is +3V

with a nominal current of 20 mA.

The plots in Figures 4 and 5 show

S21, S11, and S22 from 5 to 6 GHz.

3

GAIN (dB)

The demonstration board is a two

layer configuration for rigidity with a

total board thickness of 0.030 inch‑

es. The signal layer is the top layer

which is 0.010-inch thick RO-4350,

while the bottom layer is 0.020-inch

thick FR-4. The RF input and output

connectors, J1 and J2, are designed

for 0.031-inch thick printed circuit

boards. The center pin is trimmed

to about 0.040 inches in length.

Then the connectors are installed

such that the center pin lays down

directly on the printed circuit board

with no gap between the printed

circuit board and center pin. Be sure

to solder both the top and bottom

ground pins of the connectors to

the printed circuit board.

Figure 3. MGA-665P8 Demo Board. Actual PCB size .69” x .85”

16.0

15.9

15.8

15.7

15.6

15.5

15.4

15.3

15.2

15.1

15.0

5.0

5.2

5.4

5.6

5.8

6.0

FREQUENCY (GHz)

Figure 4. Gain response (S21) from 5 to 6 GHz for a typical MGA‑665P8 demonstration board.

0

-5

RETURN LOSS (dB)

As the S22 of the MGA-665P8 is

already very good in the 5 to 6 GHz

frequency range, network L1 and C2

provides a broadband bias decou‑

pling network for the insertion of

dc into the output stage and by also

providing a dc block at the output.

C4 provides an in-band RF bypass for

L1 and also provides a convenient

point at which the first stage of the

MGA-665P8 can be biased. R1 pro‑

vides a low frequency resistive termi‑

nation. C6 provides a low impedance

bypass that reduces power supply

noise. One of the most overlooked

purposes of C6 is the importance of

this component in terminating the

different signals produced when

making third order intermodulation

distortion measurements.

-10

S11

-15

-20

-25

S22

-30

-35

-40

5.0

5.2

5.4

5.6

5.8

6.0

FREQUENCY (GHz)

Figure 5. Input Return Loss (S11) and Output Return Loss (S22) from 5 to 6 GHz for a typical

MGA-665P8 demonstration board.

-34.0

-34.5

ISOLATION (dB)

The demonstration board has

greater than 15 dB gain from 5 to

6 GHz. The input return loss (S11) is

greater than 10 dB return loss from

5 to 5.9 GHz. Over the narrower

5.125 to 5.325 GHz frequency range,

S11 is greater than 15 dB. Due to

the broadband nature of the MGA665P8, the demo board is capable

of greater than 20 dB output return

loss (S22). The plot shown in Figure

6 shows the exceptional S12 of the

MGA-665P8. Good S12 allows the

MGA-665P8 to be used as a buffer

for a local oscillator to minimize

pulling on the local oscillator due to

load changes.

-35.0

-35.5

-36.0

-36.5

-37.0

-37.5

-38.0

5.0

5.2

5.4

4

5.8

6.0

FREQUENCY (GHz)

Figure 6. Isolation S12 of the completed MGA-665P8 demonstration board.

20

S21

0

S11

(dB)

Of equal importance is amplifier

stability. By itself, the MGA‑665P8

is unconditionally stable. However,

circuit topology can often turn an

unconditionally stable device into

an ­unstable amplifier. The plot

shown in Figure 7 shows the broad‑

band response of the MGA‑665P8

demonstration board. Notice the

smooth gain roll-off with no un‑

necessary out-of-band gain peaks.

Also note that S11 and S22 stay

negative indicating stable perfor‑

mance. Although ADS predicts a K

greater than 1 for the completed

demo board, it is comforting to be

able to measure K for the completed

demonstration board. This is easily

accomplished by measuring the

4 S parameters of the demonstra‑

tion board from 0.1 to 20 GHz and

inserting them into ADS as a .S2P

file and letting ADS calculate K or

other desired stability factors. The

plot in Figure 8 indicates that the

MGA-665P8 demonstration board is

unconditionally stable as K is greater

than 1 from 0.1 to 20 GHz.

5.6

-20

S22

-40

-60

0

2

4

6

8

10

12

14

16

18

20

FREQUENCY (GHz)

Figure 7. Gain, input return loss, and output return loss for the completed MGA-665P8

demonstration board from 0.1 to 20 GHz.

5

4

3

2

1

0

-1

0

2

4

6

8

10

12

14

16

18

20

Figure 8. Stability Factor K for the completed MGA-665P8 demonstration board

from 0.1 to 20 GHz.

In order to measure accurate

S parameters for the demonstration

board, several guidelines should be

followed. The full 2 port calibration

must be used so that both ampli‑

tude and phase can be measured

from 0.1 to 20 GHz. Data at 100 MHz

increments should suffice. The

power level must be sufficiently low

as to not drive the amplifier into

compression. This will typically be

in the -35 to -25 dBm power level

range for the MGA-665P8.

At the lower frequencies where the

gain of the demo board amplifier

is extremely low and the isolation

very high, a network analyzer with

extremely good dynamic range and

couplers with very good directivity

below 1 GHz may be required in or‑

der to achieve accurate data. A small

error in calibration, especially at

very low frequencies, can cause S11

or S22 to be slightly positive, when

in reality the reading is very close

to zero. Getting a good isolation

calibration may also be necessary

in order to get accurate S12 values

as the demonstration board ampli‑

fier gain S21 is already fairly low

at VHF frequencies. Although the

MGA-665P8 demonstration board

amplifier is not expected to have

any usable gain below 1GHz, it is

still very important that the ampli‑

fier be unconditionally stable at all

frequencies. The calculation of the

stability factor K still requires precise

S parameter amplitude and phase

information to achieve an accurate

determination of stability.

5

The OIP3 is typically +18 dBm at

5.2 GHz and 5.8 GHz, while the

output P1dB is nominally +8 dBm.

As RF input levels approach P1dB,

the device current will rise above

the quiescent bias point. The plot in

Figure 9 shows the effect of RF input

drive level vs. RF power output and

device current. The graph shows

that at P1dB the device current has

risen from about 19 mA to approxi‑

mately 26.5 mA.

The measured noise figure of the

completed demo board is approxi­

mately 1.8 dB from 5 to 6 GHz.

The noise figure can be slightly

improved at the expense of S11

by “fine tuning” with the input

microstrip line L1. The loss of the

input network consisting of the

shunt microstrip line and input

capacitor C1, including microstrip

losses, is measured at 0.28 dB at

5.2 GHz. Subtracting this from the

measured demonstration board

noise figure of 1.8 dB yields a device

noise figure of 1.52 dB.

10

31

8

29

6

27

4

25

2

23

0

21

-2

19

17

-4

-6

15

Power Output (dBm)

Device Current (mA)

-8

13

11

-10

-25

-20

-15

-10

-5

POWER INPUT (dBm)

Figure 9. RF output and device current vs. RF input level for the MGA-665P8

demonstration board.

Powerdown Mode

The MGA-665P8 can be externally

controlled by applying a voltage to

the Powerdown terminal at pin 5.

With pin 5 left open or connected

to ground, the MGA-665P8 operates

normally. As the control pin is in‑

creased above roughly 1.2V, the gain

and device current start to decrease.

This effect is shown in Figure 10. As

the control voltage approaches 1.9V,

the device current is about 140 µA

and the gain is ­decreased to –23 dB.

Conclusion

The MGA-665P8 has been shown

to provide low noise amplification

in the 5 to 6 GHz frequency range.

The MGA-665P8 provides a nominal

15 dB gain, a 1.8 dB noise figure,

very good S11 and S22, and an OIP3

of +18 dBm at a power supply volt‑

age of 3V at 20 mA.

25

20

15

10

5

0

-5

-10

Gain (dB)

Device Current (mA)

-15

-20

-25

0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

CONTROL VOLTAGE (V)

Figure 10. Gain and Device Current vs. Control Voltage for the MGA-665P8

Demonstration Board.

For product information and a complete list of distributors, please go to our web site:

www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Limited in the United States and other countries.

Data subject to change. Copyright © 2006-2010 Avago Technologies, Limited. All rights reserved.

5989-2416EN May 25, 2010

2