1800 V NPN bipolar junction transistors in 4H-SiC

advertisement

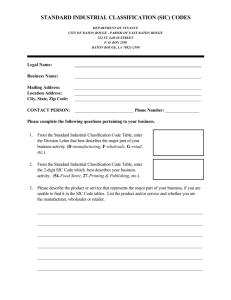

124 IEEE ELECTRON DEVICE LETTERS, VOL. 22, NO. 3, MARCH 2001 1800 V NPN Bipolar Junction Transistors in 4H–SiC Sei-Hyung Ryu, Member, IEEE, Anant K. Agarwal, Member, IEEE, Ranbir Singh, and John W. Palmour, Member, IEEE Abstract—The first high voltage npn bipolar junction transistors (BJTs) in 4H–SiC have been demonstrated. The BJTs were able to block 1800 V in common emitter mode and showed a peak cm2 at room current gain of 20 and an on-resistance of 10.8 m temperature ( A@ V for a 1 mm 1.4 mm active area), which outperforms all SiC power switching devices reported to date. Temperature-stable current gain was observed for these devices. This is due to the higher percent ionization of the deep level acceptor atoms in the base region at elevated temperatures, which offsets the effects of increased minority carrier lifetime at high temperatures. These transistors show a positive temperature coefficient in the on-resistance characteristics, which will enable easy paralleling of the devices. =27 =2 Index Terms—4H–silicon carbide, bipolar junction transistor, high voltage, temperature-stable current gain. I. INTRODUCTION S ILICON carbide (SiC) is a very attractive material for high voltage, high power switching devices because of its wide bandgap, high breakdown field, and high thermal conductivity [1]–[3]. Power MOSFETs [4], [5] in SiC have received much of the attention, but high performance SiC power MOSFETs have yet to be developed due to poor MOS channel mobility and reliability, especially in 4H–SiC. On the other hand, bipolar devices such as GTOs [6]–[13] have demonstrated high blocking voltages and high on-currents, taking full advantage of the material properties of SiC. However, power bipolar junction transistors have received very little attention, with only some low voltage BJTs in 6H–SiC being previously demonstrated [14], [15]. In this letter, we report the first demonstration of high voltage npn bipolar junction transistors in 4H–SiC. The BJTs were able to block 1800 V in common emitter configuration and showed a cm peak current gain of 20 and an on-resistance of 10.8 m ( A at V for a 1 mm 1.4 mm active area), which outperforms all SiC power switching devices reported to date. Moreover, these transistors show a positive temperature coefficient in the on-resistance characteristics, which will enable easy paralleling of the devices. II. EXPERIMENTAL RESULTS Fig. 1 shows a simplified cross section of the device. The three epilayers were grown on 8 off-axis 4H–SiC, n-type subcm. The first n epilayer, strates with a resistivity of 20 m which forms the collector of this device, is 20 m thick and has Manuscript received September 20, 2000. This work was performed on the MURI program, supported by the Office of Naval Research, Contract N00014-95-1-1302, monitored by J. Zolper. The review of this letter was arranged by Editor J. K. O. Sin. The authors are with Cree, Inc., Durham, NC 27703 USA. Publisher Item Identifier S 0741-3106(01)01936-X. Fig. 1. Simplified device cross section of the 4H–SiC power BJT. a doping of cm . The ideal parallel plate breakdown voltage of this layer is approximately 3100 V. Then, a 1 m thick, cm doped p-type epilayer was grown for the base region. Finally, a 0.75 m thick n epilayer was grown to form the emitter regions of the device. The top n epilayer was RIE etched to isolate the emitter fingers. Cell pitches of 14, 23, 35 m were used. Then, a heavy dose aluminum ion implantation was performed to form the p contact regions to the base. The devices were mesa isolated using RIE etching through the base epilayer. Then, a p-type single zone junction termination extension (JTE) region was created by Al ion implantation with cm . After an implant activation a total dose of at around 1600 C, the structure was passivated using a thick deposited oxide layer. The ohmic contacts were made using annealed nickel. Finally, the interdigitated fingers were connected using a 2 m thick, e-beam evaporated Ti/Au layer. Fig. 2 shows the room temperature on-state and blocking m). The characteristics of a 1 mm 1.4 mm BJT (pitch ) of 20 at room temdevice showed a peak current gain ( perature, which is approximately two times higher than a typical commercially available Si power BJT with comparable breakdown voltage [16]. A maximum collector current of 3.8 A (271 mA and V. The A/cm ) was observed at ) breakdown voltage with the base electrode floating ( was 1800 V, and the breakdown voltage of the base-collector ) was approximately 2200 V, which is apjunction ( proximately 71% of the ideal breakdown voltage of the epicm was observed layer. A specific on-resistance of 10.8 m V( A/cm at V). at 0741–3106/01$10.00 © 2001 IEEE RYU et al.: 1800 V NPN BJTs Fig. 2. Room temperature I–V characteristics of a 1 mm configuration. 125 2 1.4 mm 4H–SiC BJT. (a) On-state characteristics and (b) blocking characteristics in common emitter The specific on-resistance at room temperature is plotted as a function of cell pitch in Fig. 3(a). Since most of the current in BJTs flows along the surface of the emitter finger side walls due to emitter crowding [17], the specific on-resistance decreases cm at a cell pitch of 35 with decreasing cell pitch (12 m m to 8.8 m cm at a cell pitch of 14 m). The current gain at room temperature is plotted as a function of collector current density for different values of cell pitch in Fig. 3(b). The current gain ( ) decreases for devices with smaller cell pitch, which have a greater emitter periphery per unit area. This is believed to be due to carrier recombination at the surface of the emitter fingers caused by a high interface state density on the etched sidewalls. This suggests that further optimization is necessary on surface passivation. It has been predicted that SiC npn BJTs will have a negative temperature coefficient for current gain due to deep level acceptors in the base region [18]. A simple expression for current gain is given as follows [17]: Current Gain where Emitter efficiency and base transport factor . At elevated temperatures, the minority carrier lifetime increases, which causes a significant increase in the current gain of conventional silicon bipolar devices. However, in SiC npn BJTs, due to deep level of the Al acceptors, holes that were frozen-out at room temperature ionize at elevated temperatures, resulting in higher hole concentrations in the base at high temperatures. This effect reduces the emitter injection efficiency of the devices at elevated temperatures, which cancels out the effects of Fig. 3. Effect of cell pitch on device performance. (a) On-resistance versus cell pitch, (b) current gain versus cell pitch. the increasing minority carrier lifetime in the base region, and keeps the current gain of the SiC npn BJTs stable with respect to temperature. Fig. 4(a) shows the current gain of the 23 m cell pitch device at temperatures ranging from room temperature to 250 C. The V. Only a modest incurrent gain was measured at crease in the current gain with temperature was observed due to the reduction in the emitter efficiency, with a peak current gain ) of 20 at room temperature, increasing to 25 at 250 C. ( The specific on-resistance of the devices [Fig. 4(b)], which was mA, increased with temperature (10.8 measured at cm at room temperature to 19.7 m cm at 250 C). m This is believed to be mainly due to the increasing resistance in the collector region due to decreased carrier mobility at high temperatures. These features reduce the possibility of a thermal runaway and should make paralleling easy for these devices. III. SUMMARY High performance (1800 V, 10.8 m cm , at room temperature) 4H–SiC npn bipolar junction transistors in 4H–SiC have been demonstrated, which outperforms all SiC power switching devices with comparable blocking voltages reported to date. The BJTs exhibited a temperature-stable 126 IEEE ELECTRON DEVICE LETTERS, VOL. 22, NO. 3, MARCH 2001 Fig. 4. Effect of temperature on device performance: (a) current gain increases slightly with increasing temperature up to 250 C, and (b) specific on-resistance increases with temperature. current gain due to higher percent ionization of the deep level Al acceptor atoms in the base region at elevated temperatures, which makes these devices attractive for paralleling. A significant decrease in common emitter current gain was observed for tight pitch devices, which is caused by surface recombination at the etched sidewalls. Further optimization of surface passivation, especially on etched sidewalls, is necessary to improve these devices. REFERENCES [1] J. B. Casady and R. W. Johnson, “Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature application: A review,” Solid-State Electron., vol. 39, no. 10, pp. 1409–1422, 1996. [2] P. G. Neudeck, “Progress in silicon carbide semiconductor electronics technology,” J. Electron. Mater., vol. 24, pp. 283–288, 1995. [3] M. Bhatnagar and B. J. Baliga, “Comparison of 6H–SiC, 3C–SiC, and Si for power devices,” IEEE Trans. Electron Devices, vol. 40, pp. 645–655, Mar. 1993. [4] K. Hara, “Vital issues for SiC power devices,” in Proc. Int. Conf. Silicon Carbide, III-Nitrides and Related Materials., Stockholm, Sweden, Aug. 31–Sep. 5, 1997. [5] J. Tan, J. A. Cooper Jr., and M. R. Melloch, “High-voltage accumulationlayer UMOSFET’s in 4H–SiC,” IEEE Electron Device Lett., vol. 19, pp. 487–489, Dec. 1998. [6] J. W. Palmour, R. Singh, L. A. Lipkin, and D. G. Waltz, “4H–SiC high temperature power devices,” in Trans. 3rd Int. Conf. High-Temperature Electron. (HiTEC), vol. 2, Albuquerque, NM, June 1996, pp. XVI-9–14. [7] B. Li, L. Cao, and J. H. Zhao, “High current density 800-V 4H–SiC gate turn-off thyristors,” IEEE Electron Device Lett., vol. 20, pp. 219–222, May 1999. [8] J. B. Casady et al., “4H–SiC gate turn-off (GTO) thyristor development,” Mat. Sci. Forum, vol. 264–268, pp. 1069–1072, 1998. [9] S. Seshadri et al., “Current status of SiC power switching devices: Diodes & GTOs,” in Mat. Res. Soc. Spring Mtg., San Francisco, CA, Apr. 1999. [10] J. B. Fedison et al., “Factors influencing the design and performance of 4H–SiC GTO thyristors,” in Proc. Int. Conf. Silicon Carbide and Related Materials 1999, Research Triangle Park, NC, Oct. 1999. [11] A. Agarwal et al., “2600 V, 12A, 4H–SiC, asymmetrical gate turn off (GTO) thyristor development,” in Proc. ICSCRM, Research Triangle Park, NC, Oct. 1999. [12] A. K. Agarwal et al., “Turn-off performance of a 2.6kV 4H–SiC asymmetrical GTO thyristor,” , submitted for publication. [13] S. Ryu et al., “3100 V, asymmetrical, gate turn-off (GTO) thyristors in 4H–SiC,” IEEE Electron Device Lett., vol. 22, pp. 127–129, Mar. 2001. [14] J. W. Palmour, J. A. Edmond, H. S. Kong, and C. H. Carter Jr., “6H–silicon carbide devices and applications,” Phys. B: Condensed Matter, vol. 185, pp. 461–465, Apr. 1993. [15] Y. Wang et al., “Mechanisms limiting current gain in SiC bipolar junction transistors,” in Proc. Inst. Physics Conf., ch. 4, 1996, pp. 809–812. [16] “Philips Semiconductor BU2508DF Power Transistor Datasheet,”, July 1998. [17] S. M. Sze, Physics of Semiconductor Devices, 2nd ed: Wiley, 1981, pp. 140–147. [18] K. Adachi et al., “TCAD evaluation of double implanted 4H–SiC power bipolar transistors,” in Proc. ICSCRM, Research Triangle Park, NC, Oct. 1999.