Low Power AC-DC and DC-DC Multilevel Converters

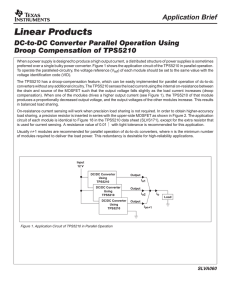

advertisement