Transistors, Gates and Busses 3/21/01 Lecture #18 16.070 NB

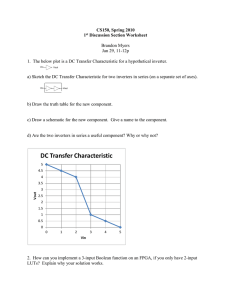

advertisement

Transistors, Gates and Busses 3/21/01 Lecture #18 16.070 • The goal for today is to understand a bit about how a computer actually works: how it stores, adds, and communicates internally ! How transistors make gates ! How gates make useful elements like memory and adders ! How information is communicated within a computer NB: Models today are in some cases simplified - this is how it works in principle, not necessarily in exact detail Fesq, 3/19/01 1 16.070 Learning Objectives • Students should be able to ! Explain TTL logic ! Identify how gates are made ! Explain how gates produce useful elements ! Discuss data busses and their operation Fesq, 3/19/01 2 16.070 Silicon (The material, not the Valley) • Silicon is the basis for (almost) all modern electronics ! It is a semi-conductor -- it has resistance midway between conductors and insulators ! Each Si atom has 4 covalent bonds to neighbors ! It can be doped by adding similar, but not identical atoms − Molecules with 5 outer electrons (e.g., arsenic) brings an extra electron which is somewhat free - an n-type − Molecules with 3 outer electrons (e.g., boron) brings a deficit of an electron (a hole) - a p-type − Both types are electrically neutral but have mobile electrons and holes - free charge carriers - - + - Fesq, 3/19/01 3 + + - + + + 16.070 P-N Junctions Make Diodes • P and n material are "placed" next to one another • Some holes in p diffuse toward n, and some electrons in n diffuse toward p • The electrons and holes combine, creating a depletion region with no free charge carriers • Due to loss of holes and electrons, p- now has a net negative charge, nhas a net positive charge ! Now there is a potential difference (0.6V), which prevents any further charge motion ! This blocks any current flow -- like an insulator Fesq, 3/19/01 4 16.070 P-N Junctions • If an external voltage is connected (+) to p, (-) to n, the free charge carriers are attracted as shown, collapsing the depletion region " current can flow ! Current will increase with increasing voltage ! This is forward bias Fesq, 3/19/01 5 16.070 n-p-n Junctions Make TTL Transistors • A bipolar transistor consists of n-p-n collector-base-emitter. This is transistor-transistor logic (TTL) Fesq, 3/19/01 6 16.070 TTL Operation • A TTL device operates in one of three modes ! When Vin "Low" (near 0), the base-emitter junction is "closed," no current flows (cut off), and Vout goes Hi towards Vcc (+5V) - this is a low Vin high Vout switch ! When VB gets towards 0.6V, the base-emitter junction is forward biased, and current flows -- the larger Vin the larger Ic - this is a linear amplifier ! When Vin gets sufficiently large, Ic is large enough that most of the voltage drop occurs across Rc, so Vout goes low- this is a a high Vin low Vout switch +5V Rc Ic Vin collector base Fesq, 3/19/01 Vout emitter 7 16.070 TTL Logic • For positive logic, High is defined as 1, Low is defined as 0 ! For TTL in: > 2.0V is High, < 0.8V is Low ! For TTL out: > 2.4V is High, < 0.4V is Low ! Transition Status is undefined • What Logical gate does this represent? • Other common Logics are ECL (Emitter-Coupled Logic) and CMOS/FET (Complementary Metal-Oxide Semiconductor/Field Effect Transistor) - choice is made based on speed, power drain Fesq, 3/19/01 Vout 5 5 Hi 4 3 2.4 2 1 0.4 Lo 0 0 Vin 0 1 2 Lo 0 8 0.8 3 4 5 Hi 2.0 5.0 16.070 Logic to Gates built of TTL • Useful gates can be built up out of Transistors and Resistors • The fundamental TTL gate is a NAND, made up (in principle) of two transistors ! (Vin1) or (Vin2) or (Vin1 and Vin2) Low − Current through R1 flows to emitter. Collector of T1 drawn Lo TWO-EMITTER TRANSISTOR − No current through T2, Vout High R1 ! Vin1 and Vin2 High T1 − Collector of T1 High E − Current flows through T2, Vout Low Fesq, 3/19/01 +5V +5V Vin1 9 RC T2 B C C Vout B E Vin2 16.070 Voltage Table and Truth Table • What is truth table? V1 LO LO HI HI V2 LO HI LO HI Vout x 0 0 1 1 # Positive logic y 0 1 0 1 z x z y NAND Fesq, 3/19/01 10 16.070 Real Tri-State NAND • Real NAND gates have more components and one more function ! OE (Output Enable) causes the output to be specified by the gate when the OE is High +5V T2 OE IN1 Vout1 IN2 ! Allows the output to float (i.e., be set by other devices hanging on the same output line) when OE is low OE 0 1 1 1 1 IN1 ALL 0 0 1 1 IN2 ALL 0 1 0 1 Gate 2 OUT FLOAT 1 1 1 0 Gate 3 Vout x1 z1 y1 OE Fesq, 3/19/01 11 16.070 NAND is a Logical Building Block • Other gates can be built up from NAND's (and NOR's) x NOT: x z 0 1 x z =x•y AND: y OR: x z =x + y y z x y 0 0 1 1 0 1 0 1 x y 0 0 1 1 0 1 0 1 z z • Not necessarily the most efficient way, but gates could be built up this way • So how many transistors (on average) to a gate? • How many gates to a modern processor/memory chip? Transistor " NAND " All Gates Fesq, 3/19/01 12 16.070 Adding • The basic function of the Arithmetic Logic Unit is to add • Half Adder can add two one-digit binary numbers 1+1 Input Bits 1 1 1 1 1 1 BINARY XOR AND 1 Fesq, 3/19/01 DECIMAL 13 0 BINARY = 2 DECIMAL 16.070 Full Adder • Full Adder is needed when there is a result to carry over • Modern processors have 32 full adders in ALU Fesq, 3/19/01 14 16.070 Writing to Static RAM (Random Access Memory) • In order to store a piece of digital information to memory, 3 functional we inputs are required ! The information you write (xin) ! The command signals that instruct the memory write (0) address A 1 0 address decoder ! The address to which you write (A) (1) (0) (0) • When we (write enable) goes high, writes 1310 (11012) to address 210(102) and latches a3 a2 din dout L din dout L a1 etc. a0 (1) x3 (1) x2 (0) x1 (1) x0 Data in, out (din, dout) Numbers in () are example Fesq, 3/19/01 15 16.070 Details of RAM Write • Need a few more functions to make this write cycle work ! Address decoder, which reads a digital address, and activates a single address line ! A latch, which when the data appears at its input, and the proper clock stroke is activated, latches or stores the bit until told to do otherwise (more in next lecture) ! The timing and control signals to drive the "write enable" (we) Fesq, 3/19/01 16 16.070 Read/Write Timing and Control • The computer is synchronized by a master clock, which establishes the clock cycle and its associated clock strobe (CS) • During certain specified clock cycles, write to RAM is enabled (WE). During all other clock cycles, read from memory is enabled din we dout Tri-state gate! Din Dout CS re WE ! Timing for write Timing for read CS A CS address valid A Din data valid WE write Fesq, 3/19/01 address valid Dout data valid 17 16.070 Communication • The processor/ALU communicates with memory (and all other devices internal to the computer) via an internal bus • The information transfer function on the bus is driven by memory transfer ! Address address ! Data data ! Control CS WE commands • All internal busses are parallel; i.e., there is a line for each bit of address, each bit of data, and each type of control signal • Within these common features, there is a great deal of variance "width" of bus (what # of bits can be transmitted simultaneously), address space, speed/timing, and sophistication of commanding Fesq, 3/19/01 18 16.070 Parallel Internal Busses • Handyboard Memory and CPU schematic Fesq, 3/19/01 19 16.070 Bus Control and Protocols • Typically one device on the bus is the controller, which maintains the master clock, and issues instructions • All other devices hang on the bus, and listen to the controller, responding to instructions address data commands CPU RAM Disk controller Peripheral interface A/D D/A Peripheral analog analog Disk • The combination of the device in out driver software is the CPU plus the hardware that hangs on the bus allows the CPU to transfer information to and from a wide variety of devices transparently • Other busses connect to peripherals (next time) • A/D (Analog to Digital ) conversions and D/A (Digital to Analog) allow communication with analog world (next time) Fesq, 3/19/01 20 16.070 Summary • The world runs on aluminum and silicon, the latter being the basis for semiconductors, which are built up into gates • Gates are the building blocks for adders, stacks, memories, etc. which form devices (CPU, ALU, RAM, …) • Devices communicate command, address and data via busses Note • Issue: Length of time to do problem sets Fesq, 3/19/01 21 16.070