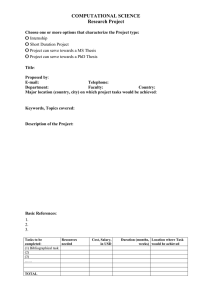

Master Thesis/Internship 2015 Topic Guide

advertisement