ROBUST ELECTRONIC CIRCUIT DE SIGN FOR YIELD

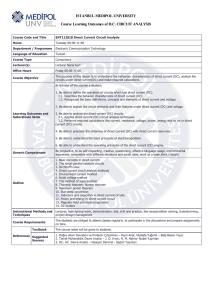

advertisement

F R A U N H O F E R - I N S T I T U T F Ü R techno - un d wirtschaftsmathemati k – k aisers l autern probability p a ra 1 1 Wafer 2 Multidimensional distribution of two correlated parameters met er 1 pa ra m ROBUSt electronic circuit de­ sign for yield optimization Motivation and aim the statistical properties of the parameter variations, the simu­lation time significant- With the trend from micro- to nanoelec- ly decreases and new expertise concerning tronics the control of production deviations the most relevant parameters and the in- can not keep pace with the reduction of fluence of their distributions on the system the absolute sizes of semiconductor devices. behaviour are generated. Both features are This results in a drastic increase of relative critical for a successful development of ro- parameter variations and thus in a decreas- bust circuits and to optimize nano­electronic ing yield of produced circuits due to system systems. behaviours beyond the specifications. The aim of this work is to assist designing Circuits with parameter tolerances on Fraunhofer-Institut für Techno- und of robust circuits to minimize the amount system level Wirtschaftsmathematik ITWM of defective circuits and therefore to increase the yield of production. The Fraun- For the construction of a symbolic behav- Fraunhofer-Platz 1 hofer ITWM considers electronic circuits at ioural model with parameter tolerances at 67663 Kaiserslautern system level using its EDA software Analog system level the netlist, the model card pa- Insydes, which allows analysis and symbol- rameters and their distributions have to be Contact ic approx­ima­tion of nominal analog circuits. extracted from both, device and circuit lev- Matthias Hauser The software now has been extended to el. That can be done automatically by the Phone +49 631 31600-44 32 handle parameter variations and analyse interface between Analog Insydes and Ca- matthias.hauser@itwm.fraunhofer.de electronic circuits with process variations dence, one of the most used commercial as well. By reducing a symbolic system to software tools for the design of ­electronic its most important terms, while keeping circuits. www.itwm.fraunhofer.de et er 2 2 Vout Vout 3.5 3.4 Vin Original Approximation 3.3 3.2 3.1 3.0 3.0 3.2 3.4 3.6 3.8 4.0 4.2 4.4 1 Analog Insydes allows the handling of a 2 1 Voltage limiter circuit Example 2 Input-output behaviour of the great variety of predefined distributions. Additionally empirical distributions from As a typical example for an industrial circuit measurements of the parameters can be here a voltage limiter circuit, which limits used. The generated symbolic model equa- the output voltage to 3.5 volts, is consid- tions can be applied to large signal, small ered. The sizes of the 30 MOSFET transis- signal, transient or sensitivity analysis of tors and the values of the two resistors are the circuit. The sensitivity analysis yields an normally distributed with standard devia- approximation of the variation of the out- tions of 1 – 2 %. For a given rather tight er- put behaviour depending on the parame- ror bound the numeric-symbolic reduction ter distributions. This gives an estimation of routine cancels 69.2 % of all terms and the relevance of each parameter. 59.2 % of the equations. This leads to a simulation time which is shortened by a factor 12, without changing the behaviour Model reduction and keeping the symbolic form. The model equations can be reduced with The diagram above shows the simulation respect to parameter distributions by a results of the original (yellow) and the re- mixed numeric-symbolic algorithm. This is duced model (blue) for several samples of done by taking data from sensitivity analy- the parameter distributions. Also the re- sis to avoid using expensive Monte- Carlo duced model keeps the characteristic lim- simulations and thus to save reduction iting behaviour. As shown in the zoomed time. Statistical error functions in the algo- area, the distribution of the output voltage rithm, like Kolmogorov-Smirnov-test or of the original system is well approximated Signal-To-Noise-test, guarantee a good ap- by the corresponding one of the reduced proximation of the original system behav- system. iour. The symbolic form of the model is kept. Due to its decreased complexity, the reduced model allows more efficient simulations and analysis of the system. Hence it is possible to identify the influence of the Number of Simulation equations time most critical parameters and their distributions on the input-output behaviour. With this, useful information about the nec- Original model 353 18.59 s Red. model 144 1.54 s 59.2 % 91.7 % essary accuracy in the circuit production steps for reaching a predefined yield can be extracted. This helps optimizing the circuit production, developing a robust circuit and finally increasing the yield. Reduction Vin voltage limiter