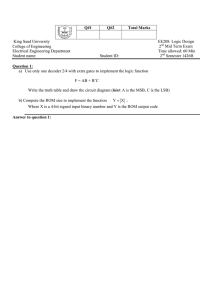

programmed logic arrays

advertisement

programmed logic arrays (pla (pla)) programmed logic arrays (pla's) are implementations of two-stage logic: and-array φ1 input register output register inputs outputs ΣΠ = left nor-array or-array φ1 φ2 right nor-array inverting input register inverting output register inputs outputs (ΣΠ)= (ΠΣ ) = (Π Σ ) = (Σ Σ ) easy to transform from and-or format to other two-stage formats φ2 sequential circuits with pla programmed logic arrays (pla's) are implementations of two-stage logic, including sequential logic combinatoric circuit φ1 register register φ for example: "slave"-latches at the inputs left "master"-latches at the output right φ2 floorplan of pla’s essential is the use of regularity in the programmed logic arrays TL LL φ1 left nor-array inverting input register TR IC right nor-array inverting output register RR φ2 UT IN inputs LB TL TL TL TL MB TR TR TR RB LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LO IN IN IN IN M0 UT UT UT RO outputs 1. identify "tiles" that are distinct: the less the better, independent of the array size 2. determine the basic layout: rows and columns extendable in the “dashed areas” pla-tiles example in nmos-technology with depletion-transistors (nor-nor) 5. add the pull-up V+ LC LL LB TL TL TL TL MB TR TR TR RB LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LO IN IN IN IN M0 UT UT UT RO LC LC IN 1. input signals, also complemented φ2 2. connections with the uncomplemented signal 3. connections with the complemented signal 4. not in the product occurring signal pla-tiles V+ 8. add the pull-up example in nmos-technology with depletion-transistors (nor-nor) TR V+ LL LB TL TL TL TL MB TR TR TR RB LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR LL LC LC LC LC IC RC RC RC RR RC LL LC LC LC LC IC RC RC RC RR φ2 LO IN IN IN IN M0 UT UT UT RO LC RC LC LC IN 6. connection with the products in the sum 7. non-occurring product unconnected φ2 UT 9. add the output circuitry nmos pla Why nor-nor? φ2 φ1 a b c d S0 S1 no individual βe's no series of transistors what you should know pla’s? many equivalent two-stage format: and-or, nor-nor, nand-nand small number cells, easy to program area possible in nmos and in cmos: - preferably nor-nor (no individual βe's, no series of transistors) - ratio logic (levels! dissipation! βn Wn Lp Attention: cmos β ≠ L W (# in + # out) # prod. p n p !) universal modules B B A A I0 I1 Z I2 I3 with a 2n-way multiplexer all combinatoric functions of n variables can be realized I0 I1 I2 I3 Z(A,B) naam 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 A.B; A+B A.B B A.B A AB + AB A+B; A.B A.B A.B + AB A A + B B A + B A + B 1 disable nor Z = A.B.Io + A.B.I1 + A.B.I2 + A.B.I3 invert B invert A exclusive-or nand and comparator A B or nmos-selectoren two implementations depletion transistors: yellow squares indicate ion implantation: lowering the threshold voltage only enhancement transistors: presence or absence of transistors considerably more area delay models A A B B P0 P1 F P2 P3 A P0 Cb A B Cb Cb A B P0 Cb P1 P1 Cb Cb Cb Cb P2 P2 P3 Cb Cb Cb Cb Cb Cb P3 Cb Cb A B Cc B Cc Cc Cc Cc Cc Cc Cc selector models A A B B P0 P1 F P2 P3 • the delay from inputs to output increases quadratically with the size of the selector • if controlled via the signal lines delay increases there also quadratically • if transistor are of the same type: also loss of levels cmos selector Why is a cmos-selector not made by replacing pass transistors of a nmos-selector by transmission gates? twice as many wires twice as many transistors more contact holes for every row a well is needed regularity at transistor level one or no transistor per cell pretty generic, and easy generation for large, complex combinatoric functions: inefficient examples: selector, pla the selector: all combinatoric functions! area increases exponentially with the number of variables delay increases quadratically with the number of variables only two (very simple) cells as basic tiles pla’s: all combinatoric and (clocked) sequential network permutation circuits in0 in1 in2 out0 out1 out2 inn-1 outn-1 control signals rotations crossbar-switch out3 n2 control signals O(n) wired per cell out2 → cell layout depends on module size! out1 for special cases (for example a rotator or shifter) regular and extendable. out0 in0 in1 in2 in3 barrel shifter out3 regardless of the size n of the shifter, only four different cells independent of n ! out2 out1 out0 in0 in1 in2 in3 barrel shifter regardless of the size n of the shifter, only four different cells independent of n ! parity generator PGn pn high pn = low if an odd number of inputs is high if an even number of inputs is high decompose: n bits PGn ( v1, v 2 , v 3 L vn ) = ( ) PGk ( v1, v 2 , v 3 L vk ) ⊕ PGn-k vk + 1,vk + 2 L vn = PGn − k + 1(PGk ( v1, v 2 , L vk ), vk + 2 L vn ) k PGn − k + 1 PGk , vk + 1 L vn 1 k PGk 1 n PGn − k k + 1 n PGn 1 0 0 0 0 0 1 1 1 1 0 1 1 1 1 0 0 decomposition of the parity generator pn PGn decompose in PGk en PGn-k+1 n bits Pk PGk k bits k = n - 1 pn n-k bits Pn-1 PGn-1 complete decomposition in PG2's p0 =low PGn-k+1 PG2 pn 1 bit n-1 bits PG2 PG2 PG2 v1 v2 v3 PG2 vn pn 2-bit-parity generator = exor vi vi p i = p i − 1 ⊕ vi vi pi-1 pi-1 pi-1 N pi vi pi-1 pi pi N pi-1 vi vi exclusive-or (exor): pi = pi-1 . vi + pi-1 . vi transmission gates preserve the levels, but delay the signal invertors have to interrupt every path to the output layout of the generator cell vi pi-1 pi pi-1 pi shifter with pass cells Ai+1 s s Ai basic idea 1: if s is high, the top input is set on the base line . if s is low , the bottom input is kept on the base line basic idea 2: encode the shifting distance “binary”: if sj is high, shift is over 2j positions a "logarithmic" shift unit realisation of a shift cell s s Ai+1 Ai protection against level degeneration of high level realisation of a shift cell design a signature checker we have two bit sequences of equal length. the sequences are stored in two registers. design a circuit that decides whether the two are equal! the design must be suitable for a any given length, that is circuits only differ in number of replications of the same cell, and the sizing of the overhead circuit! signature analyse so so s1 s1 sn-1 sn-1 v to to t1 t1 tn-1 tn-1 a pull-down-cel si si v V_ ti ti signature analyse so so s1 s1 sn-1 sn-1 v to to tn-1 tn-1 t1 t1 si si ti ti transistor schematic si si ti ti the current equations βnmin VOL βp < 1 − 1 − 2 V+ − Vto 2 v2 T2 v1 T1 vo 2 β n2 2 β n1 i= i= βp β n2 βp β n1 ( V+ + Vtpo ) 2 = (V+ − Vtno − v1 )2 − v 0 )2 − (V+ − Vtno − v 1 )2 βp 2 + β = (V + − V tno − v 0 ) n2 − (V + − V tno − v 2 )2 ( V+ + Vtpo ) 2 = (V+ − Vtno (V+ + Vtpo )2 ββnp 1 2 ( V+ − Vto ) − (V+ − Vtno − v 2 )2 2βp β n min = (V + − V to )2 − (V + − V to − v 2 )2 design equation 2 βnmin VOL βp < 1 − 1 − 2 V+ − Vto v2 T2 Wmin µ nc ox 2 L Wmin VOL nmin µ p c ox 1− 1− < Lp 2 V+ − Vto v1 T1 vo 2µp Lp > µn Lnmin VOL 1− 1− V+ − Vto 2 signature analyse so so s1 s1 sn-1 sn-1 v to to tn-1 tn-1 t1 t1 si si V+ V-ti ti other questions • is the design suitable for large-scale integration? – is repetition of cells possible? – how many cells have to be designed ? – regular wiring? • what is the delay as a function of the number of cells? – constant (approxamately)? – linear? – logarithmic? – quadratic? – exponential?