Capacitor Values: Don`t Believe the Label

advertisement

Capacitor Values:

Don’t Believe the Label

By Steven M. Sandler

Sandler, Program Engineer, Acme Aerospace

Division and Actuant Co., Tempe, Ariz., and Charles E.

Hymowitz, Managing Director, AEi Systems, Los Angeles

Variation in capacitor characteristics due to dc

bias and other effects impact power-supply design and simulation, and their impact becomes

greater as designers pursue higher performance

and higher reliability.

S

urprisingly, more often than not, a ceramic

capacitor does not exhibit its specified value of

capacitance in an actual power-supply application. So the 22-µF capacitor you’ve selected won’t

look like 22 µF once its designed into your circuit.

The underlying problem is parasitics. These nonideal characteristics are a chronic driver of performance and can be

painful to deal with, especially when you don’t realize they

are impacting your circuit operation. A high-frequency dcdc converter provides a design example that illustrates the

impact of various parasitics on capacitors when modeling

the converter’s performance in SPICE.

Worst-case circuit analysis (WCCA) is often invoked for

space and aerospace hardware that cannot afford to suffer a

performance outage or loss of any function. However, we are

seeing other disciplines such as medical equipment, critical

data backup and storage servers, and high-volume power

systems use WCCA techniques to improve reliability much

more frequently than in the past. Using WCCA techniques,

we evaluate the impact of initial temperature aging and

other environmental tolerances (radiation, vibration and

moisture) on performance.[1]

As designers are pushing their circuit

��

designs to achieve higher performance,

�����Ω

�

��

it is increasingly important to understand the consequences that second��

order effects such as capacitor dc bias

��

�����

and their associated tolerances, can have

on circuit performance and simulation

results.

Semiconductor’s LM2831, a high-frequency 1.5-A stepdown

regulator. The process is one that AEi Systems regularly uses

to develop SPICE models for National Semiconductor’s

WEBENCH online simulation system.

The normal process is to start by gathering bench-test

data from an application circuit and then comparing the

real-life performance with that of the SPICE model to provide concrete verification of the simulation results. In our

experience, the models have consistently matched the bench

data to within a few percentage points of phase margin and

crossover frequency. However, in the case of the LM2831,

we could not get the frequency-response bench data to line

up with the SPICE model.

While it is a common reaction to blame the SPICE model

for being the source of error, more often than not we find the

test setup or measurement technique is at the heart of the

discrepancy. Some of the anomalies are rather interesting.

In this case, as part of the model development process,

we performed load-step bench tests and recorded Bode

plots. The load-step response simulations agreed with the

measured data almost perfectly, but the Bode responses did

��

������

���

��

�

���

���� ��

��

���

��

������

�����

������٠����

��

�����

�����

��

����Ω

��

��

����Ω

Second-Order Effects

����

������

��

�����

�����

�����������

��

����Ω

To illustrate the significance of second-order effects, consider a problem

AEi Systems encountered when trying Fig.1. LM2831 SPICE model generated by AEi Systems was compared with bench-test data and

to model the performance of National found to correlate only after the output capacitor dc-bias effects were accounted for.

Power Electronics Technology May 2007

22

www.powerelectronics.com

���

�����

����

�����

����

����

���

���

���

��������������������������

���

���

���

����

�����

���

����������������������������

����������������������

���

�����

����

������

�

�

����

�����������������������

����������������������

��

���

������

��������

����������

��������

������������

��������������������

�����������������

����

����

������������

������������������

�����������������

���

�����

���

���

����

����

���

����

����

����

����

����

����

����

���

����

�����

��������������

������

���

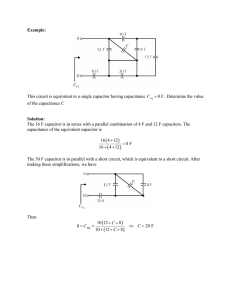

Fig. 3. Results of the change in capacitance from 16 F (biased at 1.8 V)

to 22 F, the state value. The difference in phase margin is dramatic.

�����������

Fig. 2. DC-bias effects for the X7R and X5R paint a dramatically different

picture. At 28% of rated voltage, the capacitance is down almost 25%

for the X5R.

of the output capacitance. Therefore, we conceived that the

only way the step-load result could be correct and the Bode

response incorrect would be if the capacitor value were the

culprit (assuming the Bode measurement was correct).

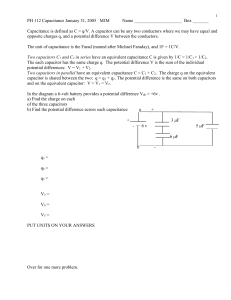

The LM2831 test circuit is shown in Fig. 1 with the parts

list indicating a 22-µF ceramic X5R capacitor. Trying to

understand the error, we calculated what we thought the

not. Interestingly, due to the transconductance nature of the

control loop, the bandwidth of the regulator is inversely proportional to the capacitance and the closed-loop impedance

(step-load response) is related to 1/(capacitance bandwidth). So the closed-loop impedance is nearly independent

API Delevan Offers Passive Products

®

Superior performance through high quality manufacturing

— Epoxy molded construction offers reliability & robustness in any environment

— Temperature stable components with high Q & high SRF available in many

thru-hole & surface mount package sizes

— Shielded components in small surface mount & thru-hole sizes minimize

coupling to less than 2%

— Tight tolerance winding capabilities to +/-1% of nominal inductance

Don’t settle. With us, you can choose.

www.powerelectronics.com

23

American Precision Industries

www.delevan.com

MI

A

L I TA R Y

PP

ROVE

D

Power Electronics Technology May 2007

CAPACITOR CHARACTERISTICS

��� ��

��

��������������������

��

��

������

����������������������

���

��

��

�

�����

�����

�����

�����������������������

����

�����

����

���

����

����

���

����

�����

������

����

��������������

�����

�����

��� �

���

������������������������

�

������

����������������������

�

���

���

���

����

����

����

��� ���� ���� ����

����������������

���� ����� ����

�����

����

Fig. 4. Capacitance change versus ac volts and overtemperature for the

X7R ceramic capacitors.

�����

������

����

��������������

�����

�����

Fig. 5. At lower frequencies (~1 kHz to 10 kHz), the ESR is much greater

for the TAJ series, which can impact step-load response and phase

margin. Also note that at the lower frequencies, the ESR can be four or

more times greater than at typical switching frequencies (~100 kHz).

capacitor would have to be to produce the bandwidth difference between the measured and simulated Bode plots. The

answer was 16 µF, and so we might reasonably consider the

possibility that a 15-µF capacitor had been used in place of

the 22-µF capacitor.

It is generally assumed that ceramic capacitors can be

modeled with a simple RLC or RC-equivalent circuit (simple

ESR representation), owing to the fact that the ESR is so low

compared to the reactive impedance. This is usually an acceptable compromise in the fidelity of the capacitor model,

and everything usually correlates reasonably well with this

approach.

At this point, we requested and were provided with the

manufacturer’s capacitor datasheet. It quickly became clear

that there was a severe dc-bias effect (Fig. 2). The manufacturer’s data indicated that at 1.8 V (the converter’s output

voltage) the capacitance decreased by 25%, which made the

capacitance 16.5 µF. The resulting Bode data for the two

different capacitor settings is shown in Fig. 3.

Development of a capacitor SPICE model with dc-bias

effects is fairly trivial.[2-3] For a static solution based on the

circuit’s operating point, a capacitor with dc bias can be even

more easily achieved with parameter-passing techniques

common to most SPICE simulators, where the value of the

capacitor is computed as {Cnom * Bias Effect * Temperature effect}. The Bias Effect parameter can be dynamically

modeled with a table model that takes in voltage and outputs a percentage equal to that of the curve found in the

Power Electronics Technology May 2007

����

manufacturer’s datasheet, which then multiplies against

the nominal capacitance of a voltage-controlled capacitor.

Programs such as Kemet SPICE[4] output a SPICE model at

a specified dc bias and temperature setting.

Parameters such as aging, frequency and ac bias (Fig. 4)

are also often overlooked, as are variations in one of the most

underspecified parameters with the greatest impact: ESR.

One of the more common issues that we see concerns the

use of tantalum and niobium-oxide capacitors. These general

pitfalls also apply to aluminum electrolytic capacitors and

wet-tantalum capacitors.

ESR is generally specified and discussed as a number,

usually a maximum ESR at a specified frequency. It is important to remember that ESR is actually a strong function

of frequency and temperature. But nominal and certainly

statistical data can be hard to come by. Depending on the

capacitor, the ESR curve can vary significantly.

What this means in your simulations is that the ESR

you use to calculate the output ripple voltage at the switching frequency might be very different than the ESR you

use to evaluate the phase margin at the bandwidth of the

power supply. This same issue often appears in EMI filter-damping networks that have a relatively low resonant

frequency. At these low resonant frequencies, the ESR

24

www.powerelectronics.com

CAPACITOR CHARACTERISTICS

�����������������

����������

���������

�����������

���

���

���

���

��

����������������

����������������������������������������

���

�������������

��

��

��

��

��

��

����� ����� ����� ����� ����� ����� ����� ����� ����� ������

������������

Fig. 7. Aging for ceramic capacitors varies according to the type of

dielectric used.

���

���

����

����

��

����

����

����

����������������

�����

����

in any case, do not cover mission life in the 5- to 20-year

range. Arrhenius equations assume a linear time base and,

therefore, are not useful in most cases.[6] The MIL-HDBK1547A standard’s estimate of 21% aging is based on such

extrapolations and is considered overly pessimistic, especially

with regard to today’s manufacturing processes. It is not

uncommon, however, to see -2.5% to -4% per decade hour

factored into most designs. Using the equation, the aging

rates presented in the table for various dielectrics may be

used to calculate capacitance over time:

Fig. 6. The wet-tantalum curves show a dramatic rise in ESR at low

temperature. (Data courtesy of NASA.)

is often high enough to significantly affect the damping

effectiveness.

As the frequency increases, it is also common for the

capacitance to decrease, which must be considered when

assessing the effectiveness of the damping of the EMI filter

and also in the stability assessment of the power supply.

Fig. 5 shows ESR curves from two

22-µF, 6.3-V capacitors from the same

manufacturer with clearly different

low-frequency ESR performance.

Another often-overlooked issue is

cold temperature operation.The effects

of cold temperature (-55°C) on capacitor performance is significant. Cold

temperature use of ceramic and solid

tantalum capacitors generally results in

a 10% to 20% reduction in capacitance

with a 10% to 20% increase in ESR.

It is often assumed that this effect

WORKS

RC NET

is similar for wet-tantalum and aluS

K

N

A

ITOR B

minum capacitors, which is not true.

CAPAC

ILITIES

B

A

P

A

C

Very little information is published

CUSTOM

regarding cold temperature use of these

capacitors. However, measurements

we have made, and also measurements

made by NASA, show that there is genMERS

NSFOR

OIL TRA

F

erally a 1500% (yes, 15 times) increase

TERS

EMI FIL

d

CUSTOM

gistere

in ESR of wet-tantalum and aluminum

S

R

O

v. B Re

IT

004 Re

CAPAC

:2

R

0

O

0

C

1

A

capacitors when operated at –55°C

SE

AS 9

1:2000 •

ISO 900

(Fig. 6).[5]

Fig. 7 and the table describe aging

“The Cube” delivers!

• specifications on-line

factors for various types of capaci• stocking distribution

tors. Such variations are a concern for

®

• custom design

equipment that cannot be upgraded

• engineering support

www.electrocube.com

or replaced during its lifetime. Often

• local sales

1307 S. Myrtle Ave • Monrovia, CA 91016

life test data is not available. HALT and

• factory service

TEL: (800) 515-1112 • FAX: (626) 357-8099

HASS testing can be expensive and,

E

D

I

S

N

I

THINK

E!

B

U

C

X

THE BO

www.powerelectronics.com

25

Power Electronics Technology May 2007

CAPACITOR CHARACTERISTICS

Dielectric/

capacitor type

Ceramic NPO

Ceramic X7R

Ceramic BX

Ceramic Z5U

Ceramic Y5V

Ceramic (BP)

capacitors

Ceramic (BP)

capacitors

Tantalum (CSR)

capacitors

Typical dielectric

constant

65

2000

4000

8000

10,000

—

Typical aging

rate (%)

None

1.5 to 2.5

3 to 4

4 to 5

6 to 7

±21* (-2.5 to -4 per

decade hour)

—

1.25 to 2.1

—

±10

Table. Aging rates of various dielectric types. *MIL-HDBK-1547A is considered overly pessimistic.

1− A

C A = C1

log10 (t) ,

log

100

where CA equals capacitance after t (hours), C1 equals

cpacitance at time t0 , A equals dielectric aging constant (aging

rate in percent) and t equals time from last heating (hours).

Beyond the IC Datasheet

It is important for the designer to have an understanding

of the many parameters associated with the use of capacitors

in power-supply applications, as well as an understanding of

the tolerance effects that are associated with these parameters.

As capacitor technology improves and switching frequencies

increase, the power supplies become much more sensitive to

these effects, which can, in some cases, dominate the powersupply performance. In some applications, more often in

linear regulators than switching regulators, we see unstable

control loops due to inordinately low capacitor ESR.

While the manufacturers of the linear regulators generally do not supply sufficient information to understand or

calculate the stability of their devices, the capacitor ESR is

often a significant zero in the regulator loop, meaning that

a very low ESR will result in an unstable loop. This is even

more common with the older regulators such as the LM117,

since at the time these regulators were designed, there were no

ultralow ESR capacitors, which means the effects of stability

on these capacitors were never considered.

PETech

References

1. Sandler, Steve, and Hymowitz, Charles, “Worst Case Analysis

of Three Terminal Regulators: Development of an HS-117

SPICE Model,” PowerSystems World 2006.

2. Intusoft newsletters, November 1995/January 1996.

3. Prymak, John, “SPICE Modeling of Capacitors,” Kemet

Electronics.

4. Kemet SPICE, www.kemet.com/kemet/web/homepage/

kechome.nsf/Weben/kemsoft#spice, Kemet Electronics.

5. Holladay, A.M., “Guidelines for the Selection and Application

of Tantalum Electrolytic Capacitors in Highly Reliable Equipment,” NASA Technical Memorandum TMx-64755, Rev. A.

6. “Worst Case Circuit Analysis of Power Conversion Circuits,”

APEC 2007.

www.powerelectronics.com

27

For superior solutions

in information and

communications

• Miniaturized SAW filters for all systems

and bands

• LTCC front-end modules for multiband

systems and WLAN

• Application-specific EMI/ESD filter modules

• Arrays of CeraDiodes for ESD protection

• Surge arresters and varistors for all systems

• Ferrites and transformers with low losses

for DSL systems

www.epcos.com

Power Electronics Technology May 2007