AAN-26

AAN-26

CEB3405 Evaluation Board for

CDK3405, 8-bit, 180MSPS, Triple Video DAC

Features

■ ■

■ ■

Up to 180 MWPS Conversion Rate

Reference Voltage Circuit

■ ■

Standard Video BNC Connectors for DAC Outputs

■ ■

■ ■

Data and Clock Buffers

Clock and Data Monitor Test Points

■ ■

Clock, Sync and Blank Inputs Selectable for 0 or 180 Degree

Phase

■ ■

Option to add CLC3800/CLC3801 Triple Video Filter

Applications

■ ■

■ ■

Evaluation of the CDK3405 Video DAC

RGB Video Generator

■ ■

Standard Definition Video Filter Option

■ ■

■ ■

Guide to PCB Layout

Guide to Design with the CDK3405

■ ■

Guide to Design with the CLC3800

General Description

The CEB3405 evaluation board is intended as a tool for device evaluation and characterization and to demonstrate the performance of the CDK3405 (8-bit, 180 MWPS Triple Video DAC). The CEB3405 will accept up to 8-bit binary input words into each of the three DAC inputs. These data signals are buffered by a 10-bit buffer. (Note: The lower two bits should be tied to ground with jumpers at each of the three header inputs.) A single input clock and two control signals (SYNCb and

BLANKb) are also buffered using dual input XOR gates. This allows for easy phase inversion of these signals if timing control is required. The digital input data for all three DACs is latched into the CDK3405 on the rising edge of the clock input signal.

The output current is determined by an external resistor which sets a reference current based upon the device reference voltage V

REF

. V

REF

is generated internal to the CDK3405, or optionally can be generated externally and applied to the V

REF input. Output current is converted to an output voltage with a ground referenced 75Ω external resistor. Output levels can be overridden by the two control signals (SYNCb and BLANKb) to insert the required video synchronization signals.

This application note is a supplement to the CDK3405 datasheet and is intended to provide more applications detail with respect to: power supplies and grounding, logic interface circuits, external voltage reference circuits and specific layout issues.

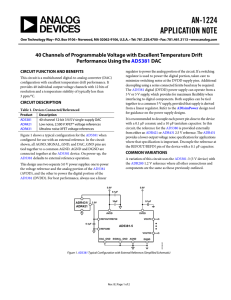

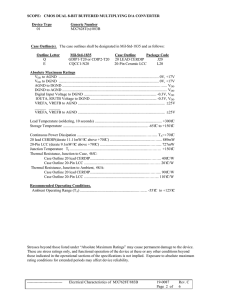

Block Diagram

© 2014 Exar Corporation

Clock

Buffers

J8 Header

J2 R0 – R7 Header

8

R

NET

Buffer

8

8

R0 – R7

V

REF

R

OUT

V

REF

G0 – G7 CDK3405

G

OUT

BLANKb

SYNCb

CLK

B0 – B7

Buffer

8

8

R

NET

J3

8

B0 – B7 Header

B

OUT

Figure 1: CEB3405 Evaluation Board Block Diagram

1 / 10 exar.com

Rev 1A

AAN-26

Power Supplies and Grounding

The CEB3405 requires two separate +3.3V power supplies.

One for the digital circuitry which includes the input and clock buffers, and one for the analog circuitry which includes the CDK3405, external reference circuit and the optional

CLC3800 video filter option. The CLC3800 option can be powered from either the board analog supply, or if desired from an additional separate power terminal. Adequate decoupling of both supplies is incorporated into the design. However, use of low-noise (non-switching) regulated supplies with low source impedance is recommended.

for an effective load resistance of 37.5Ω.

So, from above, with a standard full-scale video level

(WHITE) of 700mV, sets I

FS

= 700mV/37.5Ω = 18.67mA.

And so R

SET

= 5.31 (1.235V/18.67mA) = 355.6Ω. To ensure adequate output levels, this is rounded down to the next standard resistor size of 348Ω.

8

1/3

CDK3405

Zo = 75Ω

The power return and grounding connections are accomplished with a split ground plane, one for the digital return and one for the analog return. The two ground planes are coupled together through an inductive ferrite bead (L1) near the DAC. The purpose of this connection is to keep the high-speed digital switching signal noise from entering the low-noise analog section.

75Ω

Figure 2. Typical DAC Connection

75Ω

Video Data and Timing Circuits

Reference Circuits

The CDK3405 provides an on-board voltage reference of 1.25V, and can be accessed at the test point labeled

REF_TP. The internal reference requires an external 0.1uF compensation capacitor, which is installed between COMP

(pin35) and the positive analog supply.

Digital RGB data is brought on-board through three separate 20-Pin headers (J1-J3). Each of the 10 input bits for each convertor has an associated ground return pin.

As the CDK3405 is an 8-bit device, the lower two bits for each DAC are tied to ground potential with a jumper at the header input. The data passes through 10-bit TTL buffers before being presented to the CDK3405. Pull-up resistors are present on all inputs to ensure fixed levels if the inputs are left floating.

For higher accuracy, the CEB305 also contains an external reference voltage source that can be accessed through jumper J7. If connected, the external reference will override and take precedence over the internal reference of the

CDK3405 and appear at REF_TP. The required 0.1uF VREF decoupling capacitor is present for both configurations.

The CEB3405 reference consists of an integrated twoterminal band-gap reference diode, LT1004. The typical output at 100uA bias is 1.235V ± 4mV. The reference diode is biased to the analog supply with a 3.3KΩ resistor, setting a bias current of 1.136mA.

Reference currents for the DAC are derived from V

REF through a current setting resistor, R41 attached between

R

SET

(P37) and analog ground. The full-scale output current of each DAC is a multiple of this value, so a low tolerance, ceramic thin-film resistor is used. The nominal value for R

R

SET

SET

= 5.31 (V

can be derived from:

REF

/I

FS

)

The CEB3405 evaluation board accepts three separate timing clocks, CLOCK, BLANKb and SYNCb. Please refer to the datasheet for a more detailed description of their functions. The timing inputs are all located on the J8 header connector. Ground return connections for all three clocks are available on J19.

The clocks are all buffered using a 74F86 Exclusive-OR gate. This not only helps to match the delay of the data input buffers, but also allows for a 180° phase inversion. This may be useful when interfacing to additional clocked systems, such as an upstream digital video processor.

All three DAC’s capture and convert their respective input data with the same clock. Data is latched into the

CDK3405 on the rising edge of its clock input. Analog outputs follow after a delay, t

D

from rising edge. For the

CEB3405 evaluation board, the system clock is input on the

J8 header.

I where I

FS

is the desired full-scale output current.

FS

is determined by the required full-scale output voltage divided by the DAC resistive load:

Refer to the datasheet for specific timing information such as data set-up and hold times and minimum clock pulse widths.

I

FS

= V

FS

/ R

LOAD

Figure 1 below shows a single DAC driving a typical

75Ω video load over a 75Ω transmission line. To reduce transmission reflections, an additional back-matching 75Ω resistor is used. This appears in parallel with the video load

© 2014 Exar Corporation

It is important that negative transients are not introduced onto the data or clock inputs. To alleviate this, 22Ω resistors are placed in series with all inputs to reduce the current injection from high slew rate edges.

2 / 10 exar.com

Rev 1A

AAN-26

Analog Outputs

The three RGB outputs are comprised of variable, groundreferenced current sources. To create an output voltage, these currents drive a resistor tied between the output and analog ground. As mentioned in the Rerfence Circuits section above, this voltage is dependent upon three factors:

1. Effective output load resistance

2. Absolute value of the reference voltage (V

REF

)

3. And the value of the R

SET

resistor.

Although designed for standard video levels of 700mV with additional 300mV headroom for sync signals, the outputs can range anywhere within the allowable compliance range.

Typical output load is expected to be 37.5Ω. If lower values are used, please ensure that the maximum current output ratings are not exceeded.

The CEB3405 is configured with a fixed, low tolerance 75Ω load resistor on each output. It is expected that the user will attach the outputs to an external standard 75Ω video load via the output BNC connectors. Failure to properly terminate the outputs will result in twice the expected output voltage swing.

CLC3800 Option – Triple Standard Definition

Video Reconstruction Filter

If desired, the CEB3405 can be configured with a

CLC3800 video reconstruction filter. With this option, the CLC3800 and associated decoupling capacitors are added to the bottom side of the board. Removal of jumpers J26, J27 and J28 are required to isolate the outputs of the CDK3405 from the outputs of the CLC3800.

In this configuration, the outputs of the CDK3405 are available at the R, G and B test points and the outputs of

CLC3800 are routed to the output BNC connectors.

NOTE: If using this option, ensure that the jumpers remain disconnected to ensure isolation of the DAC and

FILTER outputs.

The CLC3800 provides 6dB of gain as well as a 4th order

8MHz Butterworth low-pass filter. A 75Ω series backmatching resistor is included for driving a standard doubly- terminated load. As with the CDK3405, an external 75Ω video load is expected to provide proper video levels.

Outputs can be either DC or AC coupled.

Power connection for the CLC3800 can be tied to the same analog supply used by the CDK3405 through jumper J30.

In addition, as the CLC3800 can operate down to a 3V supply, a separate power connection is available to help demonstrate the low power operation of the CLC3800.

PCB Layout

Careful consideration of the layout of this evaluation board was performed by Exar to ensure maximum performance for the part and to aid users in developing similar designs and layout aspects. Some highlights of the CEB3405 layout are as follows.

■ ■

The ground plane is split into analog and digital planes. They are tied together at only one point through a ferrite bead

(L1). This connection reduces the amount of digital switching noise being induced into the analog output.

■ ■

Separate supplies are used for digital and analog circuitry.

All buffers and clock circuits run from the digital supply. The

CDK3405 and the reference source are powered from the analog supply.

■ ■

■ ■

If a single supply is desired, an additional ferrite bead should be used to help isolate digital switching noise from entering the analog rail used for the CDK3405. In this configuration, separate supply decoupling capacitors should be used on each rail and terminated to their respective ground plane.

This evaluation board contains both energy storage and high frequency bypass power supply decoupling capacitors.

■ ■

Controlled impedance signal traced and associated termination of signals should be considered when operating this device at maximum conversion rates. This is necessary to minimize energy reflections from contaminating signals, especially at high slew and repetition rates. Sockets for

SIP resistor or RC networks have been provided. A series termination resistor has been provided for each clock signal.

■ ■

Undershoot transients are kept within limits for this evaluation board by using buffers in front of and in close proximity to the

CDK3405.

© 2014 Exar Corporation 3 / 10 exar.com

Rev 1A

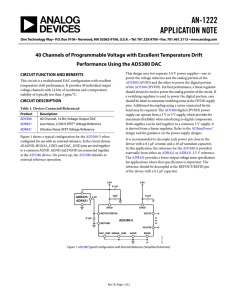

AAN-26

2 J26-

1 J26-

2 J27-

1 J27-

2 J28-

1 J28-

DGN

DGN

DGN

DGN

DGN

DGN

DGN

DGN

DGN

DGN

13

19

17

15

9

7

5

3

1

11

J2-

J2-

D

D

J2-

J2-

D

D

D

J2-

D

J2-

J2-

J2-

J2-

J2-

D

D

D

D

8 J2-

10 J2-

12 J2-

2 J2-

4 J2-

6 J2-

18 J2-

20 J2-

14 J2-

16 J2-

2

2

2

2

2

2

2

2

2

2

22

R7

22

R8

22

R6

22

R9

22

R4

22

R5

22

R3

22

R1

22

22

R2

R10

1

1

1

1

1

1

1

1

1

1

1

2 J30-

1 J30-

1 1

IN GNDP

J24

CLK

OE

D7

D6

D5

D4

D9

D8

D3

D2

D1

D0

841

11

10

9

8

7

6

5

4

3

2

13

1

U4

Q7

Q6

Q5

Q4

Q9

Q8

Q3

Q2

Q1

Q0

74ABT

16

17

18

19

14

15

20

21

22

23

1

R40

3.3K

2 8

6

1

J20 TP

F VRE

C2 0.

2 J7-

1 J7-

U2

LT1004

4

F 0.1u

C1

1

J16 TP

1

J15 TP

1

J14 TP

R5

R4

R7

R6

R3

R2

R1

R0

44

43

46

45

42

41

48

47

F 0.1u

C4

F 0.1u

C14

IN GNDP

J17

1

IN GNDP

J12

1

IN GNDP

J10

1

1

75

R39

1

1

75

R38

75

R37

2

2

2

20

21

18

19

22

23

16

17

B2

B3

B0

B1

B4

B5

B6

B7

1

J21 TP

CLK

F 0.1u

C3

F 0.1u

C15

1 1

IN GNDP

J25

+5V

+5V

+5V

+5V

+5V

A

6K

R26-

R26-

R26-

R26-

R26-

2

3

4

5

6

D 6K

E

6K

C 6K

B

6K

6

5

4

3

2

B

A

C

D

E

6K

R25-

6K

R256K

R256K

R25-

6K

R25-

+5V

+5V

+5V

+5V

+5V

16

17

18

19

14

15

20

21

22

23

Q7

Q6

Q5

Q4

Q9

Q8

Q3

Q2

Q1

Q0

841

U3

74ABT

CLK

OE

D7

D6

D5

D4

D9

D8

D3

D2

D1

D0

9

8

7

6

5

4

3

2

10

11

13

1

F 0.1u

C16

F 0.1u

C5

IN GNDP

J18

1

11

86

D U6-

74ALS

13

12 F 0.1u

C6

C SYN

1

10

R43

2 8

86

C U6-

74ALS

10

9

NK BLA

1

10

R44

2 6

86

B U6-

74ALS

5

4

1

10

R42

2 3

86

A U6-

74ALS

2

1

3

2

1

J9-

J9-

J9-

2

1

3

J11-

J11-

J11-

3

2

1

J13-

J13-

J13-

2

22

R53

1

3 J19-

3 J8-

2 J19-

2

22

R52

1

2 J8-

1 J19-

2

22

R51

1

1 J8-

5

3

1

9

7

11

13

15

19

17

J3-

J3-

J3-

J3-

J3-

J3-

J3-

J3-

J3-

J3-

1

1

1

1

1

1

1

1

1

1

22

R21

22

R20

22

R18

22

R19

22

R17

22

R15

22

R16

22

R14

22

R13

22

R22

2

2

2

2

2

2

2

2

2

2

20 J3-

18 J3-

16 J3-

14 J3-

12 J3-

10 J3-

4 J3-

2 J3-

8 J3-

6 J3-

© 2014 Exar Corporation

Figure 2: CEB3405 Evaluation Board Schematic

4 / 10 exar.com

Rev 1A

AAN-26

# Reference

4

5

6

1

2

3

U7

U3, U4, U5

U2

R11, R12, R23-R26

U6

L1

7

8

9

J4, J5, J6

J1, J2, J3

J8, J9, J11, J13, J19

10 J7, J26, J27, J28

11 R1-R10, R13-R22, R27-R36, R51-R53

12 R37, R38, R39

13 R41

14 R40

15 C1-C6, C8, C10, C14-C17

16 C7, C18

17 J22, J23, J29

18 J10, J12, J17, J18, J24, J25

19 J14, J15, J16, J20, J21

*

*

*

20 R42-44

* C9

* C10

C11, C12, C13

U9

J30

Manufacturer

Part Number

CDK3405

SN74ABT841ADWR

LT1004CDR-1-2

SN74F86DR

EXC-ELSA35

31-71047-1010

ECJ-2YB1H104K

TAJB106K020R

5010

5011

5002

CLC3800

5010

NOTE:

* These parts are for the CLC3800 video filter option. Not implemented unless special ordered.

Suggested

Manufacturer

Exar

Texas Inst.

Texas Inst.

Texas Inst.

Panasonic

Amphenol-RF

Panasonic

AVX

Keystone

Keystone

Keystone

AVX

AVX

CADEKA

Keystone

Qty n/a n/a n/a

3 n/a n/a

3

6

5

1

12

2

4

33

3

1

3

3

5

6

1

1

1

3

1

Description

Triple DAC

10-bit bis interface D-type transparent latch

1.235V voltage reference

Res_SIP5, 6kΩ

IC Quad 2-In EX-OR Gate

Bead core single 3.5x5mm axial (ferrite bead)

Conn BNC PC Mt Rt/Ang 75Ω

2x10 Header - Right Angle

1x3 Header - Straight

1x2 Header - Straight

22Ω Resistor/5%/50V

75Ω Resistor/1%/50V

348Ω Resistor/1%/50V

3.3kΩ Resistor/5%/50V

Cap 0.1μF 50V Ceramic x7r 0805

Cap Tantalum 10μF 20V 10% Smd

Red Power Connection Pins

Black Power Connection Pins

Test Points

10Ω Resistor/5%/50V

0.1μF Capacitor NC

6.8μF Capacitor NC

220μF Capacitor NC

3-Channel Video Filter NC

Red Power Connection Pins NC

Table 1 – CEB3405 Evaluation Board for CDK3405 - Bill of Materials

© 2014 Exar Corporation 5 / 10 exar.com

Rev 1A

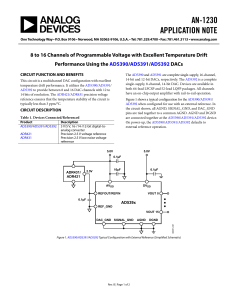

Evaluation Board Layout

AAN-26

Figure 3. CEB3405 Top Side Board Layer

© 2014 Exar Corporation 6 / 10 exar.com

Rev 1A

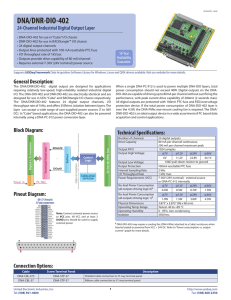

Evaluation Board Layout continued

AAN-26

Figure 3. CEB3405 GND Layer

© 2014 Exar Corporation 7 / 10 exar.com

Rev 1A

Evaluation Board Layout

AAN-26

Figure 3. CEB3405 PWR Layer

© 2014 Exar Corporation 8 / 10 exar.com

Rev 1A

Evaluation Board Layout

AAN-26

Figure 3. CEB3405 Bottom Side Board Layer

© 2014 Exar Corporation 9 / 10 exar.com

Rev 1A

Revision History

Revision

1A

Date

May 2014

Description

Initial release.

AAN-26

For Further Assistance:

Email: CustomerSupport@exar.com

or HPATechSupport@exar.com

Exar Technical Documentation: http://www.exar.com/techdoc/

Exar Corporation Headquarters and Sales Offices

48760 Kato Road Tel.: +1 (510) 668-7000

Fremont, CA 94538 - USA Fax: +1 (510) 668-7001

NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user’s specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR

Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

© 2014 Exar Corporation 10 / 10 exar.com

Rev 1A