© Copyright 2013 ISSCC—Do Not Reproduce Without Permission - 1 -

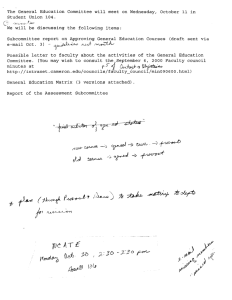

advertisement