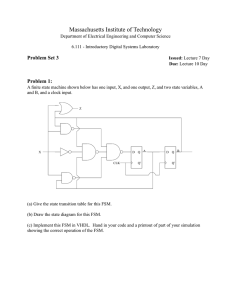

FFs and FSMs

advertisement

CSE140L: Components and Design Techniques for Digital Systems Lab Tajana Simunic Rosing Source: Eric Crabill, Xilinx 1 Overview • Lab #2 due – Reports should already be turned in via email • single PDF file which includes all the question answers requested – Demo signups are on class website • Demo can be on the students laptop or on the Lab computers in B250 • 10min per student; Wed – Sat ( April 28th to May 1st ) • http://cseweb.ucsd.edu/classes/sp10/cse140L/Lab2_demo.html • Lab #3 assigned – Teams of two • What we’re up to: – FFs in Verilog (lab_wk4.pdf) – FSM in Verilog (lab_wk5.pdf) 2 CSE140L: Components and Design Techniques for Digital Systems Lab FSMs Tajana Simunic Rosing Source: Vahid, Katz 3 Hardware Description Languages and Sequential Logic • Flip-flops – representation of clocks - timing of state changes – asynchronous vs. synchronous • FSMs – structural view (FFs separate from combinational logic) – behavioral view (synthesis of sequencers – not in this course) • Datapath = data computation (e.g., ALUs, comparators) + registers – use of arithmetic/logical operators – control of storage elements Controller Design 3.4 • Five step controller design process 5 Controller Design: Laser Timer Example b Controller x laser clk x b Combinational n1 logic n0 s1 s0 FSM outputs patient FSM inputs • Problem: Pressing button (b) once turns on laser for 3 clock cycles • Step 1: Capture the FSM • Step 2: Create architecture • Step 3: Encode the states • Step 4: Minimize logic • Step 5: Implement & test a clk State register • How about synthesis into FPGA? 6 3.3 Laser Timer • Pressing button (b) once turns on laser for 3 clock cycles • Step 1: Capture the FSM b Controller x laser clk patient clk Inputs: b State Off Off Off Off Off On1 On2 On3 Off Outputs: x 7 Controller Design: Laser Timer Example • Step 2: Create architecture – 2-bit state register (for 4 states) – Input b, output x – Next state signals n1, n0 • Step 3: Encode the states – Any encoding with each state unique will work b x=1 01 On1 x=1 10 On2 x b Combinational n1 logic n0 s1 s0 clk x=1 11 On3 FSM outputs – Already done Inputs: b; Outputs: x x=0 00 b’ Off FSM inputs • Step 1: Capture the FSM a State register 8 Controller Design: Laser Timer Example (cont) Inputs: b; Outputs: x x=0 00 b’ Off b x=1 01 On1 x=1 10 On2 x b Combinational n1 logic n0 s1 s0 clk x=1 11 On3 FSM outputs FSM inputs • Step 4: Create state table State register 9 x b Combinational n1 logic n0 s1 s0 clk FSM outputs • Step 5: Implement combinational logic FSM inputs Controller Design: Laser Timer Example (cont) State register x = s1 + s0 n1 = s1’s0b’ + s1’s0b + s1s0’b’ + s1s0’b n1 = s1’s0 + s1s0’ n0 = s1’s0’b + s1s0’b’ + s1s0’b n0 = s1’s0’b + s1s0’ 10 Controller Design: Laser Timer Example (cont) Combinational Logic FSM inputs b x x b Combinational n1 FSM inputs logic FSM outputs • Step 5: Implement combinational logic (cont) n1 n0 s1 s0 State register clk n0 s1 clk s0 State register x = s1 + s0 n1 = s1’s0 + s1s0’ n0 = s1’s0’b + s1s0’ 11 Understanding the Controller’s Behavior x=0 00 Off b x=0 b’ b x=1 x=1 x=1 01 On1 10 On2 11 On3 b 0 0 0 0 0 0 0 clk s1 0 clk 0 0 x=0 00 Off s0 0 state=00 x 0 00 Off b’ x=1 x=1 x=1 01 On1 10 On2 11 On3 b 1 0 0 0 n1 0 0 1 n0 0 0 clk s1 0 0 0 s0 1 state=00 b x 0 b’ x=1 x=1 x=1 01 On1 10 On2 11 On3 b 1 0 1 1 n1 0 0 0 n0 1 0 clk s1 0 1 1 x 1 n1 1 n0 0 s0 0 state=01 Inputs: b Outputs: x 12 Laser timer in Verilog module LaserTimer(b, x, clk, rst); input b, clk, rst; output x; reg x; parameter S_Off = 2'b00, S_On1 = 2'b01, S_On2 = 2'b10, S_On3 = 2'b11; reg [1:0] currentstate; reg [1:0] nextstate; // state register procedure always @(posedge rst or posedge clk) begin if (rst==1) // initial state currentstate <= S_Off; else currentstate <= nextstate; end // combinational logic procedure always @(currentstate or b) begin case (currentstate) S_Off: begin x <= 0; // laser off if (b==0) nextstate <= S_Off; else nextstate <= S_On1; end S_On1: begin x <= 1; // laser on nextstate <= S_On2; end S_On2: begin x <= 1; // laser still on nextstate <= S_On3; end S_On3: begin x <= 1; // laser still on nextstate <= S_Off; end endcase end endmodule // LaserTimer 13