國 立 交 通 大 學 電子工程學系 電子研究所 碩 士 論 文

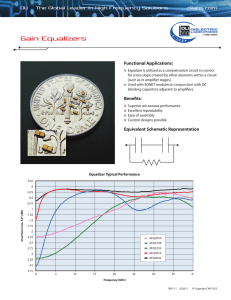

advertisement