A 1-V 36-uW Low-Noise Adaptive Interface IC for Portable

advertisement

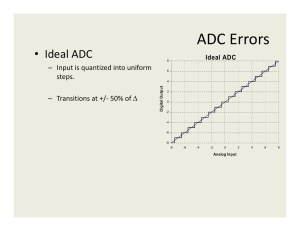

Copyright © 2007 Year IEEE. Reprinted from 2008 IEEE European Solid-State Device Research Conference, 11-13 September 2007.. This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Institute of Microelectronics’ products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubspermission@ieee.org. A 1-V 36-µW Low-Noise Adaptive Interface IC for Portable Biomedical Applications Qiang Li, Kuo Hwi Roy Tan, Teo Tee Hui and Rajinder Singh Integrated Circuits and Systems Laboratory, Institute of Microelectronics (IME), Singapore e-mail: liq@ime.a-star.edu.sg Abstract—This paper presents an adaptive interface ASIC consisting of a low-noise analog front-end and a successiveapproximation ADC. The entire analog signal processing chain is fully-differential for better immunity to common-mode noise and interferences. To make the interface adaptive to different biopotential signals, the bandwidth and gain of the analog front-end are configurable. The ADC is designed for rail-torail operation and the input full-scale is adjustable so that the resolution requirement can be relaxed. Fabricated in 0.18-µm √ CMOS, 95-nV/ Hz input-referred noise density and more than 100-dB CMRR are obtained. Operating in 10-bit mode, the ADC exhibits -1/+0.3-LSB DNL and -1.3/+0.8-LSB INL for 1-V rail-torail input. The whole interface IC consumes 36 µW from a single 1-V supply, making it suitable for a wide range of low-voltage and low-power biomedical applications. Fig. 1. Block diagram of the fully-differential adaptive interface. I. I NTRODUCTION Healthcare technologies are increasingly important and have received extensive research interests in recent years. Since the major functions of signal processing are conducted in the digital domain, an analog interface that reproduces the biomedical signal in the digital domain is fundamentally crucial. The quality of signal acquisition and digitization at the interface determines ultimately the performance of the whole system. In addition, a clear trend of healthcare devices is the portability, where low power and low voltage design are desired for longer battery lifetime or even self-powered operations. Most of biopotential signals are of very low amplitude, e.g. the amplitude of electrocardiography (ECG) signal is around tens of µV to several mV, and the electroencephalography (EEG) signal is at µV level. The bandwidth of the biopotential signals varies from hundred Hz to several kHz. To accommodate different kinds of biomedical signals, the gain and bandwidth of the interface should be adjustable. Meanwhile, the nature of human tissue and the environment result in a lot of noise and interference to the desired signal, e.g. powerline interference, baseline drift and noise due to electrode-skin contact, etc. The analog interface should be able to provide enough dynamic range and noise rejection performance. There are some configurable biomedical front-ends (FE) that have been reported [1]–[4]. However, none of them included an analog-to-digital converter (ADC). An ADC-enabled design is reported in [5], but the fixed gain and bandwidth of the front-end prevent any adaptability. In this paper, we present an configurable biomedical interface, where a lowpower successive-approximation ADC is used and the gain 1-4244-1125-4/07/$25.00 ©2007 IEEE. 288 and bandwidth of the front-end are digitally adjustable. This enables an adaptive system to different kinds of biomedical applications. The design has been fabricated in a 0.18-µm CMOS technology, and consumes only 36 µW from a single 1V supply. It is suitable for a wide range of applications where a front-end biopotential interface is required. II. I NTERFACE A RCHITECTURE The architecture of the interface IC is shown in Fig. 1. It consists basically of three functional blocks: a front-end instrumentation amplifier (IA), an analog signal conditioning block including a band-pass filter (BPF) and a programmablegain amplifier (PGA), and a successive-approximation register (SAR) type ADC. Since a lot of noise and interference to the biomedical signal are of common-mode characteristics, the fully-differential architecture is exploited for better immunity to the common-mode noise. Note that the input signal is DC-coupled directly from the electrodes, which avoids large AC-coupling capacitors that have to be placed off-chip. On the other hand, the DC-coupling of signal brings extra offset introduced by electrodes, which has to be accommodated by the input stage of the IA. The bandwidth and gain of the analog signal conditioning blocks are digitally controllable, so that the adaptive control logic can be easily integrated in the digital domain. For ADC, a resolution of 10–12 bits is usually proposed when it is used after the analog signal conditioning. In this design, however, the resolution requirement is relaxed by adapting the input full-scale of the ADC. Since the input of the ADC is differential, it is then possible to control the input Vdd vINP VREFN Vbp VREFP CF VCHOP Vbpc − AV2 + VIN 2N-1C0 VOUT 4C0 2C0 C0 C0 4C0 2C0 C0 C0 VCM Vbnc CF CMFB 2N-1C0 Fig. 2. Schematic of the DC-coupled fully-differential instrumentation amplifier (feedback not shown). VREFN VREFP vINN C2 MP VINP VINN C2 MP MP MP Non-Overlap Timing Control VOUT+ C1 C1 gm C1 gm C1 MP MP Clock/Control Generation VOUT- MP C2 CLKIN Successive Approximation Register (SAR) MP C2 Digital Output 1st Gain control 1st BW control 2nd Gain control 2nd BW control Fig. 3. Analog signal conditioning circuits (BPF and PGA) with configurable bandwidth and gain. range of ADC conversion, e.g., if the input signal of ADC is around 0.3–0.7 V, then the input full-scale of the ADC can be adjusted to 0.2–0.8 V. In other words, the ADC is adaptable and the resolution requirement can be relaxed, which permits lower power consumption. Here a 10-bit ADC is employed. Note that the adjustment of ADC full-scale is limited by the kT /C noise and other considerations. Since the supply voltage is only a single 1 V, the maximum full-scale voltage is designed ±1 V (differential) rail-to-rail. III. A NALOG F RONT-E ND The consideration of the IA design is mainly on the noise performance. As the first stage that interfaces with electrodes directly, the noise performance of the IA determines fundamentally the overall noise performance. The CMRR of IA is also crucial. As mentioned previously, the IA has to accommodate DC-coupled input that can drift up to ±200 mV. Here a folded-cascode opamp with PMOS input pairs is employed as the first stage of the IA, as shown in Fig. 2. Since the biomedical signals are within the 1/f noise region, chopper technique is exploited at the first stage. Note that the gain of the IA could not be very high, otherwise the interference may saturate the circuits. Meanwhile, a low-gain first stage is not favored considering the noise contributed in the following stages. In this design, the gain of IA is set to a fixed value of 20 V/V. The analog signal conditioning circuits are shown in Fig. 3. The two functions, BPF and PGA, are implemented using the same configuration [6]. For each amplifier, the gain is determined by C1 /C2 , and the high-cutoff frequency is determined 289 Fig. 4. Block diagram of the fully differential SAR ADC. by the load. This configuration is used here because it is of very good noise performance. In Fig. 3, the gain is controlled by switching the capacitors in parallel with C1; and the bandwidth is controlled by switching the load capacitors. This architecture permits higher flexibility in controlling the gain and bandwidth, or concurrently. Note that although the two control stages are similar, the BPF function should always be prior to PGA function so as to prevent out-of-band interference from saturating these stages. Since the gain can only be increased and the bandwidth can only be decreased, the basic circuits without the controlling capacitors set the lowest gain and highest bandwidth, which are 2 V/V and 5 kHz respectively. IV. SAR ADC The SAR ADC is suitable for low-voltage low-power applications with relatively low sampling rate. A chargeredistribution DAC based SAR ADC is used in this design, as shown in Fig. 4. The reference voltages, VREF P and VREF N , set the full-scale voltage of the ADC as ±(VREF P –VREF N ). Therefore, the ADC full-scale can be controlled by switching to several preset reference voltages. With the adaptive control of the ADC full-scale voltage, the resolution requirement can be relaxed, which permits lower power for the ADC. Note that with the reduction of the full-scale voltage, the LSB value is also reduced. The minimum LSB should be sufficiently larger than the kT /C noise and other noise sources. In this design, a fully-differential array of capacitors is employed in the DAC; and the unit capacitor size is chosen so that the minimum full-scale voltage is ±0.5 V. The maximum −4 Input−Referred Noise [V/(Hz) 1/2 ] 10 −5 10 −6 10 −7 10 −8 10 −9 10 Fig. 5. Fig. 7. Chip microphotograph of the interface ASIC. 200 400 Frequency (Hz) 600 800 Measured noise performance of the signal conditioning front-end. 1 55 DNL(LSB) 60 Highest Gain & Bandwidth 50 45 Gain (dB) 0 0.6 0.2 −0.2 −0.6 40 −1 0 35 200 400 600 Code Bin 800 1000 200 400 600 Code Bin 800 1000 Lowest Gain & Bandwidth 1.5 30 1 INL(LSB) 25 20 15 0.5 0 −0.5 −1 10 −1 10 Fig. 6. 0 10 1 2 10 10 Frequency (Hz) 3 10 −1.5 0 4 10 Measured frequency response of the signal conditioning front-end. full-scale voltage of the ADC is ±1 V rail-to-rail. A major factor that limits the resolution of SAR ADC is the matching of large capacitor array; here the common-centroid layout is employed for capacitor matching. Meanwhile, unlike the comparator of pipeline ADC, the comparator used in SAR ADC has to provide full resolution. Considering the full-scale of the ADC is rail-to-rail and there are extra low-frequency noise and offset exist, the comparator is the most power consuming block in the SAR ADC design. Here a multistage comparator with both input and output offset-cancellation is employed [7]. Note that for the preamplifier of the comparator, a complementary input stage with both PMOS and NMOS input pairs is used. Simulation shows that the comparator is able to provide 14-bit resolution with offset up to 100 mV. V. M EASUREMENT R ESULTS The interface IC was fabricated in a 0.18-µm CMOS technology. Fig. 5 shows the microphotograph of the chip. 290 Fig. 8. Measured DNL and INL of the SAR ADC. The core area of the interface is 3.2mm×2.8mm, and most of silicon area is consumed by capacitors. The analog front-end including IA, BPF and PGA consumes 21 µW from a single 1-V supply. The measured frequency response of the analog front-end is shown in Fig. 6. It is shown that the gain is configurable from 31 dB to 52 dB. The bandwidth is configurable from 500 Hz to 4.3 kHz, which covers the spectrum of most biomedical signals. The measured noise performance is shown in Fig. 7, where the 50-Hz and 150-Hz spurs are due to the interference from power-line and environment. The input-referred noise (IRN) density is 95 √ nV/ Hz at 100 Hz, the integrated noise from 0.1 Hz to 200 Hz is 1.9 µVrms . The ADC operates up to 18 kS/s and consumes 15 µW from 1-V supply. The measured INL and DNL of the ADC are shown in Fig. 8. The DNL is within -1/+0.3 LSB and the INL is within -1.3/+0.8 LSB. As mentioned previously, the resolution requirement of the ADC is relaxed with the adaptive TABLE I P ERFORMANCE S UMMARY AND C OMPARISONS 0 Amplitude (dB) −20 Parameters −40 −60 This Work [1] [3] [2] [5] [4] Supply voltage (V) 1 3 3 ±1.5 1 3.3 FE Power (µW) 21 60 26 1455 <2.3 73 −80 −100 −120 0 Fig. 9. 200 400 600 Frequency (Hz) 800 1000 Measured FFT of the SAR ADC with a 827-Hz input. 1 Amplitude (V) 0.8 FE IRN (µVrms ) 1.9 1.1 0.53 0.86 2.7 6 FE CMRR (dB) 100 110 130 117 61 100 FE Configurable Yes Yes Yes No No No ADC Power (µW) 15 – – – <2.3 – ADC Resolution (b) 10 – – – 11 – ADC Rate (kS/s) <18 – – – 1 – ADC DNL (LSB) –1/+0.3 – – – ±1.5 – ADC INL (LSB) –1.3/+0.8 – – – ±2 – Core Area (mm2 ) 9 2 12 4.8 1 N.A. 0.6 0.4 has been relaxed with the adaptive full-scale range. The ADC exhibited less than ±1-LSB DNL and ±1.3-LSB INL. The whole interface consumed only 36 µW from a low supply voltage of 1 V, making it suitable for voltage and power constrained applications. 0.2 0 0 Fig. 10. 0.3 0.6 0.9 Time (s) 1.2 1.5 1.8 ACKNOWLEDGEMENT Extracted ECG signal measured with the interface ASIC. control of the full-scale voltage. At 2 kS/s, the output spectrum from a 827-Hz analog input is shown in Fig. 9. The SFDR is 64 dB and SNDR is 54 dB, resulting in the ENOB of 8.7 bit. Finally, the interface IC has been employed in a real ECG measurement scenario with Ag/AgCl electrodes. Fig. 10 shows the extracted ECG signals. It is shown that the noise and interference have been suppressed to a relatively low level as compared to the ECG waveform. The performance achieved in this design is compared with other state-of-the-art designs for biomedical applications. As shown in TABLE I, this is the first adaptive biomedical interface consisting of both front-end and ADC. VI. C ONCLUSIONS An adaptive interface IC has been demonstrated including a low-noise signal acquisition front-end and a SAR ADC. For better immunity to the common-mode noise and interference, the design employed fully-differential architecture in the entire analog signal processing path. Both the front-end and the ADC are digitally controllable, leading to an adaptive interface capable of a wide range of biomedical √ applications. The inputreferred noise density was 95 nV/ Hz and more than 100 dB CMRR was achieved. The resolution requirement of the ADC 291 The authors would like to thank Mr. Liu Haiqi, Mr. Darwin Sutomo David, Mr. Yu Rui, Mr. Koh Chin Wee, Mr. Teo Tee Hui, and many other colleagues for their generous assistance and valuable discussions. R EFERENCES [1] R. F. √ Yazicioglu, P. Merken, R. Puers, and C. V. Hoof, “A 60µW 60nV/ Hz readout front-end for portable biopotential acquisition systems,” in 2006 IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, Feb. 5–9, 2006, pp. 56–57. [2] K. A. Ng and P. K. Chan, “A CMOS analog front-end IC for portable EEG/ECG monitoring applications,” IEEE Trans. Circuits Syst.—I: Regular Papers, vol. 52, no. 11, pp. 2335–2347, Nov. 2005. [3] R. F. Yazicioglu, P. Merken, R. Puers, and C. V. Hoof, “Low-power low-noise 8-channel EEG front-end ASIC for ambulatory acquisition systems,” in 2006 European Solid-State Circuits Conf. (ESSCIRC), Montreux, Switzerland, Sep. 18–22, 2006, pp. 247–250. [4] M. Shojaei-Baghini, R. K. Lal, and D. K. Sharma, “A low-power and compact analog CMOS processing chip for portable ecg recorders,” in 2005 IEEE Asian Solid-State Circuits Conf. (ASSCC), Hsinchu, Taiwan, R.O.C., Nov. 1–3, 2005, pp. 473–476. [5] H. Wu and Y. P. Xu, “A 1V 2.3µW biomedical signal acquisition IC,” in 2006 IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, Feb. 5–9, 2006, pp. 58–59. [6] R. R. Harrison and C. Charles, “A low-power low-noise CMOS amplifier for neural recording applications,” IEEE J. Solid-State Circuits, vol. 38, no. 6, pp. 958–965, Jun. 2003. [7] B. Razavi and B. A. Wooley, “Design techniques for high-speed, highresolution comparators,” IEEE J. Solid-State Circuits, vol. 27, no. 12, pp. 1916–1926, Dec. 1992.