PACKAGE LIST

Evaluation board with ADCLK946 component installed

Applicable documents (schematic, layout)

GENERAL DESCRIPTION

This user guide describes how to set up and use the evaluation

board for the ADCLK946. The ADCLK946 data sheet should be

used in conjunction with this user guide.

The data sheet contains full technical details about the specifications and operation of this device.

The ADCLK946 is a very high performance clock fanout buffer.

The evaluation board is fabricated using a high quality Rogers

dielectric material. Transmission line paths are kept as close to

50 Ω as possible.

08668-101

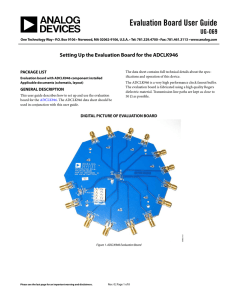

DIGITAL PICTURE OF EVALUATION BOARD

Figure 1. ADCLK946 Evaluation Board

www.BDTIC.com/ADI

TABLE OF CONTENTS

Package List ....................................................................................... 1

Recommended Board Setup ........................................................3

General Description ......................................................................... 1

Clock Outputs ................................................................................4

Digital Picture of Evaluation Board ............................................... 1

Evaluation Board Schematic and Artwork.....................................5

Revision History ............................................................................... 2

ESD Caution...................................................................................8

Evaluation Board Hardware ............................................................ 3

REVISION HISTORY

11/09—Revision 0: Initial Version

www.BDTIC.com/ADI

EVALUATION BOARD HARDWARE

RECOMMENDED BOARD SETUP

Table 1. Basic Equipment Required

The recommended setup for the ADCLK946 evaluation board

is shown in Figure 2. VCC is set to 3.3 V and VEE is set to GND.

Quantity

1

1

1

4

On the evaluation board, the clock input is set up for singleended-to-differential operation via the balun. In addition, series

capacitors in the path provide ac-coupled inputs to the

ADCLK946. The common-mode voltage for both inputs is

provided by tying VREF and VT together. This connection is made

with R13 installed at the factory.

Description

Single power supply

Signal source

High bandwidth oscilloscope

Matched high speed cables

The range of the peak-to-peak input voltage swing at CLK is

0.2 V p-p to 1.7 V p-p. Note that output jitter performance is

degraded by an input slew rate, as shown in the ADCLK946

data sheet.

POWER SUPPLY

+3.3V

GND

VCC

CH 1

CLK

CLK

VEE

ADCLK946

Qx

EVALUATION

BOARD

OSCILLOSCOPE

Qx

VREF

CH 2

VT

Figure 2. Recommended Setup for Device Evaluation

www.BDTIC.com/ADI

08668-002

CLOCK

SOURCE

GND

CLOCK OUTPUTS

The ADCLK946 has six differential outputs. All differential

clock outputs on the evaluation board are biased to GND via

200 Ω and ac-coupled to the SMAs. From the SMAs, use

matched 50 Ω coaxial cables into the oscilloscope for

evaluation. See the evaluation board schematic in Figure 4 for

more details.

ADCLK946

Table 2. Power Connections via P1

Label

GND

VCC

VEE

ADCLK946

Connect to GND

Connect to 3.3 V

Connect to GND

LVPECL

Q0

Q0

VREF

VT

REFERENCE

Q1

Q1

Q2

CLK

Q2

CLK

Q3

Q3

Q4

Q4

08668-001

Q5

Q5

Figure 3. ADCLK946 1:6 Clock/Data Buffer Block Diagram

www.BDTIC.com/ADI

GND

GND

CLK

J15 CLKB

J14

0

GND

R07

R09

DNI

0

4

3

MABA-007159-000000

SEC

T2

PRI

0

1

DNI

5

R08

J0

GND

GND

J10 OUT5

GND

J11 OUT5B

GND

GND

OUT0

C2

2

.1UF

.1UF

CLKB

.1UF

C4

.1UF

C3

C04

C03

CLK

.1UF

1

50 OHMS

50 OHMS

50 OHMS

50 OHMS

50 OHMS

VEE

CLK

CLKB

VREF

VT

VEE

OUT5

OUT5B

1

2

3

VREF 4

5

VT

VEE 6

VEE

OUT0

R4

VEE

VCC

VEE

200

VEE

R5

200

Q5B Q4B

VEE Q5

Q4VEE

ADCLK946

CP-24-2

VCC Q0 Q1 VEE

Q0B Q1B

VEE

VEE

VEE

VCC

Q2

Q2B

Q3

Q3B

VCC

VEE

VEE

R9

.1UF

VEE

VEE

VEE

18 VCC

17

16

15

14

13 VCC

OUT4B

OUT4

50 OHMS

200

R14

VEE

OUT1B

OUT1

VEE

R15

50 OHMS

C9

VEE

50 OHMS

50 OHMS

VEE

OUT2B

OUT2

.1UF

C12

.1UF

C11

50 OHMS

50 OHMS

50 OHMS

50 OHMS

.1UF

C10

.1UF

J2

.1UF

C16

1 2

.1UF

C15

J8

.1UF

C18

GND

GND

OUT2B

GND

OUT2

GND

OUT3B

GND

OUT3

J5

J4

J7

J6

LABEL "VCC (3.3V)"

LABEL "VEE (GND)"

.1UF

C17

OUT4B J9

GND

OUT4

OUT3B

OUT3

GND

OUT1B J3

GND

OUT1

POWER

P1

ORDER WEILAND 25.600.5453.0 PLUG

SAME AS ADCLK954 ENGR BRD

TP1

VT

VREF

1

VT

VEE

VCC

GND

VEE

BYPASS CAPACITORS (SUPPLY)

GND

VCC

BYPASS CAPACITORS (DUT)

VEE

STITCHING RESISTORS (O OHM)

GND

C31

C32

49.9

VEE

0

.1UF

10UF

R11

R10

R12

R44

GND

DNI

1

2

3

4

VCC

GND

R13

100

49.9

Z5.531.3425.0

C34

C33

OUT0B

PAD

VEE

R1

GND

VEE

BYPASS CAPACITORS

VT

VREF

R46

200

200

0

.1UF

10UF

R3

R2

200

R45

50 OHMS

C36

200

R16

C35

C5

0

.1UF

C41

24

23

22

21

20

19

7

8

9

10

11

12

R8

R47

C1

2

.1UF

R43

0

C39

1

R48

J1 OUT0B

.1UF

C6

200

200

200

www.BDTIC.com/ADI

R6

Figure 4. ADCLK946 Evaluation Board Schematic

200

R17

200

0

.1UF

C37

10UF

0

.1UF

0

.1UF

C40

50 OHMS => SINGLE ENDED

EVALUATION BOARD SCHEMATIC AND ARTWORK

08668-004

.1UF

08668-005

08668-006

Figure 5. Top Trace Layer

Figure 6. Ground Plane Layer

www.BDTIC.com/ADI

08668-007

08668-008

Figure 7. VCC and VEE Power Plane Layer

Figure 8. Bottom Trace Layer

www.BDTIC.com/ADI

NOTES

ESD CAUTION

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards are supplied “as is” and without warranties of any kind, express,

implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under

any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the

right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not

authorized to be used in life support devices or systems.

©2009 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

UG08668-0-11/09(0)

www.BDTIC.com/ADI