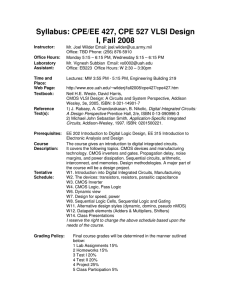

Digital Integrated Circuits

advertisement

Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits – EECS 312 Travel http://ziyang.eecs.umich.edu/∼dickrp/eecs312/ Where were your teacher and teaching assistant? Teacher: Office: Email: Phone: Cellphone: Robert Dick 2417-G EECS dickrp@eecs.umich.edu 734–763–3329 847–530–1824 HW engineers GSI: Email: Myung-Chul Kim mckima@umich.edu International Conference on Computer-Aided Design. Mr. Kim won the best-paper award at this top conference. I gave a tutorial on integrated circuit and embedded system reliability. Typical Current Draw 1 sec Heartbeat 30 beats per sample SW engineers My student gave a talk on dynamic control of VDD to minimize energy consumption while meeting performance requirements. 10 Sampling and Radio Transmission 9 - 15 mA 9 8 Current (mA) 7 Radio Receive for Mesh Maintenance 2 - 6 mA Heartbeat 1 - 2 mA 6 Low Power Sleep 0.030 - 0.050 mA 5 4 If curious, you can out about the research on the course website, at the “Excuse for absence” link. 3 2 1 0 200 220 240 260 280 300 Time (seconds) 14 CMOS IBM ES9000 Power density (Watts/cm2) 12 Prescott Jayhawk(dual) Bipolar 10 T-Rex Mckinley Squadrons Fujitsu VP2000 8 IBM GP IBM 3090S IBM RY5 NTT IBM Z9 6 Fujitsu M-780 Pentium 4 IBM RY7 Pulsar 4 IBM 3090 2 Vacuum 0 1950 IBM 360 IBM RY6 CDC Cyber 205 IBM 4381 IBM 3081 Fujitsu M380 IBM 3033 IBM 370 IBM RY4 Apache Merced Pentium II(DSIP) 1960 1970 1980 1990 2000 2010 Year of announcement 2 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Non-idealities DCVSL Dynamic CMOS Homework Midterm exam 2 Homework 3 Requested times for midterm exam. Was anybody unable to get help they needed on Homework 3? 30 November or 2 December. If so will not penalize assignments handed in by Friday. Received two replies that conflict. However, Lab 4 will be assigned today. Coin flip. 3 Digital Integrated Circuits Robert Dick Digital Integrated Circuits 4 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Lab 4 Review What is the purpose of a restorer in pass transistor logic? What happens if the restorer MOSFET is too wide? What happens if the restorer MOSFET is too narrow? What are the advantages of dynamic logic? Derive and explain. 5 Robert Dick Digital Integrated Circuits What are the disadvantages of dynamic logic? 6 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Examples Miller effect f (a) = a. f (a) = a If VD switches in the opposite direction of VG , the effect of CGD is doubled. f (a, b) = ab f (a, b) = ab (Check Figure 6-33 in J. Rabaey, A. Chandrakasan, and B. Nikolic. Digital Integrated Circuits: A Design Perspective. Prentice-Hall, second edition, 2003!) Consider an inverter. Model by using a 2CGD capacitor to ground. f (a, b, c) = ab + bc (try both ways). Derive and explain. 7 Robert Dick Digital Integrated Circuits 9 Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Non-idealities DCVSL Dynamic CMOS Homework Stack effect Dynamic hazards Potential for two or more spurious transitions before intended transition VDD A B Results from uneven path delays in some multi-level circuits Each series transistor drops the voltage seen by the next transistor. Z 1 VT = TT 0 + p p γ |−2φF + VSB | − |2φF | 0 0 1 1 Dy n a m ic VTn2 p= VTn0 + p |2φF + Vint | − |2φF | γ VSS 0 10 Robert Dick Digital Integrated Circuits 11 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework 0 1 G1 S lo w G3 1 01 1 0 1 0 Digital Integrated Circuits Eliminating dynamic hazards 1 G2 h a z a rd s Non-idealities DCVSL Dynamic CMOS Homework Dynamic hazards 0 1 1 Some approaches allow preservation of multi-level structure Quite complicated to apply 1 01 0 1 0 Simpler solution – Convert to two-level implementation G5 0 1 0 G4 1 0 V e ry s lo w 12 Robert Dick Digital Integrated Circuits 13 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Static hazards Problems with glitches Still have static hazards Potential for transient change of output to incorrect value 1 1 These transitions result in incorrect output values at some times Also result in uselessly charging and discharging wire and gate capacitances through wire, gate, and channel resistances S t a t ic 1 − h a z a rd 0 Increase power consumption 1 S t a t ic 0 14 0 Robert Dick 0 − h a z a rd Digital Integrated Circuits 15 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Non-idealities DCVSL Dynamic CMOS Homework Glitches increase power consumption VDD Digital Integrated Circuits Detecting hazards VDD The observable effect of a hazard is a glitch 1 A B VSS A circuit that might exhibit a glitch has a hazard Whether or not a hazard is observed as a glitch depends on relative gate delays VSS Relative gate delays change depending on a number of factors – Conditions during fabrication, temperature, age, etc. Best to use abstract reasoning to determine whether hazards might be observed in practice, under some conditions 16 Robert Dick Digital Integrated Circuits 17 Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Non-idealities DCVSL Dynamic CMOS Homework Eliminating static hazards Where do static hazards really come from? Ensure that the function has a term maintaining a 0 output for all 0→0 transitions. Static-0: A A Static-1: A + A Assume SOP form has no product terms containing a variable in complemented and uncomplemented forms Ensure that the function has a term maintaining a 1 output for all 1→1 transitions. There are precisely defined algorithms for this, but they build on a knowledge of logic minimization. 18 Robert Dick Digital Integrated Circuits Reasonable assumption, if true, drop product term 19 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Where do static hazards really come from? Living with hazards Assume POS form has no sum terms containing a variable in complemented and uncomplemented forms Sometimes hazards can be tolerated Reasonable assumption, if true, drop sum term Combinational logic whose outputs aren’t observed at all times Assume only one input switches at a time Synchronous systems Conclusion: SOP has no 0-hazards and POS has no 1-hazards Systems without tight power consumption limits In other words, if you are doing two-level design, you need not analyze the other form for hazards 20 Robert Dick Digital Integrated Circuits 21 Non-idealities DCVSL Dynamic CMOS Homework Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Differential cascode voltage switch logic 23 Robert Dick Digital Integrated Circuits Differential cascode voltage switch logic example 24 Non-idealities DCVSL Dynamic CMOS Homework Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Differential cascode voltage switch logic response Static vs. dynamic logic Static logic relies only on steady-state behavior of system. Eventually the output converges to a correct result. Dynamic logic relies on transient behavior and is sensitive to timing. Reliable design is generally trickier. Why use it? Static logic requires (kP + kN ) transistors for k-input gate. Dynamic logic requires kN + 2 transistors for k-input gate. 25 Robert Dick Digital Integrated Circuits 27 Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Non-idealities DCVSL Dynamic CMOS Homework Dynamic logic Dynamic logic example Two-phase operation. 28 Robert Dick Digital Integrated Circuits 29 Robert Dick Non-idealities DCVSL Dynamic CMOS Homework Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Dynamic logic operating principles I Dynamic logic operating principles II 1 Can only discharge output node once per clock period. 2 Inputs must make only one transition during evaluation. 3 Output can be in the high impedance state during and after evaluation. 4 Logic function is implemented by the pull-down network only. 5 Requires only kN + 2 transistors. 6 Full swing outputs. 11 VM = VIH = VIL = VTN so noise margin is low. 7 Non-ratioed - sizing of the devices does not affect the logic levels. 12 Needs precharge and evaluation cycle. 8 Reduced load capacitance due to lower input capacitance. 9 Reduced load capacitance due to smaller output loading. no Isc, so all the current provided by PDN goes into discharging CL. 30 Robert Dick Digital Integrated Circuits 10 Power consumption usually higher than static CMOS. Good: No static current. Good: No glitching. Bad: Higher transition probabilities. Bad: More load on clock distribution network. 31 Non-idealities DCVSL Dynamic CMOS Homework Robert Dick Digital Integrated Circuits Non-idealities DCVSL Dynamic CMOS Homework Upcoming topics Homework assignment 11 November, Thursday: Homework 3. 16 November, Tuesday: Read Sections 7.1, 7.2.1–7.2.3 in J. Rabaey, A. Chandrakasan, and B. Nikolic. Digital Integrated Circuits: A Design Perspective. Prentice-Hall, second edition, 2003. Example problems on recently covered material. Latches and flip-flops. 22 November, Thursday: Lab 4. 32 Robert Dick Special topic: ALU design Daniel Clifford and Ike Anyanetu Digital Integrated Circuits 34 Robert Dick Digital Integrated Circuits