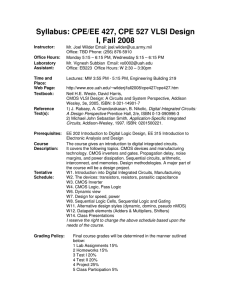

EECE 412 – Digital Integrated Circuits

advertisement

EECE 412 – Digital Integrated Circuits Catalog description: Introduction to digital electronic circuits. Models, current equations and parasitics of CMOS transistors for digital design. Study of CMOS inverter and logic gates, including analysis, design, simulation, layout and verification. Advanced circuit styles. Sequential circuits. Advanced topics: semiconductor memories, power grid, clocking strategies, datapath building blocks, deep-submicron design issues, interconnect. Credit hours: 3 credits Required or elective: Technical elective for undergraduate students (EECE 412). Open to graduate students with extra load (EECE 612). Prerequisites: By course: EECE 310 Electronics I; EECE 320 Digital Systems Design, By topic: Basic semiconductor devices, electronic circuits; Basic logic design. Textbook(s) and/or required materials: J. Rabaey, A. Chandrakasan, and B. Nikolic: “Digital Integrated Circuits: A Design Perspective”, 2th Edition, Prentice Hall, 2003. References: − N. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective, Addison-Wesley, 2004. − D. Hodges, R. Saleh, and H. Jackson, Analysis and design of Digital Integrated Circuits, 3rd Edition, McGraw-Hill, 2003. − S. Kang and Y. Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, 3rd Edition, McGraw-Hill, 2003. − N. Weste and K. Eshraghian, Principles of CMOS VLSI Design, Addison-Wesley, 1993. Computer usage: HSPICE circuit simulator; Cadence design tools Course Objectives The objectives of this course are to: To give students an introduction to the fundamentals of digital integrated circuits and expose them to examples of applications. To give students the ability to analyze, design, and optimize digital circuits with respect to different quality metrics: cost, speed, power dissipation, and reliability. To give students the basic background to go through a complete digital design cycle: analysis, design, simulation, layout and verification. Course Topics No. Subjects covered 1 Introduction: Issues in digital design 2 MOS transistor theory 3 The CMOS inverter: VTC, Delay 4 Power and energy 5 Combinational logic structures 6 Sequential logic gates 7 Logic design styles 8 Interconnect: R, L and C 9 Timing 10 Arithmetic building blocks 11 Memories and array structures 12 Design methodologies Correlates to program objectives 1,2,3 1,2,3, and 4 1,2,3, and 4 50 min. lectures 2 4 6 3 4 4 4 3 3 4 3 2 Course Learning Outcomes At the end of the course, students should be able to: Understand how CAD models make the link between technology and digital design. Assess the quality metrics of a digital design. Understand the impact of technology scaling. Understand the basic operation of MOS transistors, current equations, and parasitics. Know how to determine the VTC of a CMOS inverter and compute its noise margins. Understand the concepts of propagation delay, power consumption of CMOS ICs. Know how to design a CMOS inverter that meets certain delay and power specifications. Know how to analyze and design complex logic gates in standard CMOS technology, and compute their delay and power consumption. Know how to draw the layout of complex logic gates using a CAD tool. Know the method of Logical Effort. Be able to analyze and design static sequential circuits and understand basic clocking issues Know how to design arithmetic circuits. Know the basics of semiconductor memories Understand the impact of interconnect parasitics on circuit performance and signal integrity. Have basic skills needed to design digital integrated systems. Correlates to program outcomes* H M L (a),(b),(c), (e),(j),(k), (h) (f) (n) (a),(b),(c), (m),(j), (e),(k),(n) (o) (a),(b),(c), (e),(j),(k), (h),(o) (n) (a),(b),(k), (m) (n) (a),(b),(k), (m) (n) (a),(b),(k), (m) (n) (a),(b),(e), (m) (c) (k),(n) (a),(b),(e), (k),(n) (a),(b),(e), (k),(n) (a),(e),(k), (n) (a),(e),(k), (n) (a),(e),(k), (n) (a),(e),(n) (a),(b),(e), (k),(n) (a),(c),(e), (k),(n) (m) (c) (d) (m) (c) (m) (c) (c), (o) (h) (m) (c) (g),(o) * H: High correlation, M: Medium correlation, L: Low correlation Class/laboratory schedule: Two 90-minute lectures per week. Use of computer lab is needed for working on the assignments and projects. Evaluation methods 1. Assignments 2. Quizzes 3. Project 4. Final Exam 10% 40% 15% 35% Professional component Engineering topics: 90% General education: 0% Mathematics and basic sciences: 10% Person(s) who prepared this description and date of preparation Mohammad Mansour, January 2009 Date of last revision January 2009