Broadband Microwave Integrated Circuits for Voltage Standard

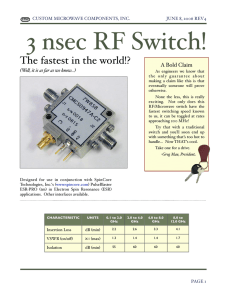

advertisement