A Control Strategy for Unified Power Quality Conditioner

advertisement

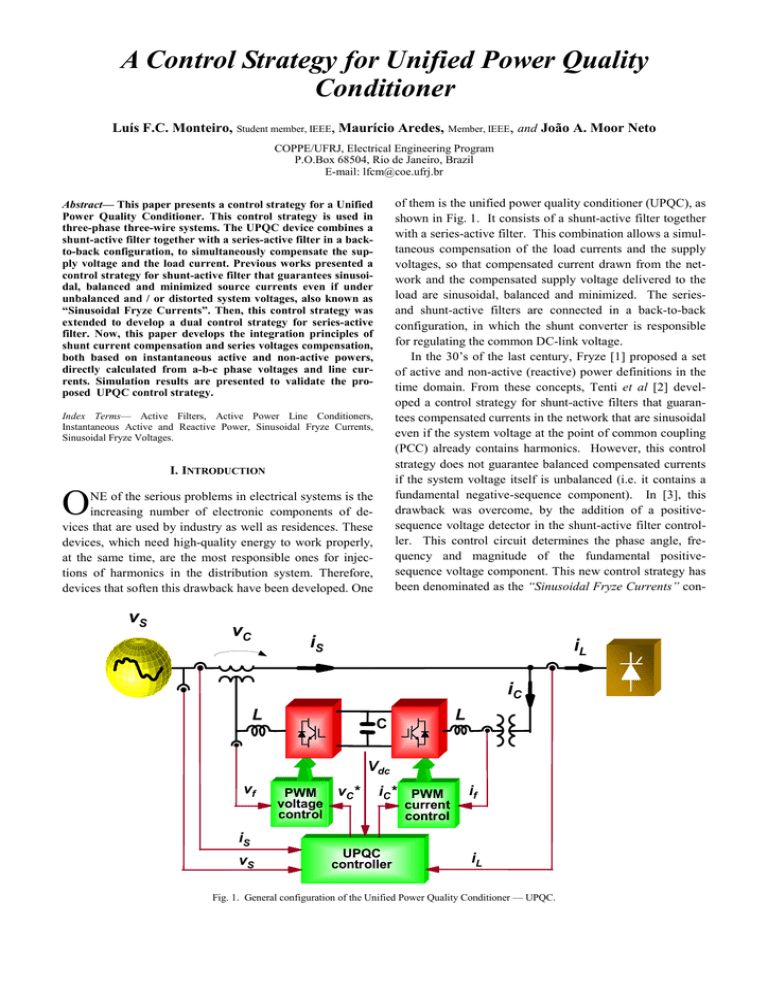

A Control Strategy for Unified Power Quality Conditioner Luís F.C. Monteiro, Student member, IEEE, Maurício Aredes, Member, IEEE, and João A. Moor Neto COPPE/UFRJ, Electrical Engineering Program P.O.Box 68504, Rio de Janeiro, Brazil E-mail: lfcm@coe.ufrj.br of them is the unified power quality conditioner (UPQC), as shown in Fig. 1. It consists of a shunt-active filter together with a series-active filter. This combination allows a simultaneous compensation of the load currents and the supply voltages, so that compensated current drawn from the network and the compensated supply voltage delivered to the load are sinusoidal, balanced and minimized. The seriesand shunt-active filters are connected in a back-to-back configuration, in which the shunt converter is responsible for regulating the common DC-link voltage. In the 30’s of the last century, Fryze [1] proposed a set of active and non-active (reactive) power definitions in the time domain. From these concepts, Tenti et al [2] developed a control strategy for shunt-active filters that guarantees compensated currents in the network that are sinusoidal even if the system voltage at the point of common coupling (PCC) already contains harmonics. However, this control strategy does not guarantee balanced compensated currents if the system voltage itself is unbalanced (i.e. it contains a fundamental negative-sequence component). In [3], this drawback was overcome, by the addition of a positivesequence voltage detector in the shunt-active filter controller. This control circuit determines the phase angle, frequency and magnitude of the fundamental positivesequence voltage component. This new control strategy has been denominated as the “Sinusoidal Fryze Currents” con- Abstract— This paper presents a control strategy for a Unified Power Quality Conditioner. This control strategy is used in three-phase three-wire systems. The UPQC device combines a shunt-active filter together with a series-active filter in a backto-back configuration, to simultaneously compensate the supply voltage and the load current. Previous works presented a control strategy for shunt-active filter that guarantees sinusoidal, balanced and minimized source currents even if under unbalanced and / or distorted system voltages, also known as “Sinusoidal Fryze Currents”. Then, this control strategy was extended to develop a dual control strategy for series-active filter. Now, this paper develops the integration principles of shunt current compensation and series voltages compensation, both based on instantaneous active and non-active powers, directly calculated from a-b-c phase voltages and line currents. Simulation results are presented to validate the proposed UPQC control strategy. Index Terms— Active Filters, Active Power Line Conditioners, Instantaneous Active and Reactive Power, Sinusoidal Fryze Currents, Sinusoidal Fryze Voltages. I. INTRODUCTION O NE of the serious problems in electrical systems is the increasing number of electronic components of devices that are used by industry as well as residences. These devices, which need high-quality energy to work properly, at the same time, are the most responsible ones for injections of harmonics in the distribution system. Therefore, devices that soften this drawback have been developed. One vS vC iS iL iC L L C Vdc vf PWM voltage control vC* iC* PWM current control if iS vS UPQC controller iL Fig. 1. General configuration of the Unified Power Quality Conditioner — UPQC. trol strategy. This work exploits the use of that positive-sequence voltage detector to develop a new control strategy for series-active filter. It is based on a dual minimization method for voltage compensation, together with a synchronizing circuit (PLL circuit). The synchronizing circuit is responsible to detect the fundamental frequency, as well as the phase angle of the positive-sequence voltage component. The dual minimization method is responsible to accurately determine the magnitude of this voltage component. This control strategy is denominated here as the “Sinusoidal Fryze Voltages” control strategy. Further, this paper presents the integration the “Sinusoidal Fryze Currents” and the “Sinusoidal Fryze Voltages” control strategies into an UPQC controller. Additionally, the proposed UPQC controller includes an algorithm that provides damping in harmonic voltage propagation and hinders load harmonic currents to flow into the network. A complete model of the UPQC approach is implemented in a digital simulator and results is presented to validate the proposed control strategy. A. The Positive-Sequence Voltage Detector (V+1) A positive-sequence voltage detector [V+1 voltagedetector block in Fig. 2(a)] in terms of "minimized voltages" is developed. A dual principle for voltage minimization is employed, together with a phase-lockedloop circuit (PLL circuit), as shown in Fig. 3. The used PLL circuit is detailed in the next section. In fact, this dual principle of voltage minimization is used here for extracting "instantaneously" the fundamental positive-sequence component ( V+1 in phasor notation, or va1, vb1, vc1 as instantaneous values, as the outputs of Fig. 3) from a generic three-phase voltage. The distorted and unbalanced voltages vas, vbs, vcs of the power supply are measured and given as inputs to the PLL circuit. As shown in the next section, it determines the signals ia1, ib1, ic1, which are in phase with the fundamental positive-sequence component ( V+1 ) contained in vas, vbs, vcs. Thus, only the magnitude of V+1 is missing. The fundamental characteristic of the used PLL allows the use of a dual expression for determining active voltages in the form vap ia1 vas ia1 + vbs ib1 + vcs ic1 = v bp 2 2 2 ib1 + + i i i a 1 b 1 c 1 vcp ic1 II. THE UPQC CONTROLLER Fig. 2 shows the complete functional block diagram of the UPQC controller. The part shown in Fig. 2(a) is responsible to determine the compensating current references for PWM control of the UPQC shunt converter, whereas the other part shown in Fig. 2(b) generates the compensating voltage references for PWM series converter. Next, each functional block of Fig. 2 will be detailed. 1 ial ibl icl 3 2 vas vbs vcs vDC (a) va1 vb1 vc1 V+1 Voltage Detector DC Voltage Regulator iac Current Minimization as an artifice to extract the V+1 component from vas, vbs, vcs. The reason is that the signals ia1, ib1, ic1 are three symmetric sinus functions with unity amplitude, which correspond to an auxiliary fundamental positive-sequence current I+1 that is in phase with V+1 . Hence, the average value of the "three-phase instantaneous power", 3V+1I+1cosφ, is maximum (would be zero if V+1 and I+1 are orthogonal), and the average signal Rbar in Fig. 3 comprises the total amplitude of V+1 . Therefore, it is possible to guarantee that the signals va1, vb1, vc1 are sinusoidal and have the same magnitude and phase angle of the fundamental positive-sequence component of the measured system voltage. ibc ia1vas + ib1vbs + ic1vcs ia21 + ib21 + ic21 icc Gloss 2 4 ias ibs 2 ics 3 va1 vb1 vc1 vas vbs vcs 5 Damping Controller vah vbh vch Compensating Voltages calculation (1) vac vbc vas vbs vcs Low Pass Filter 5th Order Butterworth Cut freq. = 50 Hz Rbar ia1 PLL Synchronizing Circuit R ib1 ic1 3 vcc (b) Fig. 2. The functional block diagram of the UPQC controller for (a) shunt UPQC converter and (b) series UPQC converter. va1 = Rbar ⋅ ia1 vb1 = Rbar ⋅ ib1 v = R ⋅ i bar c1 c1 Fig. 3. The V+1 voltage detector diagram block va1 vb1 vc1 1) The PLL Circuit C. Current Minimization The used PLL circuit (Fig. 4) can operate satisfactorily under high distorted and unbalanced system voltages. The inputs are vab = vas – vbs and vcb = vcs – vbs. The outputs of the PLL circuit are ia1, ib1, ic1. The algorithm is based on the instantaneous active three-phase power expression p3φ = vabia + vcbic. The current feedback signals ia(wt) = sin(wt) and ic(wt) = sin(wt – 2π/3) are built up by the PLL circuit, just using the time integral of output ω of the PI-Controller. Note that they have unity amplitude and ic(wt) leads 120o ia(wt). Thus, they represent a feedback from a positivesequence component at frequencyω. The PLL circuit can reach a stable point of operation only if the input p3φ of the PI-Controller has a zero average value ( p3φ = 0 ) and has p3φ minimized low-frequency oscillating portions in ~ ( p3φ = p3φ + ~ p3φ ). Once the circuit is stabilized, the average value of p3φ is zero and, with this, the phase angle of the positive-sequence system voltage at fundamental frequency is reached. At this condition, the auxiliary currents ia(ωt) and ic(ωt) = sin(ωt – 2π/3), becomes orthogonal to the fundamental positive-sequence component of the measured voltages vas, vcs respectively. Therefore, ia1(ωt) = sin(ωt – π/2) is in phase with the fundamental positive-sequence component contained in vas. Fig. 6 shows in details that functional block named "Current Minimization" in Fig. 2(a). It determines the instantaneous compensating current references, which should be synthesized by the shunt PWM converter of the UPQC. It has the same kernel as the Generalized Fryze Currents methods widely used, like in [4], [5] and [6]. The inputs of the controller are the load currents ia1, ib1, ic1, the control voltages va1, vb1, vc1 determined by the V+1 detector, and the DC voltage regulator signal Gloss. The conductance G is determined in Fig. 6 corresponds to the active current of the load. In other words, it comprises all current components that can produce active power with the voltages va1, vb1, vc1. A low-pass fifth order Butterworth filter is used to extract the average value of G, which is denominated as Gbar. Now, since va1, vb1, vc1 comprises only the VD+1 component, Gbar must correspond to the active portion of the fundamental positive-sequence component ( I+1 ) of the load current. The control signal Gcontrol is the sum of Gbar and Gloss, which, together with the control voltages va1, vb1, vc1, are used to determine the currents iaw, ibw, icw. These control signals are pure sinusoidal waves in phase with va1, vb1, vc1 and include the magnitude of the positive-sequence load current (proportional to Gbar) and the active current (proportional to Gloss) that is necessary to compensate for losses in the UPQC. Since the shunt active filter of the UPQC compensates the difference between the calculated active current and the measured load current, it is possible to guarantee that the B. The DC voltage regulator The dc voltage regulator is used to generate a control signal Gloss, as shown in Fig. 2(a). This signal forces the shunt active filter to draw additional active current from the network, to compensate for losses in the power circuit of the UPQC. Additionally, it corrects dc voltage variations caused by abnormal operation and transient compensation errors. This point is clarified later, where simulation results are discussed. Fig. 5 shows the dc voltage regulator circuit. It consists only of a PI-Controller [G(s) = Kp + KI/s], where, for normalized inputs, Kp = 0.50 and KI = 80. i a(ω t) vab X p3φ Σ vcb ωt sin( ω t ) PI-Controller ω 1 s sin( ω t – π/2) sin( ω t – π/2 – 2 π/3) X sin( ω t + 2 π/3) i c (ω t) sin( ω t – π/2 + 2 π/3) va1ial + vb1ibl + vc1icl va21 + vb21 + vc21 Low Pass Filter 5th Order Butterworth Cut freq. = 50 Hz G 1 va1 vb1 vc1 i a1 Gbar Gcontrol Gloss Σ i b1 3 1 ial i c1 ibl icl iaw Fig. 4: The Synchronizing Circuit – PLL Circuit. VDC_ref ial ibl icl + Σ low-pass filter PI – controller Gloss iaw = Gcontrol ⋅ va1 ibw = Gcontrol ⋅ vb1 i = G control ⋅ vc1 cw ibw icw iac = iaw − ial ibc = ibw − ibl i = i − i cc cw cl – iac vDC Fig. 5: The DC voltage regulator. ibc Fig. 6. The Current Minimization control algorithm. icc compensated currents ias, ibs, ics drawn from the network are always sinusoidal, balanced and in phase with the positivesequence system voltages. This characteristic represents a great improvement done at the “Generalized Fryze Currents” control strategy. D. The Damping Control Algorithm In a UPQC configuration, instability problems due to resonance phenomena may occur. In order to enhance the overall system stability, an auxiliary circuit can be added to the controller of the series active filter. The basic idea consists in increasing harmonic damping, as a series resistance, but effective only in harmonic frequencies, others than the fundamental one. This damping principle was first proposed by Peng [7], in terms of components defined in the pq Theory and used by Aredes [8] and Fujita [9]. The damping control algorithm, now developed in terms of abc variables (in the phase mode), can be seen in Fig. 7. The inputs to the damping circuit are the source currents ias, ibs, ics (compensated currents), which are flowing through the series transformers of the UPQC, and the voltages determined by the V+1 voltage detector va1, vb1, vc1. The active and non-active instantaneous powers are determined by using the equations (2) and (3); P = va1ias + vb1ibs + vc1ics ; Q = vaqias + vbqibs + vcqics va1 3 va1ias + vb1ibs + vc1ics va21 + vb21 + vc21 vb1 vc1 G (2) High Pass Filter Butterworth 5th order Cut off freq. = = 50 Hz Gcomp High Pass Filter Butterworth 5th order Cut off freq. = = 50 Hz Bcomp 7 4 ias ibs vaq = (vb1 − vc1 ) / 3 vbq = (vc1 − va1 ) / 3 vcq = (va1 − vb1 ) / 3 ics 6 vcq vbq vaq vaq ias + vbq ibs + vcq ics 2 vaq + vbq2 + vcq2 va1 vb1 vc1 Gcomp 7 Bcomp 8 B 5 iah = iap + iaq ibh = ibp + ibq ich = icp + icq iaq = Bcomp .vaq ibq = Bcomp .vbq icq = Bcomp .vcq vaq vbq vcq iah ibh ich vaq = (vb1 − vc1 ) / 3 ; (3) vbq = (vc1 − va1 ) / 3 vcq = (va1 − vb1 ) / 3 Note that the voltages vaq, vbq, vcq are achieved from the fundamental positive-sequence voltages va1, vb1, vc1. Therefore, it is possible to guarantee that the voltages vaq, vbq, vcq are still sinusoidal and lag 90º the voltages va1, vb1, vc1, respectively. A conductance G and a susceptance B are determined from the calculated active and non-active instantaneous powers, as shown in Fig. 7. Then, high-pass, fifth order Butterworth filters are used to extract the oscillating parts of that conductance and susceptance. The auxiliary currents iap, ibp, icp and iaq, ibq, icq, are determined as follows: iap = Gosc ⋅ va1 ; (4) ibp = Gosc ⋅ vb1 icp = Gosc ⋅ vc1 i aq = Bosc ⋅ v aq ibq = Bosc ⋅ vbq icq = Bosc ⋅ vcq . (5) Damping signals (harmonic components still present in the source currents) are determined as described in (6). iah = iaq + iap . (6) ibh = ibq + ibp ich = icq + icp Finally, the multiplication between the damping signals iah, ibh, ich and a gain K determines the damping voltages vah, vbh, vch. that will be added to the compensating voltage references of the series active filter of the UPQC, as will be explained in the next section. Thus, the gain K acts as a harmonic resistance to damp resonance phenomena. E. Compensating Voltages Calculation 8 3 iap = Gcomp .va1 ibp = Gcomp .vb1 icp = Gcomp .vc1 where, vah vbh vch vah = K ⋅ iah vbh = K ⋅ ibh v = K ⋅ i ch ch Gain K 6 Fig. 7. Damping control algorithm in terms of abc variables. The block diagram that determines the compensating voltages vac, vbc, vcc [Fig. 2(b)], which is synthesized by the series PWM converter, is shown in Fig. 8. The inputs are the control voltages determined by the V+1 voltage detector: va1, vb1, vc1, the source voltages: vas, vbs, vcs, and the damping voltages: vah, vbh, vch. The compensating voltage are: vac = va1 − (vas + vah ) vbc = vb1 − (vbs + vbh ) v = v − (v + v ) c1 cs ch cc . (7) Ideally, the compensated voltages delivered to the critical load will comprise only the fundamental positive-sequence component (va1, vb1, vc1) of the supply voltage vS. The damping voltages will improve stability and provide harmonic isolation. 5 3 va1 vb1 vc1 vah vbh ial 0.4 0.2 0.0 -0.02 -0.04 vch iac 0.4 vac = va1 − (vas + vha ) vbc = vb1 − (vbs + vhb ) v = v − (v + v ) c1 cs hc cc vas vbs vac vbc vcc 0.2 0.0 -0.02 -0.04 ias 0.4 0.2 0.0 -0.02 -0.04 vcs 0.10 2 0.14 0.16 0.18 0.20 0.22 0.24 0.26 0.28 Fig. 9: Load current, current of the shunt active filter and source current. Fig. 8. Compensating voltages calculation As conclusion, the proposed UPQC control strategy provides compensated voltages and currents that are sinusoidal, balanced and minimized (in phase). Therefore, the power factor is ideal, the voltages delivered to the load are sinusoidal and balanced, and it is possible to guarantee that the source currents will be sinusoidal, balanced and minimized even if under unbalanced and / or distorted system voltages. III. SIMULATION RESULTS A test case was mounted to investigate the performance of the UPQC filter through digital simulations, in the Saber DesignerTM. Per unit (pu) quantities cannot be used directly in this simulator. Thus, 1V (phase to ground) and 1A (line current) were used as the basis of the system. A balanced, 1V, three-phase, voltage source is used. A three-phase sixpulse thyristor rectifier, with 0.2 A DC-current (20%), is used as a non-linear load. The shunt-active filter and the series-active filter start its operation in 0.2s. The total simulation time is 0.8s. The thyristor rectifier is connected at t = 0.1s. An inductor and a resistor, whose values correspond to 0.1 % of the system base impedance, compose the source impedance. In this case, the short-circuit power at the load terminal is equal to 10 p.u. The small high-pass filters to mitigate switching frequency harmonics at the series and shunt PWM converters are R=0.6 Ω and C = 170 µF. Although it seams a high capacitor, it corresponds to 5% of the system baseimpedance. A capacitor of 2400µF is used at the DC link of the UPQC. The reference voltage is equal to 4.5 V. To give an idea of the capacitor’s dimension, the unit capacitor constant (UCC) is calculated, by the following equation: 1 1 ⋅ C ⋅V 2 ⋅ 2400 µ ⋅ (4.5) 2 = 2 = 8.1ms UCC = 2 P 3 ⋅ 1 ⋅1 0.12 that the source currents take to reach the steady state is pretty small. This demonstrates that the proportional and integral gains of the DC voltage regulator are well dimensioned. Fig. 10 shows the supply voltage vas (uncompensated, left side of the UPQC), the compensating voltage vac of the UPQC, and compensated voltage vaw, delivered to the critical load, before and after the start of the series active filter. The source voltage has 10% of negative-sequence component at the fundamental frequency, plus 5% of a 5th harmonic and 5% of a 7th harmonic. The vaw voltage, after the start of the series active filter, becomes almost sinusoidal. Fig. 11 shows the DC Link Voltage vDC and the losses in the UPQC, represented by the Gloss signal. The reference value at the terminals of the DC-link is equal to 4.5 volts. It may be noticed, that the ripple at the DC-link voltage is very small, in the order of 0.4% of the reference value during a short transient period, after the start of the UPQC, and less than 0.1 %, in steady-state operation. The switching losses of the inverters may not represent the reality, since ideal models of switches in the digital simulator are used. This condition is needed in the proposed system, because a basis of 1V and 1A was chosen. Fig. 12 shows the source currents ias, ibs, ics, the compensated voltages vaw, vbw, vcw, and the current ias together with voltage vaw repeated in a separated graphic, before and after vas 2.0 1.0 0.0 -1.0 -2.0 v ac 1.0 0.5 0.0 -0.5 -1.0 vaw . (8) Fig. 9 shows the load, shunt and source currents ial, iac, ias, before, and after the start of the shunt-active filter. After the start of the shunt active filter, the source current becomes almost sinusoidal. It may be noticed, that the time 2.0 1.0 0.0 -1.0 -2.0 0.10 0.12 0.14 0.16 0.18 0.20 0.22 0.24 0.26 0.28 Fig. 10. Supply voltage, compensating voltage, and the compensated voltage delivered to the critical load. the UPQC energization. It may be seen that, when the UPQC start its operation the source currents, as well the compensated voltages become almost sinusoidal and balanced. The source current ias and the compensated voltage vaw are almost in phase after the start of the UPQC. It confirms that the control strategy proposed is useful in a threephase three-wire system, where the system voltages are unbalanced and distorted and the load currents with high contents of harmonics. 5.00 vDC 4.75 4.50 4.25 4.00 0.2 Gloss 0.1 0.0 -0.1 -0.2 IV. CONCLUSIONS A control strategy for Unified Power Quality Conditioner — the UPQC — is proposed. Simulation results have validated the proposed control strategy, for the use in three-phase three-wire systems. In case of using in threephase four-wire systems, there is the necessity of compensating the neutral current. In this case, three-phase fourwire PWM converter is necessary. The computational efforts to develop the proposed control strategy is reduced, if compared with pq-Theory-based controllers, since the α-β-0 transformation is avoided. For three-phase three-wire systems, the performance of the proposed approach is comparable with those based on the pq Theory, without loss of robustness even if operating under distorted and unbalanced system voltage conditions. Presently, the authors are working on the possibility of extending the proposed control strategy for the use in threephase four-wire systems. V. REFERENCES [1] [2] [3] [4] [5] [6] [7] [8] [9] S. Fryze, “Wirk-, Blind- und Scheinleistung in elektrischen Stromkainsen mit nicht-sinusfömigen Verlauf von Strom und Spannung,” ETZ-Arch. Elektrotech., vol. 53, 1932, pp. 596-599, 625-627, 700-702. L. Malesani, L. Rosseto, P. Tenti, “Active Filter for Reactive Power and Harmonics Compensation”, IEEE – PESC 1986, pp. 321-330. Luís F.C. Monteiro, M. Aredes, “A Comparative Analysis Among Different Control Strategies for Shunt Active Filters,” Proc. (CDROM) of the V INDUSCON - Conferência de Aplicações Industriais, Salvador, Brazil, July 2002, pp.345-350. T. Furuhashi, S. Okuma, Y. Uchikawa, "A Study on the Theory of Instantaneous Reactive Power," IEEE Trans. on Industrial Electronics, vol. 37, no. 1, pp. 86-90, Feb. 1990. L. Rossetto, P. Tenti, "Evaluation of Instantaneous Power Terms in Multi-Phase Systems: Techniques and Application to PowerConditioning Equipments," ETEP – Eur. Trans. Elect. Power Eng., vol. 4, no. 6, pp. 469-475, Nov./Dec. 1994. M. Depenbrock, D. A. Marshall, J. D. van Wyk, "Formulating Requirements for a Universally Applicable Power Theory as Control Algorithm in Power Compensators," ETEP – Eur. Trans. Elect. Power Eng., vol. 4, no. 6, pp. 445-455, Nov./Dec. 1994. F.Z. Peng, H. Akagi, A. Nabae, “A New Approach to Harmonic Compensation in Power Systems – A Combined System of Shunt Passive and Series Active Filters,” IEEE Trans. Ind. Appl , vol.26, no.6, Nov./Dec. 1990, pp. 983-990. M. Aredes, J. Häfner, K. Heumann, “ A Combined Series and Shunt Active Power Filter,” IEEE/KTH Stockholm Power Tech Conf., vol. Power Electronics, pp. 237-242, Stockholm, Sweden, June 1995. H. Fujita, H. Akagi, “The Unified Power Quality Conditioner: The Integration of Series and Shunt Active Filters,” IEEE Trans. on Power Electronics, vol.13, No.2, March 1998. 0.1 0.2 0.3 0.4 0.5 0.6 Fig. 11. DC link voltage signal vDC and DC voltage regulator signal Gloss vbw vaw vcw 2.0 1.0 0.0 -1.0 -2.0 ics 0.4 0.2 ias ibs 0.0 -0.2 -0.4 vaw 2.0 1.0 ias 0.0 -1.0 -2.0 0.18 0.20 0.22 0.24 0.26 0.28 0.30 Fig. 12. Source currents, compensated voltages and the compensated voltage vaw together with the source current ias VI. BIOGRAPHIES Luís Fernando Corrêa Monteiro was born in Rio de Janeiro State on March 1975. He received the B. Sc. Degree from Federal University of Rio de Janeiro in 2003. He is enrolled in M.Sc. at COPPE/UFRJ in Power Electronics where is developing control strategies for active filters and devices to improve the power quality in the electrical system. His Main research areas of interest are Custom Power and FACTS. The engineer Luís F. C. Monteiro is a student member of the Brazilian Power Electronics Society (SOBRAEP), International Electrical and Electronics Engineering (IEEE), and Council on Large Electric Systems (CIGRE). Maurício Aredes (S’94, M’97) was born in São Paulo State, Brazil, on August 14, 1961. He received the B.Sc. degree from Fluminense Federal University, Rio de Janeiro State in 1984, the M.Sc. degree in Electrical Engineering from Federal University of Rio de Janeiro in 1991, and the Dr.-Ing. Degree (magna cum laude) from Technische Universität Berlin in 1996. From 1985 to 1988 he worked at the Itaipu HVDC Transmission System and from 1988 to 1991 in the SCADA Project of Itaipu Power Plant. From 1996 to 1997 he worked within CEPEL – Centro de Pesquisas de Energia Elétrica, Rio de Janeiro, as R&D Engineer. In 1997, he became an Associate Professor at the Federal University of Rio de Janeiro, where he teaches Power Electronics. His main research area includes HVDC and FACTS systems, active filters, Custom Power and Power Quality Issues. Dr. Aredes is a member of the Brazilian Society for Automatic Control and the Brazilian Power Electronics Society. João A. Moor Neto was born in Rio de Janeiro State on 1965. He received the B.Sc. Degree from UCP-RJ in 1991, and M.Sc. from Federal University of Itajubá in 1995. He is enrolled in D.Sc. at COPPE/UFRJ in Power Electronics since 2002. In 1995 he became a Professor at UNIJUI-RS, where he teaches Power System. His main research areas of interest are FACTS and Custom Power.