Analyze Power Supply Rejection Ratio of LDO Regulator Based on

advertisement

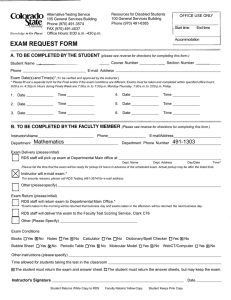

Proceedings of the International Conference on Electronics and Software Science, Takamatsu, Japan, 2015 Analyze Power Supply Rejection Ratio of LDO Regulator Based on Accurate Small Signal Model Po-Yu Kuo*, Gang-Zhi Fan and Chi-Huang Chiu Department of Electronic Engineering, National Yunlin University of Science and Technology 123 University Road, Section 3,Douliou, Yunlin 64002, Taiwan, R.O.C. *Email:kuopy@yuntech.edu.tw ABSTRACT The power supply rejection ratio (PSRR) is a crucial specification for the low-dropout regulator (LDO). Many circuit topologies have been proposed to achieve high PSRR for the LDO. To simplify the design flow, most analog circuit designers estimate the PSRR performance based on the small signal model. However, the accuracy of the small signal model for PSRR has not been verified. In this paper, the accuracy of the general small signal model has been analyzed. A new small signal model for PSRR of LDO has been developed and verified. The simulation results shows that the accuracy has been improved significantly while the new model is applied comparing to the general model. The simulation results has been verified using a standard 0.35-µm CMOS process technology. KEYWORDS Power supply rejection ratio (PSRR); low-dropout regulator (LDO); small signal model; CMOS process technology. simplify the design flow, most analog circuit designers estimate the PSRR performance based on the small signal model. However, the small signal model for PSRR is not straightforward to obtain. The small signal model of PSRR for LDO has been discussed in [1]. The proposed model is generally used by most circuit designers. However, this model is not accurate to analyze the PSRR performance of LDO. In this paper, the PSRR model in [1] has been verified and the results show that it bears a significant difference compared with the LDO at low frequencies. The errors from this model are up to 11.2dB. Therefore, a new small signal model for PSRR of LDO has been developed and verified, by considering the effects caused by the parasitic capacitors. The results show that the errors of PSRR are reduced to 1.17dB while new model is applied. With this new model, the analog circuit designers can estimate the accurate PSRR in the pre-design stage. 1 INTRODUCTION 2 General PSRR Model of LDO The low-dropout regulator (LDO) is a very common circuit block in the dc-dc converter. When an operation voltage of an electronic device is supplied by a LDO, it is impossible to avoid ripple noise voltage that comes along a power supply line. To tackle the issue, it is necessary to design a LDO with high power supply rejection ratio (PSRR) so that the impact caused by the ripple noise voltage can be reduced as much as possible. Therefore, many circuit topologies have been proposed to achieve high PSRR for the LDO [1]–[4]. To 2.1 PSRR Model for Error Amplifier ISBN: 978-1-941968-17-8 ©2015 SDIWC The PSRR is mainly caused by the device connected directly to the power supply input and output [1]. In the LDO, many transistors in the error amplifier are connected to the power supply input and output. Hence, we must consider the PSRR model for error amplifier. To perform double-to-single-ended conversion, and add the ac signal obtained from the input differential pair to a single-ended signal, most error amplifier that has a single-ended output 124 Proceedings of the International Conference on Electronics and Software Science, Takamatsu, Japan, 2015 (a) (b) Figure 1. (a) Type-A error amplifier and (b) its small signal model for PSRR. (a) (b) Figure 2. (a) Type-B error amplifier and (b) its small signal model for PSRR. use a current-mirror load. The current-mirror load can be implemented by connecting the PMOS to the supply voltage, or by connecting the NMOS to the ground. In the following of this paper, the PMOS-mirror is classified as Type-A topologies and NMOS-mirror is classified as Type-B topologies. Hence, it is apparent that the implementation of the current mirror is crucial in determining the PSRR of error amplifier. To analyze the PSRR, Vdd and Vout-A has been defined as ac ripple at the power supply and the output of the amplifier, respectively. The internal paratactic capacitance has been ignored for simplicity because they are much smaller comparing to the capacitance of the large output power device. PMOS load of Mp1 is much smaller than R2, the 1/gm resistance can be ignored so that power supply ripple is entirely reflected at the output. The relationship of Vout-A and Vdd is shown as follows: 2.2 Type-A Topologies A structure of Type-B error amplifier and its small signal model for PSRR are shown in Fig. 2 [1]. The amplifier in Fig. 2(a) is a general structure of the Type-B Topology error amplifier. The amplifier consists of PMOS input differential pair with the NMOS current mirror load connected to the ground. The PSRR model to this error amplifier can be derived by using the same analysis procedure in previous section. The model is obtained by grounding the two differential inputs and applying the AC voltage source Vdd as the input supply. The current-dependent current source iR1 is the current flowing through R1 into the output. Thus, this current models the effect of current mirror. Because the diode-connected NMOS A structure of Type-A error amplifier and its small signal model for PSRR are shown in Fig. 1 [1]. The amplifier consists of an NMOS input differential pair with the PMOS current mirror load connected to the power supply. The small signal PSRR model of the Type-A error amplifier is shown in Fig. 1(a). The model is obtained by grounding the two differential inputs and applying the AC voltage source Vdd as the input supply. The channel resistances of the PMOS and NMOS devices are R1 and R2, respectively. The current-dependent current source iR2 is the current flowing through R2 into the output. Thus, this current models the effect of current mirror. Because the diode-connected ISBN: 978-1-941968-17-8 ©2015 SDIWC R2 + i R2 (R 1 || R 2 ) Vout − A = Vdd R1 + R 2 R 2 Vdd R 1R 2 + = Vdd ≈ Vdd R1 + R 2 R 2 R1 + R 2 (1) For Type-A amplifier topologies, the entirely supply ripple is transferred to the output over a wide frequency range. 2.3 Type-B Topologies 125 Proceedings of the International Conference on Electronics and Software Science, Takamatsu, Japan, 2015 ( a1 = Rrds1 rds 2 rds 4 C1 + C m + C gsp + C gdp ( ) ) ( + Rrds1 rds 2 rdsp C m + C gdp + Rrds 2 rds 4 rdsp C m + C gdp ( + Rg mp rds1 rds 2 rds 4 rdsp C1 + C m + C gdp ) ) b0 = Rrds1 (rds 2 + rds 4 ) + rds1 rdsp (rds 2 + rds 4 ) + Rg m1 g mp rds1 rds 2 rds 4 rdsp ( b1 = Rrds1 rds 2 rds 4 C1 + C m + C gsp + C gdp ) + RC gdp rds1 rdsp (rds 2 + rds 4 ) + RC m rds1 rdsp (rds 2 + rds 4 ) + RCout rds1 rdsp (rds 2 + rds 4 ) ( + rds1 rds 2 rds 4 rdsp C1 + C m + C gsp + C gdp ( + RC gdp rds1 rds 2 rds 4 rdsp g mp − g m1 Figure 3. The schematic of a conventional LDO. ( + RC m rds1 rds 2 rds 4 rdsp g mp − g m1 R 2 Vdd − ≈ Vdd R1 + R 2 R1 R 1R 2 = 0 R1 + R 2 (2) The conventional small signal model for PSRR of a general LDO shown in Fig. 3, has been discussed in [1]. The system transfer function can be derived from the model as shown in (3) as follows: a0 = Rrds1 (rds 2 + rds 4 ) + Rg mp rds 4 rdsp (rds1 − rds 2 ) ( a2 = RC gsp rds1rds 2 rds 4 rdsp C gdp + Cm ) ISBN: 978-1-941968-17-8 ©2015 SDIWC ) + RC gdp rds1 rds 2 rds 4 rdsp (C gsp + C out ) 2.4 Conventional PSRR Model for LDO where ) b2 = RC1rds1 rds 2 rds 4 rdsp C m + C gdp + C out load of MN2 is much smaller than the channel resistance R1, the 1/gm resistance can be ignored so that power supply ripple is entirely reflected at the output. The relationship of VoutA and Vdd is shown as follows: From (2), it is very clear that there is not dc ripple appears at the output and theoretically isolating the output from the input supply ripple. For the general LDO, most circuit designers use a PMOS transistor as power transistor at the output because it exhibits a low forward drop and consequently a low power loss across the PMOS device. The PSRR model of LDO can be obtained by including the PSRR models of error amplifier and PMOS power transistor. a + a s + a2 s 2 H LDO (s) = 0 1 b0 + b1s + b2 s 2 ) ( R2 − i R1 (R1 || R 2 ) Vout − A = Vdd R1 + R 2 ) + RC gsp rds1 rds 2 rds 4 rdsp (C m + C out ) + RC m Cout rds1 rds 2 rds 4 rdsp In the equation, gmp is the transconductance of transistor Mp, gm12 is the transconductance of input differential pair M1 and M2, RoA is the output resistance of the single stage amplifier, RdsMP is the drain-source resistance of transistor Mp, Cm is the miller compensation capacitor, CoL is the output capacitor of LDO, and CoA is the output capacitor of single stage amplifier. In the following experiments, the SPICE simulation results were carried out using a standard 0.35-µm CMOS process technology. The simulated PSRR of the system transfer function (3) and the LDO are shown in Fig. 4. From the simulation results, the PSRR performance from the system transfer function bears a significant difference up to 11.2dB at low frequencies. The errors in magnitude at low frequencies are up to −13.2% when the transfer function (3) is applied. Since the errors are too large to demonstrate accurate PSRR behavior of the LDO, the transfer function (3) cannot be used to estimate PSRR behavior of the LDO. 3 PROPOSED NEW PSRR MODEL OF LDO (3) To achieve high accuracy, the small signal model can be constructed based on the complete small signal equivalent circuit of CMOS transistor discussed in [5][6]. In order to 126 Proceedings of the International Conference on Electronics and Software Science, Takamatsu, Japan, 2015 Figure 4. Simulated PSRR of the system transfer function (3). Figure 6. Simulated PSRR of the the proposed PSRR model. achieve simplicity without losing of accuracy, the intrinsic part of complete small signal equivalent circuit of CMOS transistor, has been applied in the new model. Fig. 5 shows the proposed PSRR model of LDO. To improve the accuracy of the general model, two parasitic capacitors Cgsp and Cgdp, have been added in the proposed model. The Gate-Source capacitor of Mp, Cgsp, must be considered in the small signal model since this capacitor is connected to the power supply Vdd. The Gate-Drain capacitor of Mp, Cgdp, is connected to the output node Vout. Thus, capacitor Cgdp will affect the PSRR of the LDO and cannot be ignored in the small signal model. The simulated PSRR of the proposed model is shown in Fig. 6. From the simulation results, the PSRR performance from the proposed model is identical to the CMOS LDO. The maximum error of magnitude for the small signal model at low frequencies is reduced to 1.17 dB compared with that from the transfer function (3). The error at low frequencies are –1.38% when the proposed PSRR model is applied. Hence, the proposed new model can achieve accurate estimation for PSRR of LDO. 4 CONCLUSIONS This paper proposed a new small signal model for PSRR of LDO. The accuracy of the general and new models have been verified with CMOS LDO. The errors of PSRR at low frequencies are up to −13.2% when the general model is applied. The errors at low frequencies are reduced to –1.38% if the new model is applied. With the proposed model, the circuit designers can estimate accurate PSRR performance during the pre-design stage and speed up the whole design flow. ACKNOWLEDGEMENT The authors would like to appreciate the support from Ministry of Science and Technology, Taiwan, under the Grants: MOST 103-2221-E-224-079 and the technical support from the National Chip Implementation Center (CIC). REFERENCES [1] Figure 5. Proposed PSRR model of LDO. ISBN: 978-1-941968-17-8 ©2015 SDIWC V. Gupta, G. A. Rincon-Mora, and P. Raha, “Analysis and design of monolithic, high PSR, linear regulators for SoC applications,” in Proc. IEEE Int. SOC Conf., pp. 311–315, Sep. 2004. 127 Proceedings of the International Conference on Electronics and Software Science, Takamatsu, Japan, 2015 [2] [3] [4] [5] [6] B. Forejt, V. Rentala, J. D. Arteaga, and G. Burra, “A 700+-mW class D design with direct battery hookup in a 90-nm process,” IEEE J. Solid-States Circuits, vol. 40, no. 9, pp. 1880–1887, Sep. 2005. S. Heng and C.-K. Pham, “A low-power high-PSRR low-dropout regulator with bulk-gate controlled circuit,” IEEE Trans. Circuits Syst. II, vol. 57, no. 4, pp. 245–249, Apr. 2010. M. Ho, K. N. Leung, and K.-L. Mak, “A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages,” IEEE J. Solid-States Circuits, vol. 45, no. 11, pp. 2466–2475, Nov. 2010. J. Guo and A. Werthof, “Direct parameter extraction method for deep submicrometer metal oxide semiconductor field effect transistor small signal equivalent circuit,” IET Microwaves, Antennas & Propagation, vol. 3, no.4, pp. 564–571, Jun. 2009. Ooi, B. L., Z. Zhong, and M. S. Leong. “Analytical Extraction of Extrinsic and Intrinsic FET Parameters.” IEEE Transactions on Microwave Theory and Techniques, vol. 57, no. 2, pp. 254–261, Feb. 2009. ISBN: 978-1-941968-17-8 ©2015 SDIWC 128