Title Fluorinated InGaZnO Thin-Film Transistor With HfLaO Gate

advertisement

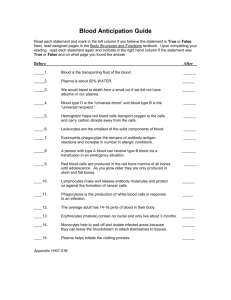

Title Author(s) Citation Issued Date URL Rights Fluorinated InGaZnO Thin-Film Transistor With HfLaO Gate Dielectric QIAN, L; Lai, PT IEEE Electron Device Letters, 2014, vol. 35 n. 3, p. 363-365 2014 http://hdl.handle.net/10722/202928 IEEE Electron Device Letters. Copyright © IEEE IEEE ELECTRON DEVICE LETTERS, VOL. 35, NO. 3, MARCH 2014 363 Fluorinated InGaZnO Thin-Film Transistor With HfLaO Gate Dielectric Ling Xuan Qian and Peter T. Lai, Senior Member, IEEE Abstract— Fluorinated amorphous InGaZnO thin-film transistor with HfLaO gate dielectric has been studied by treating InGaZnO film in a CHF3 /O2 plasma. The saturation carrier mobility can be improved from 29.6 cm2 /V · s to as high as 39.8 cm2 /V · s. In addition, the passivation effect of the fluorination on the dominant donor-like traps at the InGaZnO/HfLaO interface is observed, as reflected by suppression of hysteresis phenomenon and smaller subthreshold swing. Measurement result of low-frequency noise further supports the improvement in electrical properties by the plasma treatment. Index Terms— Amorphous InGaZnO (a-IGZO), thin-film transistor (TFT), HfLaO, fluorine, plasma. I. I NTRODUCTION N THE field of flat-panel displays (FPDs), thin-film transistors (TFTs) with high field-effect mobility (μFE ) are required [1]. Accordingly, ZnO-based TFTs have been intensively investigated to replace conventional amorphous silicon TFTs. Compared to polycrystalline ZnO (poly-ZnO) TFTs, amorphous InGaZnO (a-IGZO) TFTs exhibit better spatial uniformity of device performance. In addition, the incorporation of Ga ions, which act as carrier suppressors and network stabilizers in InZnO (IZO), is beneficial to achieving high carrier mobility and excellent uniformity [2]. Hence, a-IGZO TFT has been regarded as one of the most promising candidates for the application in FPDs. Lee et al. reported a-IGZO TFT with a high μFE of 28 cm2 /V · s using ZrO2 gate dielectric [3]. However, it had large subthreshold swing (SS, 0.56 V/dec) and large threshold-voltage (VTH ) hysteresis (VH , 3 V), which could slow down the switching and deteriorate the reliability properties of the device respectively. In addition, Zan et al. used nanometer dot doping to improve μFE to an average value of 67.5 cm2 /V · s [4]. Nevertheless, if considering the effective intrinsic channel length, the average intrinsic μFE is 33.8 cm2 /V · s. However, the SS of this device is as large as 0.92 V/dec, and a negative VTH of −2.94 V was achieved, making the device unsuitable for switching applications. a-IGZO TFT with Ta2 O5 gate dielectric achieved a high μFE of 61.5 cm2 /V · s, but also had a large SS (0.61 V/dec) [5]. It was reported that the electrical characteristics of poly-ZnO TFTs could be improved by fluorine implantation [6]. Unfortunately, the improvements in mobility and SS were accompanied by a change of operation mode from accumulation to depletion. I Manuscript received December 3, 2013; revised December 20, 2013; accepted December 22, 2013. Date of publication January 24, 2014; date of current version February 20, 2014. This work was supported by the University Development Fund, Nanotechnology Research Institute of the University of Hong Kong, under Grant 00600009. The review of this letter was arranged by Editor A. Chin. The authors are with the Department of Electrical and Electronic Engineering, the University of Hong Kong, Hong Kong (e-mail: laip@eee.hku.hk). Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/LED.2013.2296895 Fig. 1. Schematic diagrams of the device cross section: (a) during the CHF3 /O2 plasma treatment; (b) a-IGZO TFT with HfLaO gate dielectric. Furthermore, fluorine doping by spin coating of metalfluoride (ZnF2 and InF3 ) precursor aqueous solution was also adopted to improve both the carrier mobility and stability of IZO TFTs [7]. In this letter, the effects of fluorine incorporation in a-IGZO on the characteristics of a-IGZO TFTs are studied for the first time. Fluorine is introduced in a-IGZO by means of plasma treatment, which is more compatible with device processing on large-area substrate and also induces less damage to thin film than implantation. Due to its superior properties, including high dielectric constant, good thermal stability and low trap density [8], high-k material HfLaO is selected as the gate dielectric for the samples in this letter. Consequently, both high saturation carrier mobility (μsat , 39.8 cm2 /V · s) and small SS (0.21 V/dec) can simultaneously be obtained by the sample with the plasma treatment. Moreover, this sample can operate in enhancement mode with a small VH of −0.5 V. II. E XPERIMENTAL D ETAILS The schematic diagrams of the device cross section during the CHF3 /O2 plasma treatment and after all the fabrication processes are shown in Fig. 1. P-type (100) silicon acts as both substrate and gate electrode. Firstly, deposition of a 40-nm HfLaO film was done by a sputtering system. An annealing treatment at 400 °C in N2 for 10 min followed. Subsequently, the sample received a deposition of a 60-nm a-IGZO active layer through radio-frequency (RF) sputtering in an Ar/O2 mixed ambient. Then, the sample received the CHF3 /O2 plasma treatment with the flow rate of 10 sccm/ 1 sccm at a RF power of 20 W for 3 min. The addition of O2 was to remove carbon and increase fluorine concentration by suppressing CFx radicals [9], [10]. The control sample without plasma treatment was also fabricated. After that, a lift-off process was utilized to form the source/drain electrodes, which were composed of 20-nm Ti and 80-nm Au. The channel width (W) and length (L) were 100 μm and 20 μm respectively. Finally, both samples were annealed in a forming-gas (N2 : H2 = 95 : 5) ambient at 350 °C for 20 min. In addition, metal-insulator-semiconductor (MIS) capacitor was prepared beside the transistor to monitor the gate-oxide capacitance per unit area (Cox , equal to 0.202 μ F/cm2 in this letter). For each condition, 12 devices were measured, and the device with the median value of μsat was selected to represent the condition. 0741-3106 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications_standards/publications/rights/index.html for more information. 364 IEEE ELECTRON DEVICE LETTERS, VOL. 35, NO. 3, MARCH 2014 Fig. 2. SIMS depth profiles in the stacks of IGZO/HfLaO/Si thin films for: (a) Zn, Hf, La and Si in the plasma-treated sample before the forming-gas annealing; (b) F in the plasma-treated sample before & after the forming-gas annealing. III. R ESULTS AND D ISCUSSION Fig. 2 exhibits the secondary ion-mass spectrometry (SIMS) depth profile in the stack of IGZO/HfLaO/Si thin films. The ordinate refers to the atom counts in an analysis area of 56.6 μm × 56.6 μm while the abscissa is about the acquisition time which reflects the depth from the surface of a-IGZO. For the plasma-treated sample before the forming-gas annealing, it is apparent that fluorine has been successfully introduced into a-IGZO by the plasma treatment, and majority of fluorine atoms piles up near the surface of a-IGZO. The fluorine peak at the IGZO/HfLaO interface should be due to its blocking effect on the fluorine incorporation. After the forming-gas annealing, fluorine atoms have diffused towards the a-IGZO/HfLaO interface, and a fraction of them has spread into HfLaO. Fig. 3(a) shows the transfer characteristics of the a-IGZO TFTs with or without CHF3 /O2 plasma treatment for a-IGZO: 1/2 drain current (ID ) vs. VGS , and ID vs. VGS at a drainto-source voltage (VDS ) of 5 V. The important electrical parameters are extracted from Fig. 3 and listed in Table I. Among them, μ sat and VTH are calculated from a linear fitting 1/2 to the plot of ID vs. VGS (using a VGS range of 1 V), which is based on the I–V equation of field-effect transistor operating in the saturation region: ID = (μsat Cox W/2L) (VGS −VTH )2 (1) The inset of Fig. 3(a) reveals μsat is gate-bias dependent, which is consistent with the result reported in [11], and accordingly the maximum value of μsat during the VGS sweeping is selected for comparison purpose [6], [11]. Compared to the control sample (μsat = 29.6 cm2 /V · s), the plasma1/2 treated sample possesses a steeper slope of ID vs. VGS and 2 accordingly a higher μsat (39.8 cm /V · s). It is well known that fluorine and oxygen have similar ionic radius, and the Zn–F bonding is more stable than the Zn–O one. Therefore, it is easy to cause the substitution of the oxygen atoms in the lattice (OX O ) of a-IGZO by the fluorine atoms derived from the CHF3 /O2 plasma. Moreover, the difference in electrovalency between oxygen ion (O2− ) and fluorine ion (F− ) can induce the substitution of an oxygen ion by a fluorine ion to generate a free electron [7]: − • − OX O +F → FO + e (2) Therefore, the electron concentration in a-IGZO is increased, resulting in a shift of the zero-gate-bias Femi level towards Fig. 3. Transfer (a) and output (b) characteristics of the a-IGZO TFTs. TABLE I E XTRACTED E LECTRICAL PARAMETERS OF IGZO TFTs the conduction band. Accordingly, a larger fraction of the acceptor-like traps in a-IGZO and/or at the a-IGZO/HfLaO interface can be filled by the generated free electrons. As a result of the filling of acceptor-like traps at/near the a-IGZO/HfLaO interface, trap-induced scattering on channel electrons is suppressed, and thus carrier mobility is increased [12]. However, even with an increased electron concentration in a-IGZO, VTH is slightly increased from 2.5 V to 2.8 V by the plasma treatment, possibly due to the introduction of negative fluorine ions in the gate oxide. Fig. 3(b) displays the output characteristics of two samples. Both samples clearly exhibit the n-type enhancement mode. Moreover, ID increases linearly with VDS in the region of low VDS , and current saturation can be observed in the region of high VDS . Due to the increase in μsat , the on current (Ion ) at VGS = 10 V and VDS = 5 V for the plasma-treated sample (Ion = 1149 μA) is improved by over 20% compared to the control sample (Ion = 934 μA). However, the off current (Ioff ) is also increased, which should be ascribed to the conductivity increase of the ZnO-based material after fluorine incorporation demonstrated by Equation (2) [6], [7]. As a whole, a slight improvement of Ion /Ioff (from 9.0 × 105 to 9.2 × 105 ) can still be achieved by the plasma treatment. As shown in Fig. 4, both samples present a hysteresis phenomenon in the counter-clockwise direction, which reveals the dominant role of donor-like traps at the a-IGZO/HfLaO interface. Nevertheless, the reduction of VH from −1.3 V to QIAN AND LAI: FLUORINATED InGaZnO TFT WITH HfLaO GATE DIELECTRIC Fig. 4. Transfer characteristics of the a-IGZO TFTs measured under the forward and reverse sweepings. 365 It is found that μsat can be increased from 29.6 cm2 /V · s to as high as 39.8 cm2 /V · s by the plasma treatment. Accordingly, Ion is increased by over 20%. In addition, the passivation effect of plasma treatment on the dominant donor-like traps at the a-IGZO/HfLaO interface is also observed. As a result, the hysteresis phenomenon is suppressed while SS is reduced. Accordingly, both high saturation carrier mobility and small SS (0.21 V/dec) can simultaneously be achieved by the plasma-treated sample, which can also operate in enhancement mode with a small VH of −0.5 V. The LFN measurement result further supports the improvement in electrical properties. In summary, fluorinated a-IGZO is a promising material for making high-performance TFT used in the field of FPDs. R EFERENCES Fig. 5. The plot of SiD /I2D versus frequency of the a-IGZO TFTs. −0.5 V reveals that the counter-clockwise hysteresis can be obviously suppressed by the CHF3 /O2 plasma treatment for a-IGZO. Therefore, it is believed that the CHF3 /O2 plasma treatment can effectively passivate the dominant donor-like traps at the a-IGZO/HfLaO interface. A similar effect on donor-like traps after fluorine incorporation in ZnO-based material was reported [6]. In addition, the subthreshold region shown in Fig. 3(a) is steeper for the plasma-treated sample, and thus a smaller SS (0.21 V/dec) is obtained as compared to the control sample (SS = 0.31 V/dec). It was reported that the donor-like traps existing at the intermediate energy levels in the bandgap of ZnO could influence the subthreshold swing with a hump in the transfer curve of ZnO TFTs [13]. Moreover, Raja et al. claimed that the unpredictable subthreshold swing with a hump-shaped transfer curve in a-IGZO TFTs could be suppressed through passivating the natural intrinsic donor states [14]. Hence, the decrease of SS further verifies the passivation effect on the donor-like traps at the a-IGZO/HfLaO interface by the CHF3 /O2 plasma treatment. As shown in Fig. 5, the normalized noise power spectral density (SiD /I2D ) is measured at a fixed (VGS – VTH ) of 5.0 V in the linear region (VDS = 1.0 V) for each sample. The lowfrequency noise (LFN) of a-IGZO TFTs can be influenced by carrier number fluctuation (due to interface traps) and/or mobility fluctuation (due to Coulomb scattering) [15]. Since the LFN of the plasma-treated sample is smaller than that of the control sample, the improvement in electrical properties (smaller SS, smaller VH and higher μsat ) by the CHF3 /O2 plasma treatment is further supported. IV. C ONCLUSION In this letter, the effect of fluorine incorporation in a-IGZO by the CHF3 /O2 plasma treatment on the characteristics of a-IGZO TFT with HfLaO gate dielectric has been investigated. [1] T. Kamiya, K. Nomura, and H. Hosono, “Present status of amorphous In-Ga-Zn-O thin-film transistors,” Sci. Technol. Adv. Mater., vol. 11, no. 4, pp. 044305-1–044305-23, Sep. 2010. [2] J. S. Park, W. J. Maeng, H. S. Kim, et al., “Review of recent developments in amorphous oxide semiconductor thin-film transistor devices,” Thin Solidi Films, vol. 520, no. 6, pp. 1679–1693, Jan. 2012. [3] J. S. Lee, S. Chang, S. M. Koo, et al., “High-performance a-IGZO TFT with ZrO2 gate dielectric fabricated at room temperature,” IEEE Electron Device Lett., vol. 31, no. 3, pp. 225–227, Mar. 2010. [4] H. W. Zan, W. W. Tsai, C. H. Chen, et al., “Effective mobility enhancement by using nanometer dot doping in amorphous IGZO thinfilm transistors,” Adv. Mater., vol. 23, pp. 4237–4242, Aug. 2011. [5] C. J. Chiu, S. P. Chang, and S. J. Chang, “High-performance a-IGZO thin-film transistor using Ta2 O5 gate dielectric,” IEEE Electron Device Lett., vol. 31, no. 11, pp. 1245–1247, Nov. 2010. [6] Z. Ye and M. Wong, “Characteristics of thin-film transistors fabricated on fluorinated zinc oxide,” IEEE Electron Device Lett., vol. 33, no. 4, pp. 549–551, Apr. 2012. [7] J. S. Seo, J. H. Jeon, Y. H. Hwang, et al., “Solution-processed flexible fluorine-doped indium zinc oxide thin-film transistors fabricated on plastic film at low temperature,” Sci. Rep., vol. 3, no. 2085, pp. 1–9, Jun. 2013. [8] N. C. Su, S. J. Wang, C. C. Huang, et al., “Low voltage-driven flexible InGaZnO thin-film transistor with small subthreshold swing,” IEEE Electron Device Lett., vol. 31, no. 7, pp. 680–682, Jul. 2010. [9] K. Takahashi, M. Hori, and T. Goto, “Fluorocarbon radicals and surface reactions in fluorocarbon high density etching plasma. I. O2 addition to electron cyclotron resonance plasma employing CHF3 ,” J. Vac. Sci. Technol. A, vol. 14, no. 4, pp. 2004–2010, Jul./Aug. 1996. [10] B. Chapman, Glow Discharge Processes Sputtering and Plasma Etching, New York, NY, USA: Wiley, 1980, pp. 314–316. [11] K. H. Choi and H. K. Kim, “Correlation between Ti source/drain contact and performance of InGaZnO-based thin film transistors,” Appl. Phys. Lett., vol. 102, pp. 052103-1–052103-5, Feb. 2013. [12] H. Q. Chiang, B. R. McFarlane, D. Hong, et al., “Processing effects on the stability of amorphous indium gallium zinc oxide thin-film transistors,” J. Non Cryst. Solids, vol. 354, nos. 19–25, pp. 2826–2830, May 2008. [13] M. Furuta, Y. Kamada, M. Kimura, et al., “Analysis of hump characteristics in thin film transistors with ZnO channels deposited by sputtering at various oxygen partial pressures,” IEEE Electron Device Lett., vol. 31, no. 11, pp. 1257–1259, Nov. 2010. [14] J. Raja, K. Jang, N. Balaji, et al., “Negative gate-bias temperature stability of N-doped InGaZnO active-layer thin-film transistors,” Appl. Phys. Lett., vol. 102, pp. 083505-1–083505-4, Feb. 2013. [15] H. S. Choi, S. Jeon, H. Kim, et al., “Verification of interface state properties of a-InGaZnO thin-film transistors with SiN x and SiO2 gate dielectrics by low-frequency noise measurements,” IEEE Electron Device Lett., vol. 32, no. 8, pp. 1083–1085, Aug. 2011. [16] L. F. Lan and J. B. Peng, “High-performance indium-gallium-zinc oxide thin-film transistors based on anodic aluminum oxide,” IEEE Trans. Electron Device, vol. 58, no. 5, pp. 1452–1455, May 2011. [17] L. Yuan, X. Zou, G. Fang, et al., “High-performance amorphous indium gallium zinc oxide thin-film transistors with HfO x N y /HfO2 /HfO x N y tristack gate dielectrics,” IEEE Electron Device Lett., vol. 32, no. 1, pp. 42–44, Jan. 2011.