TGC4702-FC

advertisement

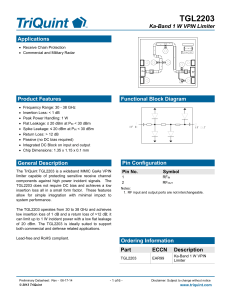

TGC4702-FC 77 GHz Down Converting IQ Mixer Key Features • • • • • • • Measured Performance RF & LO Frequency Range: 75 - 82 GHz IF Frequency Range: DC - 100 MHz Conversion Loss: 12 dB @ 77GHz RF-LO Isolation: 18 dB @ 77 GHz Bias: Vb = 1.1 V Technology: HBT with front-side Cu/Sn pillars Chip Dimensions: 2.46 x 1.89 x 0.38 mm Primary Applications Bias conditions: Vb = 1.1 V • Automotive Radar IF Out (I), LO - RF = 50 MHz, RFin = -1 dBm, LOin = +11 dBm Conversion Loss (dB) 13.0 12.5 Product Description 12.0 The TriQuint TGC4702-FC is a down converting IQ mixer designed to cover the automotive radar frequency band. 11.5 11.0 10.5 10.0 75 76 77 78 79 80 81 82 RF Frequency (GHz) LOin = +11 dBm 20 RF-LO Isolation (dB) 19 The TGC4702-FC typically provides 12 dB conversion loss from 75 – 82 GHz to an IF frequency band of DC – 100 MHz. The TGC4702FC is designed using TriQuint’s proven HBT process and front-side Cu / Sn pillar technology for simplified assembly and low interconnect inductance. Die reliability is enhanced by using TriQuint’s SiN passivation process. Lead-free and RoHS compliant. 18 17 16 15 14 13 12 11 10 75 76 77 78 79 80 81 82 LO Frequency (GHz) 1 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Table I Absolute Maximum Ratings 1/ Symbol Parameter Value Notes Vb Bias Voltage 2V 2/ Ib Bias Current 15 mA 2/ Input Continuous Wave Power (RF + LO) 24 dBm 2/ Pin 1/ These ratings represent the maximum operable values for this device. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device and / or affect device lifetime. These are stress ratings only, and functional operation of the device at these conditions is not implied. 2/ Combinations of supply voltage, supply current, input power, and output power shall not exceed the maximum power dissipation listed in Table IV. Table II Recommended Operating Conditions Parameter 1/ Symbol Vb Bias Voltage Ib Quiescent Bias Current PLO 1/ Value 1.1 V ~ 1 mA LO Input Power +11dBm See assembly diagram for bias instructions. 2 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Table III RF Characterization Table Bias: Ib=6mA, FLO=76.55GHz, FRF=76.50 GHz, PLO=11 dBm PARAMETER NOMINAL MAXIMUM UNITS Conversion Loss 12 16 dB RF – LO Output Isolation 16 dB I-Q Phase 90 Degrees 3 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Table IV Power Dissipation and Thermal Properties Parameter Maximum Power Dissipation 1/ Test Conditions Tbaseplate = 85 °C Value Notes Pd = 0.25 W 1/ Mounting Temperature Refer to Solder Reflow Profiles (pg 13) Storage Temperature -65 to 150 °C Channel operating temperature will directly affect the device median time to failure (MTTF). For maximum life, it is recommended that channel temperatures be maintained at the lowest possible levels. 4 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Measured Data on Flipped Die on Carrier Board Bias conditions: Vb = 1.1 V IF Out (I), LO - RF = 50 MHz, RFin = -1 dBm, LOin = +11 dBm Conversion Loss (dB) 13.0 12.5 12.0 11.5 11.0 10.5 10.0 75 76 77 78 79 80 81 82 RF Frequency (GHz) IF Out (I), LO - RF = 50 MHz, RFin = -1 dBm @ 77GHz 19 Conversion Loss (dB) 18 17 16 15 14 13 12 0 1 2 3 4 5 6 7 8 9 10 11 12 LO Power (dBm) 5 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Measured Data on Flipped Die on Carrier Board Bias conditions: Vb = 1.1 V IF Out (I), LO - RF = 50 MHz, LOin = +11 dBm @ 77.05 GHz 14.0 Conversion Loss (dB) 13.5 13.0 12.5 12.0 11.5 11.0 10.5 10.0 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7 8 9 10 11 12 RF Power (dBm) LO - RF = 50 MHz, RFin = -1 dBm, LOin = +11 dBm 100 I-Q Phase (Degrees) 90 80 70 60 50 40 30 20 10 0 74 75 76 77 78 79 80 81 82 83 RF Frequency (GHz) TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B 6 TGC4702-FC Measured Data on Flipped Die on Carrier Board Bias conditions: Vb = 1.1 V LO - RF = 50 MHz, RFin = -1 dBm @ 77 GHz 100 I-Q Phase (Degrees) 90 80 70 60 50 40 30 20 10 0 -1 0 1 2 3 4 5 6 7 8 9 10 11 12 13 LO Power (dBm) LO - RF = 50 MHz, LOin = +11 dBm @ 77.05 GHz 100 I-Q Phase (Degrees) 90 80 70 60 50 40 30 20 10 0 -11 -10 -9 -8 -7 -6 -5 -4 -3 -2 -1 0 1 RF Power (dBm) TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B 7 TGC4702-FC Measured Data on Flipped Die on Carrier Board LO-IF Isolation (dB) Bias conditions: Vb = 1.1 V LOin = 7.5 dBm 40 38 36 34 32 30 28 26 24 22 20 18 16 14 12 10 75 76 77 78 79 80 81 82 83 84 85 RF Frequency (GHz) LOin = +11 dBm 20 RF-LO Isolation (dB) 19 18 17 16 15 14 13 12 11 10 75 76 77 78 79 80 81 82 LO Frequency (GHz) 8 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Measured Data on Flipped Die on Carrier Board Bias conditions: Vb = 1.1 V IF Out (I), LO - RF = 50 MHz, RFin = -1 dBm, LOin = +11 dBm 9 8 Current (mA) 7 6 5 4 3 2 1 0 74 75 76 77 78 79 80 81 82 83 RF Frequency (GHz) IF Out (I), LO - RF = 50 MHz RFin = -1 dBm @ 77 GHz 9 8 Current (mA) 7 6 5 4 3 2 1 0 0 2 4 6 8 10 12 LO Power (dBm) TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B 9 TGC4702-FC Electrical Schematic Vb 5 or 9 2 RF In 17 12 IF Out (I) IF Out (Q) TGC4702-FC 7 LO In Bias Procedures Bias-up Procedure Bias-down Procedure Vb set to 0 V Turn off signals Adjust Vb slowly for 1.1 V (Ib will be ~ 1 mA) Turn Vb to 0 V Apply signals to RF In and LO In 10 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Mechanical Drawing 1.245 1.580 2.030 1.771 17 16 18 19 20 14 21 1.769 1.644 13 1 0.628 12 2 0.404 3 0.178 0.121 0.178 0.121 0.000 0.123 1.454 1.228 1.004 0.698 0.470 0.197 0.000 6 7 0.122 0.123 5 4 1.990 8 9 10 1.762 11 2.460 0.404 2.263 0.195 0.628 2.265 1.021 15 0.197 1.644 0.795 1.890 1.769 0.492 0.195 Drawing is for chip face-up Units: millimeters Thickness: 0.380 Die x,y size tolerance: +/- 0.050 Chip edge to pillar dimensions are shown to center of pillar Pillar #1,3,6,8,10, 11,13,16,18 RF CPW Ground 0.075 Ø Pillar #2 IF Out (I) 0.075 Ø Pillar #4, 10 DC Ground 0.075 Ø Pillar #5, 9 Vb 0.075 Ø Pillar #7 LO In 0.075 Ø Pillar #12 IF Out (Q) 0.075 Ø Pillar #17 RF In 0.075 Ø Pillar #14, 15, 19, 20, 21 Mech. Support Only 0.075 Ø GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test. 11 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Recommended Assembly Diagram TGC4702-FC data represented in this datasheet was taken using co-planar waveguide (CPW) transition on the substrate and ground-signal-ground probes RFin IFout (I) IFout (Q) 10 nF 10 nF LOin TGC4702-FC Die (flip-chip bonded) Vb +1.1V 1 uF Vg can be biased from either pillar # 5 or #9 Die is flip-chip soldered to a 15 mil thick alumina test substrate GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test. 12 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B TGC4702-FC Assembly Notes Component placement and die attach assembly notes: • Vacuum pencils and/or vacuum collets are the preferred method of pick up. • Air bridges must be avoided during placement. • Cu pillars on die are 65 um tall with a 22 um tall Sn solder cap. • Recommended board metallization is evaporated TiW followed by nickel/gold at pillar attach interface. Ni is the adhesion layer for the solder and the gold keeps the Ni from oxidizing. The Au should be kept to a minimum to avoid embrittlement; suggested Au / Sn mass ratio must not exceed 8%. • Au metallization is not recommended on traces due to solder wicking and consumption concerns. If Au traces are used, a physical solder barrier must be applied or designed into the pad area of the board. The barrier must be sufficient to keep the solder from undercutting the barrier. Reflow process assembly notes: • Minimum alloying temperatures 245 0C. • Repeating reflow cycles is not recommended due to Sn consumption on the first reflow cycle. • An alloy station or conveyor furnace with an inert atmosphere such as N2 should be used. • Dip copper pillars in “no-clean flip chip” flux prior to solder attach. Suggest using a high temperature flux. Avoid exposing entire die to flux. • If screen printing flux, use small apertures and minimize volume of flux applied. • Coefficient of thermal expansion matching between the MMIC and the substrate/board is critical for long-term reliability. • Devices must be stored in a dry nitrogen atmosphere. • Suggested reflow will depend on board material and density. Typical Reflow Profiles for TriQuint Cu / Sn Pillars Process Sn Reflow Ramp-up Rate 3 0C/sec Flux Activation Time and Temperature 60 – 120 sec @ 140 – 160 0C Time above Melting Point (245 0C) 60 – 150 sec Max Peak Temperature 300 0C Time within 5 0C of Peak Temperature 10 – 20 sec Ramp-down Rate 4 – 6 0C/sec Ordering Information Part Package Style TGC4702-FC GaAs MMIC Die GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test. 13 TriQuint Semiconductor: www. triquint.com (972)994-8465 Fax (972)994-8504 Info-mmw@tqs.com November 2009 © Rev B