PM8356

QuadPHY FC

Preliminary

4 Channel 1.0625 and 2.125 Gbit/s Fibre Channel Transceiver

FEATURES

GENERAL

• Four independent 1.0625 or

2.125 Gbit/s, bi-directional, Fibre

Channel transceiver to 10 bit parallel

interfaces.

• Integrated serializer/de-serializer,

clock recovery, clock synthesis, byte

alignment.

• Standalone pin configurable or

software configurable.

• No external components required to

interface the high-speed signals to

optics, coax, or serial backplanes.

• Integration of passive components to

minimize BOM cost.

• Simple power supply filtering

requirements.

• Meets 1/2G Fibre Channel Jitter

specifications for optical applications.

HIGH SPEED INTERFACE

PARALLEL INTERFACE

• Provides working and protect highspeed differential I/O for redundant

systems.

• Independent 1G/2G rate selection for

transmit and receive on a per channel

basis without affecting the operation of

channels not going through rate

selection process.

• Selectable transmit pre-emphasis and

receive equalization on a per-channel

basis to allow maximum reach.

• Supports differential PECL REFCLK at

106.25 MHz.

• Programmable output current that

directly drives 50 ohms.

• Provides internal 100 ohm differential

termination on transmit and receive

high-speed signals for optimal signal

integrity.

• Integrated AC coupling.

• Lock times less than 300 bit times.

• Parallel interface compatible with ANSI

T11.2 FC-HSPI.

• Receive recovered clock rates of

106.25 MHz for 2.125 Gbit/s operation,

and 106.25 or 53.125 MHz for

1.0625 Gbits/s operation.

• Transmit clock rates of 106.25 MHz for

2.125 Gbit/s operation, and

106.25 MHz for 1.0625 Gbit/s

operation.

• Provides both source-simultaneous or

source-centered transmit and receive

parallel interface timing modes to

simplify ASIC and FPGA system

interface implementations.

• Interoperates with 2.5 V SSTL-2 or

3.3V LVTTL levels.

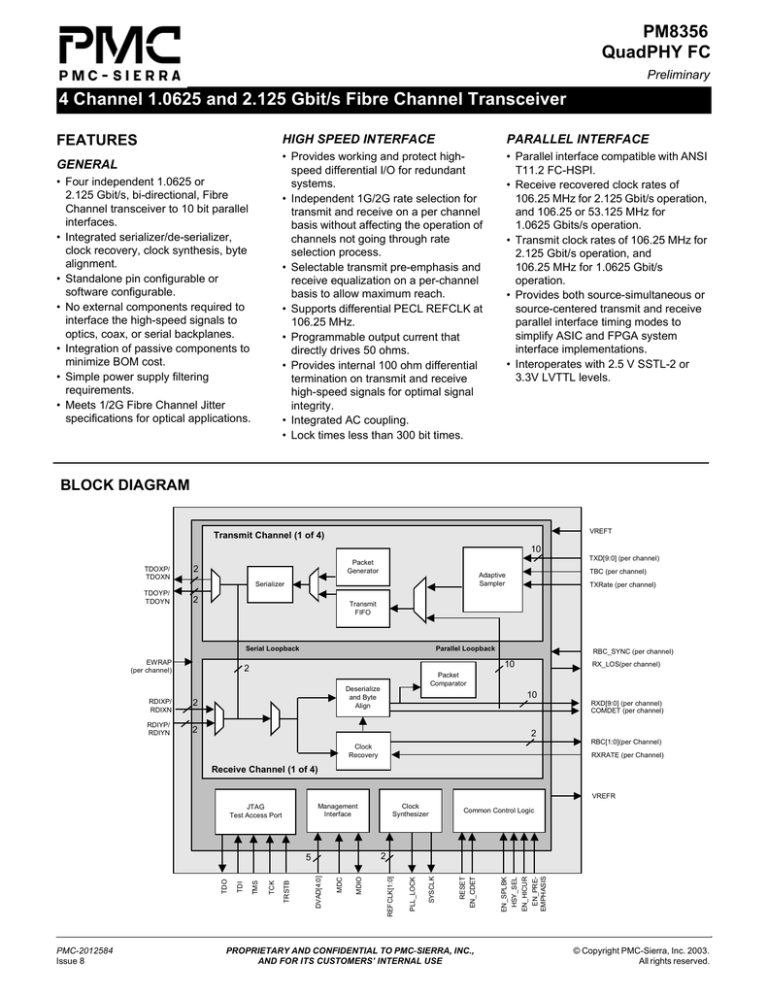

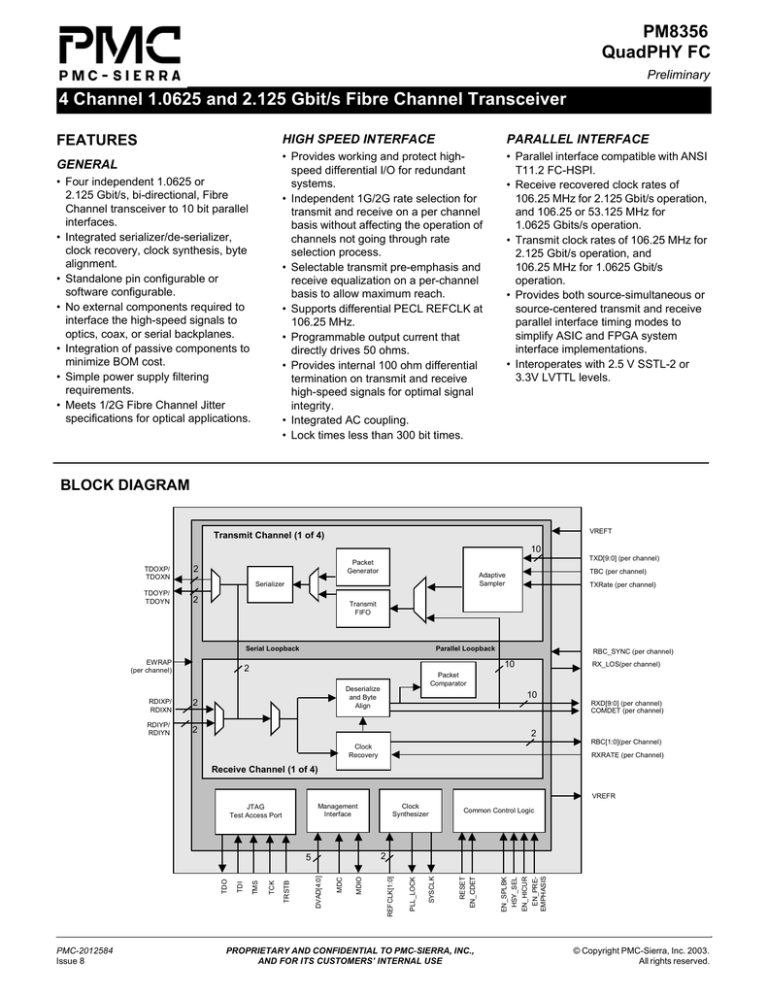

BLOCK DIAGRAM

VREFT

Transmit Channel (1 of 4)

10

TDOXP/

TDOXN

TDOYP/

TDOYN

Packet

Generator

2

2

Serial Loopback

RDIYP/

RDIYN

TXRate (per channel)

Transmit

FIFO

EWRAP

(per channel)

RDIXP/

RDIXN

TBC (per channel)

Adaptive

Sampler

Serializer

TXD[9:0] (per channel)

Parallel Loopback

RBC_SYNC (per channel)

10

2

Packet

Comparator

Deserialize

and Byte

Align

2

RX_LOS(per channel)

10

2

2

Clock

Recovery

RXD[9:0] (per channel)

COMDET (per channel)

RBC[1:0](per Channel)

RXRATE (per Channel)

Receive Channel (1 of 4)

VREFR

Management

Interface

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC.,

AND FOR ITS CUSTOMERS’ INTERNAL USE

EN_PREEMPHASIS

EN_HICUR

EN_SPLBK

HSY_SEL

RESET

EN_CDET

SYSCLK

PLL_LOCK

MDC

MDIO

DVAD[4:0]

TCK

TRSTB

TDI

TMS

TDO

Common Control Logic

2

5

PMC-2012584

Issue 8

Clock

Synthesizer

REFCLK[1:0]

JTAG

Test Access Port

© Copyright PMC-Sierra, Inc. 2003.

All rights reserved.

PM8356 QuadPHY FC

4 Channel 1.0625 and 2.125 Gbit/s Fibre Channel Transceiver

TEST FEATURES

PHYSICAL CHARACTERISTICS

APPLICATIONS

• Supports optional 2-pin serial

management interface using

MDC/MDIO protocol for configuration

and diagnostic access.

• Built in self-test (BIST) via internal

packet generation and checking.

• Serial and parallel loopback modes per

channel for testing and debugging.

• Standard IEEE 1149.1 JTAG test port

for boundary scan board purposes.

• An evaluation kit (PM2377-KIT) is

available for the QuadPHY FC.

• Low power 0.18 m CMOS technology.

• 324-pin, 23 mm x 23 mm HSPBGA

package with 1 mm ball pitch.

• Operates over industrial temperature

range -40 to +85 °C.

• Power supply: +/- 10%, 1.8 V for core,

2.5 V for SSTL-2 (3.3V for LVTTL).

• 1.0625 Gbit/s and 2.125 Gbit/s Fibre

Channel transceivers.

• High-speed serial backplanes.

• Storage Area Networking Systems.

• Work Station/Server Fibre Channel

I/O.

• Military and industrial applications.

TYPICAL APPLICATION

HIGH DENSITY FIBRE CHANNEL SWITCH

1,2,3 Gbit/s Backplane

Optics

1.0625 Gbit/s or

2.125 Gbit/s

FC link

Optics

PM8356

QuadPHY

FC

MAC/Port

Controller

ASIC

PM8356

QuadPHY

FC

PM8356

QuadPHY

FC

Optics

Optics

Switch

ASIC

10G FC Link

4 x 3.1875 Gbit/s

Optics

PM8355

QuadPHY

II

MAC/Port

Controller

ASIC

PM8355

QuadPHY

II

PM8355

QuadPHY

II

Four independent bi-directional

backplane links going to each of the

working and protect switch cards

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 1.604.415.6000

Fax: 1.604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PMC-2012584 (P8)

For a complete list of PMC-Sierra’s

trademarks, see our web site at

http://www.pmc-sierra.com/legal/.

Other product and company names

mentioned herein may be the trademarks of

their respective owners.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE