Routability-driven Placement Algorithm for Analog Integrated Circuits

advertisement

Routability-driven Placement Algorithm

for Analog Integrated Circuits

Cheng-Wu Lin, Cheng-Chung Lu, Jai-Ming Lin,

and Soon-Jyh Chang

March 27, 2012

Department of Electrical Engineering

National Cheng Kung University, Tainan, Taiwan

Outline

Introduction to Analog Placement

Routability-driven Analog Placement

Congestion Estimation

Placement Expansion

Proposed Placement Flow

Experimental Results

Conclusion

2

Analog Placement Considerations

Basic constraints

Matching interdigitated placement, common-centroid placement

Symmetry symmetric placement

Proximity adjacent placement

Substrate

Well

Other considerations

Thermal effects, stress gradients, etc.

M5

M3

M2 M1 M1 M2

M3 M 4

M1 M2 M1 M2

M1 M2 M2 M1

M1 M2

Interdigitated

placement

Common-centroid

placement

Symmetry constraint

M1

M4

M2

Proximity constraint

3

Analog Placement Approaches

Constructive method

Generate placement according to schematic topology [Mehranfar,

JSSC’91] or signal paths [Long et al., ASP-DAC’06]

M5

M5

M7、M10

M7、M10

VB1 M10

M5

○

M7

M7 、

、 M10

M10

W

2

M7

W

2

M1

M1 、

、 M2

M2

●

VIP

VIN

VON

○

●

CC2

M9

M11

●

M2

M1

○

●

M3

○

●

●

○

VB2

M4

●

VOP

M8

●

○

M6

M6 、

、 M9

M9

W

2

M11

M11

M3

M3 、

、 M4

M4

M8

M8

M6

M6 、

、 M9

M9

W

2

CC1

M6

C

and C C2

CC1

C1 and CC2

4

Analog Placement Approaches

Constructive method

Generate placement according to schematic topology [Mehranfar,

JSSC’91] or signal paths [Long et al., ASP-DAC’06]

4

Analog Placement Approaches

Constructive method

Generate placement according to schematic topology [Mehranfar,

JSSC’91] or signal paths [Long et al., ASP-DAC’06]

Deterministic algorithm

Enumerate all possible placements for the basic module sets,

and then combine these placements hierarchically [Strasser et al.,

ICCAD’08]

4

Analog Placement Approaches

Constructive method

Generate placement according to schematic topology [Mehranfar,

JSSC’91] or signal paths [Long et al., ASP-DAC’06]

Deterministic algorithm

Enumerate all possible placements for the basic module sets,

and then combine these placements hierarchically [Strasser et al.,

ICCAD’08]

4

Analog Placement Approaches

Constructive method

Generate placement according to schematic topology [Mehranfar,

JSSC’91] or signal paths [Long et al., ASP-DAC’06]

Deterministic algorithm

Enumerate all possible placements for the basic module sets,

and then combine these placements hierarchically [Strasser et al.,

ICCAD’08]

Statistical algorithm

Apply simulated annealing (SA) algorithm with floorplan

representations

4

Representations for Analog Placement

Topological representation is a popular method for modern VLSI

design

Smaller solution space (compared with absolute representation)

Need specific techniques to deal with placement constraints

Previous work of handling symmetry constraint

Sequence-pairs [Balasa & Lampaert, DAC’99]

O-trees [Pang et al., DAC’00]

Binary trees [Balasa, ICCAD’00]

TCG-S [Lin et al., ASP-DAC’05]

CBL [Liu et al., ASP-DAC’07]

Previous work of tackling common-centroid constraint

C-CBL [Ma et al., ICCAD’07]

B*-trees [Strasser et al., ICCAD’08]

Sequence-pairs [Xiao & Young, ASP-DAC’09]

5

Routability-driven Analog Placement

One of the objective function in SA algorithm is to minimize chip

area, which makes blocks compact to the lower-left corner

For analog design, a compact placement is not practical

Routing over the active areas of analog devices is usually

avoided to reduce parasitics and cross-talk effects

Reserve enough spaces between the devices for laying out

wires

6

Review of Congestion-aware Placement

Congestion-aware placement for analog circuits [Xiao et al., ICCAD’10]

Whole placement region is divided into an nn mesh, and vertical

and horizontal congestions are estimated for each room

Rooms are expanded column-by-column and row-by-row based on

the congestion map

Symmetry constraint

must be

satisfied after

placement

Symmetry

group expansion

Non-symmetry

module

55 mesh

Symmetry axis

Column expansion

Symmetry axis

Symmetry constraint

is violated!

7

Problem Formulation

Given a set of devices and topological placement constraints

The active areas of all devices are considered as routing blockages

Routing congestion in the resulting placement P is minimized

All topological constraints are satisfied in the resulting placement P

Cost function (P):

(P) = AP + WP + CP

AP: bounding-rectangle area of the placement

WP: total wire length measured by half-perimeter estimation

CP: estimation of routing congestion

8

Overview of Our Placement Flow

Input devices, netlist, and topological placement constraints

Generate a compact placement based on ASF-B*-trees and HB*-trees

Estimate routing congestion

Expand congested regions

Minimum

cost?

No

Yes

Done

9

Congestion Estimation

The way to predict congestion accurately is to use the same

technique and parameters in both congestion estimation and

global routing [Pan & Chu, ICCAD’06]

Congestion-driven Steiner tree construction can be used for

congestion estimation and global routing

Previous work: FastRoute [Pan & Chu, ICCAD’06], NTHU-Route

[Chang et al., ICCAD’08]

1. Use FLUTE to generate the Steiner

1. minimal trees for all nets

Congestion map generation

Congestion-driven Steiner tree construction

2. Route two-pin nets using L-shaped

2. pattern routing

3. Generate congestion map from the

3. routing demand

Route two-pin nets

using pattern routing and maze routing

10

Congestion Estimation

The way to predict congestion accurately is to use the same

technique and parameters in both congestion estimation and

global routing [Pan & Chu, ICCAD’06]

Congestion-driven Steiner tree construction can be used for

congestion estimation and global routing

Previous work: FastRoute [Pan & Chu, ICCAD’06], NTHU-Route

[Chang et al., ICCAD’08]

Congestion map generation

Reconstruct Steiner tree for each net

according to the congestion map

Congestion-driven Steiner tree construction

Route two-pin nets

using pattern routing and maze routing

10

Congestion Estimation

The way to predict congestion accurately is to use the same

technique and parameters in both congestion estimation and

global routing [Pan & Chu, ICCAD’06]

Congestion-driven Steiner tree construction can be used for

congestion estimation and global routing

Previous work: FastRoute [Pan & Chu, ICCAD’06], NTHU-Route

[Chang et al., ICCAD’08]

Congestion map generation

Reconstruct Steiner tree for each net

according to the congestion map

Congestion-driven Steiner tree construction

Route two-pin nets

using pattern routing and maze routing

10

Congestion Estimation

The way to predict congestion accurately is to use the same

technique and parameters in both congestion estimation and

global routing [Pan & Chu, ICCAD’06]

Congestion-driven Steiner tree construction can be used for

congestion estimation and global routing

Previous work: FastRoute [Pan & Chu, ICCAD’06], NTHU-Route

[Chang et al., ICCAD’08]

Congestion map generation

Reconstruct Steiner tree for each net

according to the congestion map

Congestion-driven Steiner tree construction

Route two-pin nets

using pattern routing and maze routing

10

Congestion Estimation

The way to predict congestion accurately is to use the same

technique and parameters in both congestion estimation and

global routing [Pan & Chu, ICCAD’06]

Congestion-driven Steiner tree construction can be used for

congestion estimation and global routing

Previous work: FastRoute [Pan & Chu, ICCAD’06], NTHU-Route

[Chang et al., ICCAD’08]

Proposed congestion map generation:

Congestion map generation

Congestion-driven Steiner tree construction

Route two-pin nets

using L-shaped pattern routing

Generate congestion map

from the routing demand

10

Congestion Map Generation with Analog Devices

Grid graph model for global routing:

Global bins

Modules

Global edges

Grid graph model

Since the active areas of all devices are considered as routing

blockages, we reduce global edge capacities of a bin if the bin is

occupied by some devices

11

Congestion Map Generation with Analog Devices

s

ce2 , de2

ce1 , de1

Edge capacity: ce

Routing demand: de

a

ce2* , de2

ce1* , de1

if de > ce*, overflowe = de – ce*

otherwise overflowe = 0

ce1* = 0

ce2* = ce2 a

s

12

Overview of Our Placement Flow

Input devices, netlist, and topological placement constraints

Generate a compact placement based on ASF-B*-trees and HB*-trees

Estimate routing congestion

Expand congested regions

Minimum

cost?

No

Yes

Done

13

Placement Expansion

To eliminate routing overflow, we slightly expand congested

regions of a compact placement

Placement expansion for non-symmetry modules

Placement expansion for symmetry groups

Dummy nodes are inserted into ASF-B*-trees or HB*-trees for

placement expansion

14

Review of ASF-B*-tree

Concept of symmetry islands [Lin & Lin, DAC’07]

Matching devices should be placed at proximity to reduce

mismatch [Pelgrom et al., JSSC’89]

Each module should abut at least one of the other modules in the

same symmetry group

A symmetry island defines a symmetric placement, in which

devices form a connected placement

M3

M4

M1

M2

Symmetry group:

S = {(M1 , M2) , (M3 , M4)}

M3

M4

M1

M2

15

Review of ASF-B*-tree

Concept of symmetry islands [Lin & Lin, DAC’07]

Matching devices should be placed at proximity to reduce

mismatch [Pelgrom et al., JSSC’89]

Each module should abut at least one of the other modules in the

same symmetry group

A symmetry island defines a symmetric placement, in which

devices form a connected placement

Automatically symmetric-feasible B*-tree (ASF-B*-tree) is used

to represent a symmetry island

b4s

b1 b3

b2s b3 b1

b0s

b4r

b2r b3r b1r

b0r

n0r

n1r

n2r

n3r

n4r

15

Review of HB*-tree

Hierarchical B*-tree (HB*-tree) deals with the placement of

symmetry islands and non-symmetry modules

Hierarchy nodes can handle the groups which require matching,

symmetry, and proximity constraints

b5

b5

s

4

b1

b0

b

b3

b

1

b

0

n0r

b6

n1r

nS 0

n2

n3

hierarchy node

nS1

b2

n6

n4r

n5r

16

Placement Expansion for Non-symmetry Modules

n0

B*-tree

b2

n1

b0

b1

n2

Congested region

Expansion width is determined

according to congestion map

n0

b2

b0

b1

n1

n2

17

Placement Expansion for Non-symmetry Modules

n0

n0

Expansion height is determined

according to congestion map

b2

n1

n1

b0

b1

n2

n2

b2

b2

b0

b1

b0

b1

17

Placement Expansion for Non-symmetry Modules

n0

b0

b2

b2'

b1

b1'

HB*-tree

nS0

n1r

n2r

n0

b0

b2

b2'

b1

b1'

nS0

18

Placement Expansion for Symmetry Groups

b2

b1

b1'

b2'

n0r

ASF-B*-tree

r

n0r

n1

s

b0

n2r

n1r

b2

b1

b1'

s

b0

b2'

r

r

b1

b2

n2r

r

b0

19

Placement Expansion for Symmetry Groups

ASF-B*-trees guarantee that each symmetry group remains

symmetric after placement expansion

n0r

n1r

b2

b1

b1'

s

b0

b2'

r

r

b1

b2

n2r

r

b0

19

Placement Expansion for Symmetry Groups

ASF-B*-trees guarantee that each symmetry group remains

symmetric after placement expansion

Dummy node only needs to

add half the expansion width

n0r

s

b3

b2

b1

b1'

s

b0

n0r

s

b3

n1r

b2'

r

n2

b2

n3r

r

n1

n3r

b1

b1'

b2'

s

b0

n2r

19

Outline

Introduction to Analog Placement

Routability-driven Analog Placement

Congestion Estimation

Placement Expansion

Proposed Placement Flow

Experimental Results

Conclusion

20

Proposed Placement Flow

Start

Construct Steiner trees for all nets

Input modules, nets,

and constraints

Estimate routing overflow

Generate a placement P

Overcongeste

d?

Yes

Cost calculation

Congestion elimination

1(P) = AP + WP

Minimu

m cost?

No

No

Cost calculation

2(P*) = AP + WP + CP

Yes

Candidate placement P*

Minimu

m cost?

No

Perturbation for

placement P*

Yes

End

Stage 1

Stage 2

21

Proposed Placement Flow

Construct Steiner trees for all nets

Estimate routing overflow

Expand all congested regions

Reconstruct Steiner trees

for all nets

Overcongeste

d?

Yes

No

Congestion elimination

Estimate routing overflow

Overcongeste

d?

No

Cost calculation

Yes

2(P*) = AP + WP + CP

Minimu

m cost?

No

Perturbation for

placement P*

Yes

End

Stage 2

21

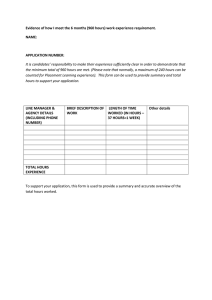

Experimental Results

Platform: 2.5GHz SUN Fire-X4250 workstation with 16GB RAM

Benchmark: two MCNC benchmark circuits

Circuit

# of mod.

# of sym. mod.

Mod. area (mm2)

ami33

33

7 (2+2+2+1)

1.16 = 100%

ami49

49

5 (2+2+1)

35.45 = 100%

22

Experimental Results

Platform: 2.5GHz SUN Fire-X4250 workstation with 16GB RAM

Benchmark: two MCNC benchmark circuits

Without placement expansion

With placement expansion

Circuit

Area

(%)

HPWL

(mm)

# of

overflow

Time

(sec.)

Area

(%)

HPWL

(mm)

# of

overflow

Time

(sec.)

ami33

107.11

37.38

154

103

113.25

47.73

0

556

ami49

108.44

569.25

253

206

115.32

677.24

0

1337

ami33

ami49

22

Experimental Results

Platform: 2.5GHz SUN Fire-X4250 workstation with 16GB RAM

Benchmark: two MCNC benchmark circuits

Symmetry property is maintained after placement expansion

ami33

ami49

22

Conclusion

Analog placement considering routability was introduced

The active areas of all devices are considered as routing blockages

Routing congestion in the resulting placement is minimized

Symmetry constraint must be satisfied after placement expansion

ASF-B*-trees were used for maintaining the symmetry property

after placement expansion

Future work

Consider symmetric routing during the congestion estimation

23

Questions or Comments

Thank you!

24