Microwave Office™

Application Note

INTRODUCTION

To fine-tune an RF/microwave design to meet new design criteria, engineers turn to

the built-in optimizers within their electronic design automation (EDA) software.

A typical optimization case for a microwave filter, for instance, might include goals

for in-band insertion loss and return loss, cutoff frequency, and out-of-band rejection.

The large number of criteria that the optimization engine then has to take into

consideration to create a landscape of “solutions” are more or less random, and,

more often than not, quite large.

This application note presents a method for improved design flow efficiency with a

goal of cost-effective first-pass design success. A solution is proposed that maps the

impact that individual components have on sub-system performance so that a good

trade-off can be made with regard to component values and tolerance (low tolerance

equals more expensive, larger tolerance equals less expensive). This new method

ultimately leads to lower manufacturing costs and improved yield.

MODELITHICS CLR LIBRARY

The proposed solution requires accurate passive component models that enable yield

analysis by means of a tolerance setting. By combining Modelithics Global Models™

or passive RLC components [1] with AWR’s Microwave Office™ high-frequency

design software, the software can be used to find an optimal solution that not only

reaches the design goal more efficiently, but also helps designers find an optimum

component trade-off and a high yield.

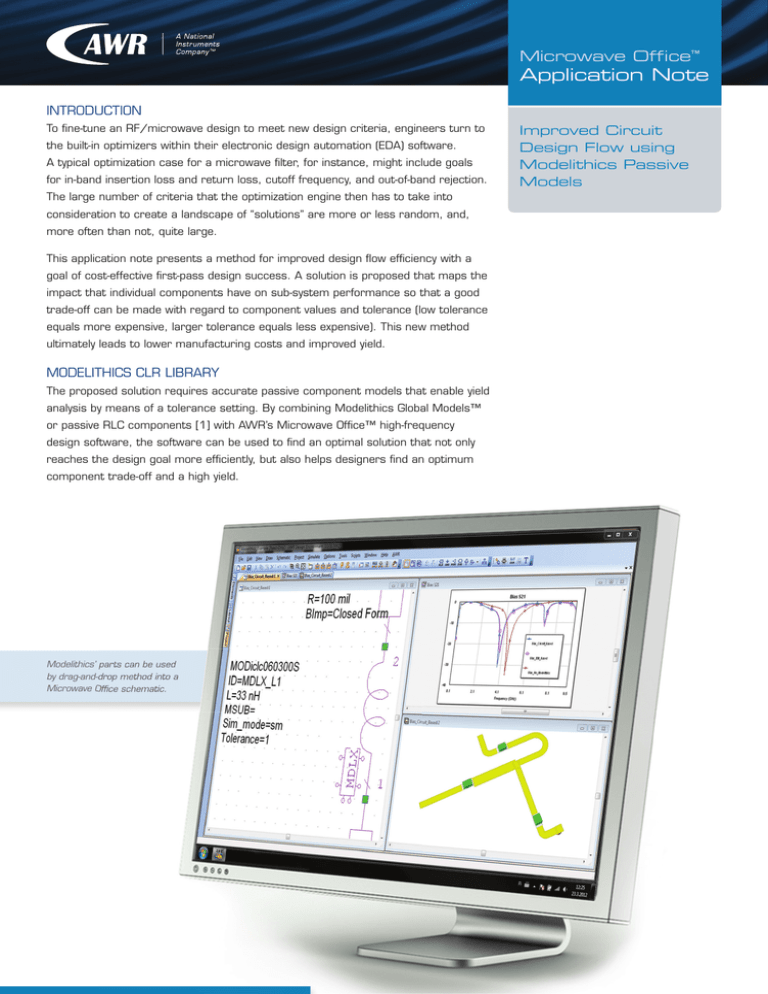

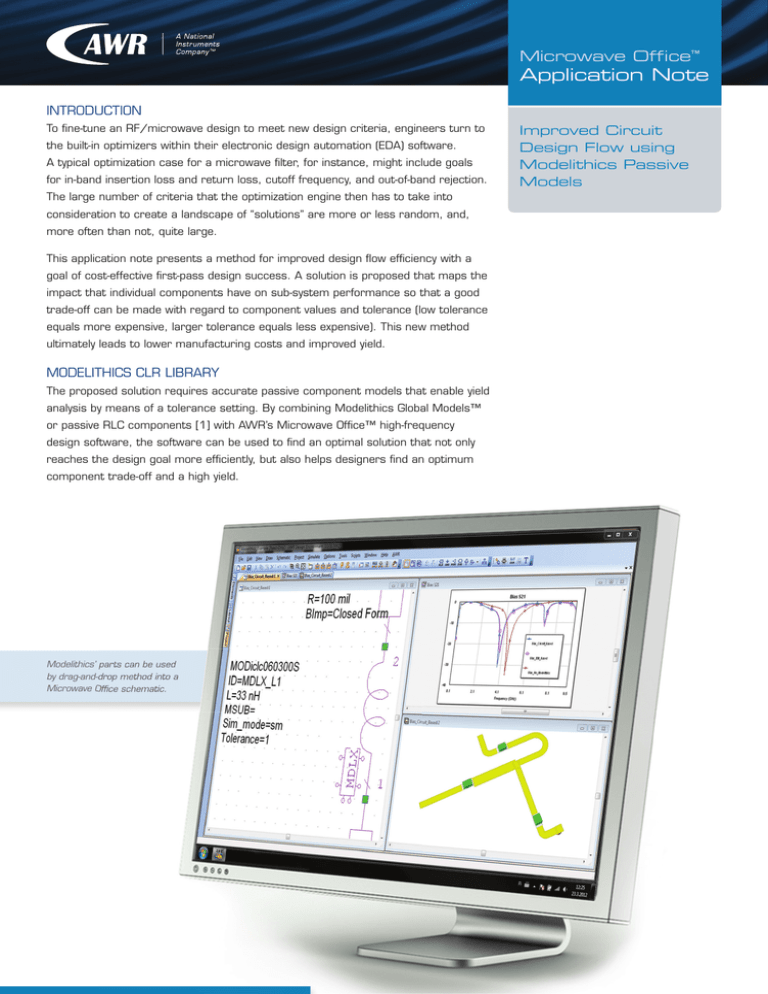

Modelithics’ parts can be used

by drag-and-drop method into a

Microwave Office schematic.

Improved Circuit

Design Flow using

Modelithics Passive

Models

The Modelithics CLR Library offers a wide range of highly scalable Global Models, each

representing an entire family of component values that are scalable based on part value,

substrate, and pad dimension properties. The models are also structured to allow for

statistical tolerance analysis. All models are thoroughly documented with a detailed

model data sheet and available on the Modelithics site: www.modelithics.com/products.

LOW PASS FILTER DESIGN GOALS

A standard low-pass filter (LPF) design is used to demonstrate the proposed new

design flow approach, which involves a simulation-based methodology for yield

estimation and cost-effective yield improvement. Table 1 shows the design goals for

this LPF example. The combination of Modelithics Global Models and AWR Design

Environment™ statistical tools provides a clear advantage over the use of commonly

Goal

Frequency

Range (GHz)

3dB Cutoff Frequency

2.2

< 1dB Insertion Loss

DC to 2.1

> 30dB Out of Band

Rejection

> 12dB Return Loss

3.25 to 8.5

DC to 2.0

Table 1: LPF design goals.

available S-parameter models and traditional design flows.

FILTER DESIGN FLOW

Figure 1 illustrates the filter design flow. It begins with synthesis of an ideal filter. The

next step is to substitute the ideal components with Global Models and eventually add

transmission line effects. An optimization of part values is then done to compensate for

non-idealities and parasitic effects. The result at this point should be a nominal filter design

that has a good match to the goals. Transmission line dimensions can also be optimized

along with the part values to fine tune the design and compensate for the lack of availability of in-between part values that may be required for an even more optimal design.

Figure 1: Filter design flow.

(a) Ideal

Synthesize

& Analyze

(b) Modelithics

Global Model

(c) Modelithics

Model with

TLine Effects

Optimize

Normal

Design

Analyze

Tolerances &

Optimize Yield

Layout/Fab

Measure

The focus of this application note is to improve this flow by adding a tolerance analysis and

yield optimization step prior to fabrication. Electromagnetic (EM) analysis could also be

used to further validate the nominal design simulations, however, built-in transmission line

models are more convenient and computationally efficient to use for tolerance analysis.

The design was synthesized by selecting a 5th order Chebychev filter, with a pass-band

ripple of 0.5dB and a series inductor as a first component. Such designs can be readily

synthesized using filter synthesis software routines such as AWR’s iFilter™ wizard [3].

LPF MEASUREMENT TO MODEL COMPARISON

Figure 2 shows the layout process file (LPF) layout designed to the given specifications,

inclusive of the fabricated test fixture (assembled using tight tolerance part values).

Figure 3 shows the modeled versus measured results. While the model matches the

measurement well, the results do not yet reflect the outcomes that may be achieved in

manufacturing, especially with looser tolerance parts.

Figure 2: Fabricated design (left) and AWR layout

(below) of nominal design.

Figure 3: Simulated (red) and measured

(blue) results for nominal filter. Top=S11 (dB).

Bottom=S21 (dB).

focus will be on the tolerances of the surface mount L-C values. Figure 4 shows the

filter design in the AWR Design Environment. To run statistics with Modelithics Global

Models, a tolerance parameter is enabled and assigned to the anticipated manufacturing distribution. In the first yield analysis, a 5% normal (or Gaussian) distribution

will be assigned to the three inductors and the two capacitors used in the design.

1

MTEE

ID=TL3

W1=W_1 mil

W2=W_1 mil

W3=W_1 mil

MLIN

ID=TL10

W=W_1 mil

L=L_1 mil

MD LX

MSTEP

ID=TL7

W1=W_1 mil

W2=W_3 mil

1

2

MSTEP

ID=TL2

W1=W_1 mil

W2=W_3 mil

MODiclc0402001

ID=CLC_0402CS_L2

L=L2nH

MSUB=

Sim_mode=0

Tolerance=1

PADW=20 mil

MLIN

ID=TL22

W=W_1 mil

L=L_1 mil

1

L1

MTEE

ID=TL13

W1=W_1 mil

W2=W_1 mil

W3=W_1 mil

1

2

MSTEP

ID=TL9

W1=W_1mil

W2=W_3mil

MLIN

ID=TL4

W=W_1 mil

L=L_1 mil

MLIN

ID=TL23

W=W_1mil

L=L_1mil

MD LX

2

3

C1

2

MODcatc600L001

ID=ATC_600L_C1

C=C1 pF

MSUB=

Sim_mode=0

Tolerance=1

PADW=22 mil

PADL=18mil

PADG=16 mil

MSTEP

ID=TL5

W1=W_1 mil

W2=W_4 mil

VIA

ID=V1

D=10 mil

H=19 mil

T=1.7 mil

RHO=1

MLIN

ID=TL59

W=W_1 mil

L=105.9 mil

M DL X

1

2

MSTEP

ID=TL12

W1=W_1 mil

W2=W_3 mil

L2

MSTEP

ID=TL11

W1=W_1 mil

W2=W_3 mil

L3

MLIN

ID=TL14

W=W_1 mil

L=L_1 mil

MSTEP

ID=TL6

W1=W_5mil

W2=W_4mil

1

MODiclc0402001

ID=CLC_0402CS_L3

L=L3 nH

MSUB=

Sim_mode=0

Tolerance=1

PADW=20 mil

MLIN

ID=TL19

W=W_1 mil

L=L_1 mil

2

3

MSTEP

ID=TL8

W1=W_1mil

W2=W_3mil

MSTEP

ID=TL15

W1=W_1 mil

W2=W_4 mil

1

MD LX

The design shown previously is now the starting point for the tolerance analysis. The

MODiclc0402001

ID=CLC_0402CS_L1

L=L1nH

MSUB=

Sim_mode=0

Tolerance=1

PADW=20 mil

MLIN

ID=TL1

W=W_1 mil

L=105.9mil

MD LX

YIELD ANALYSIS

C2

2

MODcatc600L001

ID=ATC_600L_C2

C=C2 pF

MSUB=

Sim_mode=0

Tolerance=1

PADW=22 mil

PADL=18mil

PADG=16 mil

MSTEP

ID=TL16

W1=W_5mil

W2=W_4mil

VIA

ID=V2

D=10 mil

H=19 mil

T=1.7 mil

RHO=1

MSUB

Er=3.38

H=16mil

T=1.7 mil

Rho=1

Tand=0.0031

ErNom=3.38

Name=SUB1

L1=2.7

L2=5.1

C1=1.8

L3=2.7

C2=1.8

W_1=35.27

W_3=26

W_4=22

W_5=24

L_1=20

Figure 4: LPF with optimized values:

L1 = L3 = 2.7nH; L2 = 5.1nH; C1= C2 =1.8pF.

A yield analysis is then performed, using 500 iterations, which resulted with an initial

yield of 54% for the design specifications shown earlier in Table 1. These yield goals

are set up as the limit bars on the graphs shown in Figure 5. The S11 and S21

results are also shown, with the nominal design being the dark line.

It is common practice for some components to have tight tolerance parts selected

or “binned” from the middle of a manufacturing lot. This results in a binominal or

“normal with a gap” distribution if loose tolerance parts are purchased. This type

of distribution can be simulated in Microwave Office™ with a distribution called

“Normal-Tol,” which allows for specifying two values, one being the tight tolerance

percentage that has been chopped out and the other being the overall manufacturing

distribution from which the tight tolerance parts have been selected. Using this type

of distribution for all the L-C components actually reduces the yield to 45 %. With

this distribution, none of the design simulations will have nominal part values.

The tight tolerance parts that would have been selected from the middle of such a

binned distribution approach would not really be normal or Gaussian. To account for this,

Microwave Office has an inverse distribution called “normal-clipped.” If it is first assumed

that only the capacitors, then only the inductors have this type of 2% tight tolerance

(normal-clipped) distribution, slightly higher yields of 50% and 47%, respectively, can be

achieved. If it is assumed that all the inductors and capacitors have this tight tolerance

distribution, the yield can be increased to 85%. However, this is an expensive design

Figure 5: Initial yield analysis results.

Top=S11 (dB). Bottom= S21 (dB).

Design specs: |S11dB| < -12 from DC

to 2.0GHz; |S21dB| > -3 from DC to 2.2GHz;

|S21dB| < -30 from 3.25-8.5GHz

now. It would be prudent to find another way to reduce the cost and achieve this yield.

SENSITIVITY ANALYSIS

As a byproduct of yield analysis, the Microwave Office simulation can be set up to

output sensitivity graphs for all the varied parameters. These graphs can help the

user quickly identify to which parameters the design performance is sensitive and to

which it is not. It can also suggest a direction to change a parameter for improved

yield and realize what is often referred to as “design centering.”

Figure 6 shows sensitivity graphs of the L1 and L2 inductors. The results shown

are after 1000 iterations with 5/2% normal-tol distributions for all components.

In Microwave Office, the yield analysis output measurement parameter “ysens” is

used to generate this information after setting up a rectangular graph. In using this

output parameter with Modelithics Global models, it is recommended to set ysens to

the tolerance parameter of the component of interest (and not the part value itself).

From the data shown in Figure 6, it can be seen that the yield can be improved with

a lower value of L2, while it seems less sensitive to L1. The analysis shows that

the yield is reasonably centered on the L1 value, but may provide better yield with a

lower value of L2. Examination of the sensitivity graphs for the remaining parameters

(not shown for brevity) show that the design was reasonably centered or insensitive

to the other component values.

Figure 6: Sensitivity analysis results.

Top=L1. Bottom=L2.

Understanding the results of the sensitivity analysis, it is possible to explore how

the yield results might change by lowering the value of L2 from its nominal value

of 5.1nH. The Modelithics model datasheet is one way to identify the available

discrete values the user might select as a substitution. Referring to details within

the datasheet for the selected inductor, the next lower values from nominal (5.1nH)

in the table are 4.7nH and 4.3nH. The value 4.7nH was selected and the tolerance

analysis repeated.

YIELD RESULTS AFTER SENSITIVITY ANALYSIS

The inductor value substitution resulted in immediate yield improvement. After

changing L2 to 4.7nH, yield for the case of all 5% loose tolerance part values

improved to 69% (up from 54%).

Further improvements to 80% and 93% are realized by using tighter 2% tolerance

parts for inductors-only and capacitors-only, respectively. The use of tight tolerance parts

for all inductors and capacitors produces a simulated yield of 100% or 99% if we factor

in 5% tolerances on the substrate height and dielectric constant and +/- 1mil on line

widths. Figures 7 shows the results of 99% yield.

S11 Magnitude Low pass filter_Sim

0

S21 Magnitude Lowpass pass filter_Sim

50

-10

-20

0

DB(|S(1,1)|)

Low_pass_filter

-30

~99% yield

(2% C’s /2% L’s)

-50

-40

-50

-60

DB (|S(2 ,1) |)

Lo w _p a ss_ fil te r

-100

0.05

2.05

4.05

6.05

Fr equen cy ( GHz)

8.05

10

0.05

2.05

4.0 5

6.0 5

Frequen cy ( GHz)

8 .05

10

Figure 7: 99% yield design. Left=S11 (dB). Right=S21 (dB).

CONCLUSION

This application note illustrates a complete design flow with the use of statistically enabled

models for yield and sensitivity analyses. It demonstrates that, starting with an ideal

design, a nominal design that has good agreement to measurements can be achieved and

then adjusted for improved yield while accounting for anticipated manufacturing tolerances.

This same design flow is not possible with S-parameter models.

References

[1] “Comprehensive Models for RLC

Components to Accelerate PCB Designs,”

Microwave Journal, May 2004.

[2] G. Matthaei, L. Young and E.M.T. Jones,

Microwave Filters, Impedance-Matching

Networks and Coupling Structures, 1964

McGraw Hill.

AWR Corporation thanks Dr. Larry

Dunleavy, CEO of Modelithics, for his

contributions to this application note.

Copyright © 2012 AWR Corporation. All rights reserved. AWR is a registered trademarks and the AWR logo, Microwave

Office, AWR Design Environment and iFilter are trademarks of AWR Corporation. Other product and company names listed

are trademarks or trade names of their respective companies.

AN-MDL-DF-2012.10.11

AWR Corporation | www.awrcorp.com

info@awrcorp.com | +1 (310) 726-3000