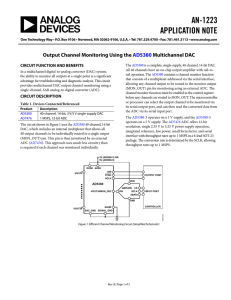

Built-in Self-Test and Calibration of Mixed

advertisement