5

4

3

2

1

D

D

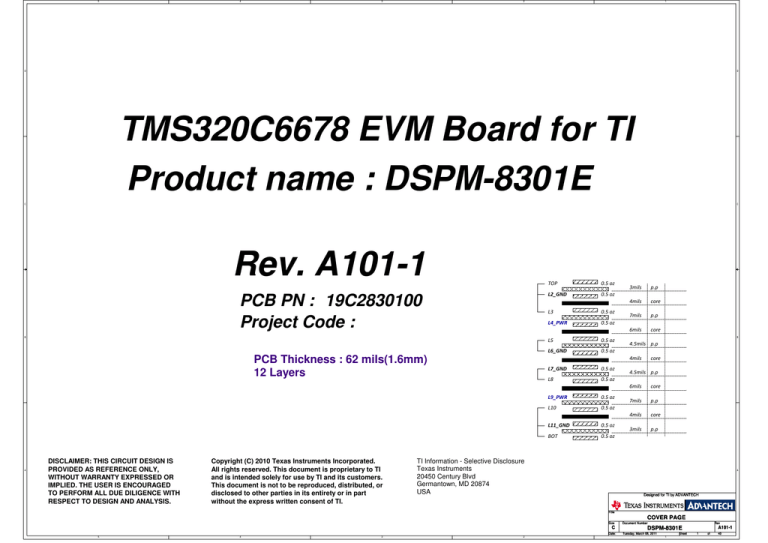

TMS320C6678 EVM Board for TI

Product name : DSPM-8301E

C

C

Rev. A101-1

PCB PN : 19C2830100

Project Code :

B

PCB Thickness : 62 mils(1.6mm)

12 Layers

A

DISCLAIMER: THIS CIRCUIT DESIGN IS

PROVIDED AS REFERENCE ONLY,

WITHOUT WARRANTY EXPRESSED OR

IMPLIED. THE USER IS ENCOURAGED

TO PERFORM ALL DUE DILIGENCE WITH

RESPECT TO DESIGN AND ANALYSIS.

Copyright (C) 2010 Texas Instruments Incorporated.

All rights reserved. This document is proprietary to TI

and is intended solely for use by TI and its customers.

This document is not to be reproduced, distributed, or

disclosed to other parties in its entirety or in part

without the express written consent of TI.

TOP

0.5 oz

L2_GND

0.5 oz

L3

0.5 oz

L4_PWR

0.5 oz

L5

0.5 oz

L6_GND

0.5 oz

L7_GND

0.5 oz

L8

0.5 oz

L9_PWR

0.5 oz

L10

0.5 oz

L11_GND

0.5 oz

BOT

0.5 oz

3mils

p.p

4mils

core

7mils

p.p

6mils

core

B

4.5mils p.p

core

4mils

TI Information - Selective Disclosure

Texas Instruments

20450 Century Blvd

Germantown, MD 20874

USA

4.5mils p.p

6mils

core

7mils

p.p

4mils

core

3mils

p.p

A

Designed for TI by ADVANTECH

Title

COVER PAGE

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

1

of

40

5

4

3

2

1

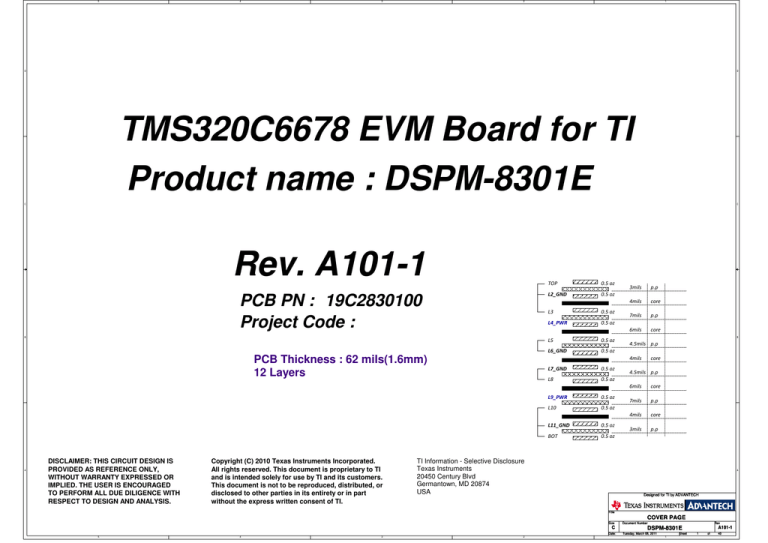

TITLE & TABLE OF CONTENTS

Page

D

Description

Page

Description

01

COVER PAGE

31

FPGA_XC3S200AN_B

02

TITLE & TABLE OF CONTENTS

32

FPGA_XC3S200AN_C

03

BLOCK DIAGRAM_AMC

33

Power ucd9222

04

POWER SEQUENCE

34

Power_1.2V/1.8V/2.5V/0.75V

05

POWER CONSUMPTION

35

Power_VCC5 / VCC3V3_AUX

06

POWER DISTRIBUTION

36

Power VCC1V5

07

CLOCK DIAGRAM

37

History_0

08

FPGA_BLOCK

38

09

BUS Management Map

39

10

AMC GF

11

MMC

12

DSP_SERDES_PORTS

13

DSP_DDR3

14

DSP_EMIF

15

DSP_JTAG_EMU_TSIP

16

DSP_MISC

17

DSP_CLOCK_Smart Reflex

18

DSP_POWERA

19

DSP_POWERB

20

DSP_POWERC

21

DSP_GND

22

CLOCK_GEN1

23

CLOCK GEN2

24

DDR3

25

DDR3_ECC

26

USB-JTAG

27

Gigabit Ethernet PHY

28

RJ45

29

Connectors for HyperLink & Debug

30

FPGA_XC3S200AN_A

D

C

C

B

A

B

A

Designed for TI by ADVANTECH

Title

TITLE & TABLE OF CONTENTS

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

2

of

40

5

4

3

2

1

BLOCK DIAGRAM_AMC

AMC Board

AMC_State

MMC JTAG

SPI EEPROM

SYSPG_D1 LED

FPGA_DONE LED

JTAG

User controlled LED - 4

1. 64M X 16 / 512MB

2. 128M X 16 / 1GB

ROM_SPI

MMC

XC3S200AN

(XILINX)

CDCE62005

CLK_SPI2

CLK_SPI3

CLK#2

Sequence

Control

JTAG & EMU[0:1]

CH-A

USB-JTAG

FT2232HL

CH-B

DSP_UART

UART

EEPROM

PIN

PIN

Port mapping

2

1

Power Control

Power

RAM

DSP

FPGA PHY

Others

PWR CONN

RS232

MAX3221EAE

PIN

Port mapping

Port mapping

PIN

Port mapping

PIN

01

GND

41

EMIFCE2Z

EMIFA21

03

SDA

43

EMIFBE0z

46

EMIFA22

05

SCL

45

EMIFBE1z

EMIFA03

48

EMIFA23

07

EMIFD0

47

EMIFOEz

EMIFA04

50

GPIO00

09

EMIFD1

49

EMIFWEz

12

EMIFA05

52

GPIO01

11

EMIFD2

51

EMIFRnW

14

EMIFA06

54

GPIO02

13

EMIFD3

53

EMIFWAIT1

16

EMIFA07

56

GPIO03

15

EMIFD4

55

TIMI0

18

EMIFA08

58

GPIO04

17

EMIFD5

57

TIMO0

20

EMIFA09

60

GPIO05

19

EMIFD6

59

TIMI1

22

EMIFA10

62

GPIO06

21

EMIFD7

61

TIMO1

24

EMIFA11

64

GPIO07

23

EMIFD8

63

SSPMISO

26

EMIFA12

66

GPIO08

25

EMIFD9

65

SSPMOSI

28

EMIFA13

68

GPIO09

27

EMIFD10

67

SSPCS1

30

EMIFA14

70

GPIO10

29

EMIFD11

69

SSPCK

32

EMIFA15

72

GPIO11

31

EMIFD12

71

UARTTXD

34

EMIFA16

74

GPIO12

33

EMIFD13

73

UARTRXD

36

EMIFA17

76

GPIO13

35

EMIFD14

75

UARTRTS

38

EMIFA18

78

GPIO14

37

EMIFD15

77

UARTCTS

Title

39

EMIFCE1Z

79

GND

Size

02

EMIFA00

42

EMIFA20

04

EMIFA01

44

06

EMIFA02

08

10

80

40

EMIFA19

80

GPIO15

4

TSIP_CLK0

11

SRIO_4

TCLKB

TSIP_CLK1

12

TSIP0 [0..3]

100MHz

13

TSIP1 [0..3]

SGMII

14

FCLKA

00

01

15

02

16

03

04

PCI-E_1

05

PCI-E_2

B

Alternate I2C link

TCLKC

TSIP_FS0

TCLKD

TSIP_FS1

17

06

18

07

19

08

SRIO_1

09

SRIO_2

10

SRIO_3

20

A

Designed for TI by ADVANTECH

BLOCK DIAGRAM_AMC

79

3

Port mapping

TCLKA

C

Date:

5

C

AMC Port mapping

B

A

POWER 12V

128k-byte

Miscellaneous I/O 80 Pin conn. Signal

Port mapping

TSIPx2

Pin-Header 3x1

2.54mm

DSP_SGMII_P1 & MDIO

PIN

Level-Shifter

DSP_I2C

DSP_UART

JTAG & EMU[0:1]

DSP_SGMII_P1 & MDIO

SWITCH

(TS3L301)

DSP_I2C(1.8V)

DSP_UART(3.3V)

DSP_SPI(1.8V)

EMIF16(1.8V)

GPIO[0:15](1.8V)

USB

TSIPx2

M24M01-HRMN6TP

EMU[2:17]

ENET PHY

Mini-USB

SRIOx4

NU Resistors

EMU[2:17]

MAC1

JTAG&EMU[0:1] MDIO

60-Pin EMU CONN.

Miscellaneous I/O conn.

PCIEx2

PCIEx2

I2C

BM_GPIO(0~15) /

PCIESSEN / User define

Power Control

D

SGMIIx1

MAC0

TSIPx2

DIP SW

MMC

MMC_LED1

MMC_LED2

SRIOx4

GPIO

IPMB-L

(MSP430)

EMIF

SPI

88E1111-B2

C

Hyper Link

DSP

TMS320C6678

GPIO[0:15]

DIP_SWITCH

CDCE62005

RJ45

DDR3

JTAG

+V3.3_MP

AMC_State

EMIF

HyperLink

50Gbps

DDR3-1333

w/ ECC

DSP_GPIO

NAND FLASH

(512Mb 64M X8)

NAND512R3A2D

ZA6E

to FPGA

NOR 128M-bit

N25Q128A21BSF40F #0

SPI

DSP_SPI#1

FPGA

iPass+HD

SPI Flash

DEBUG_LED

CLK#1

HyperLink CONN.

1. 1Gb X 16

2. 1Gb X 8

DDR3 -1333

128k-bit

AT25128B

MUX

JTAG

D

MUX

FPGA JTAG

DDR3(ECC)

1

from MMC

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

3

of

40

5

4

3

Power Sequence

S0

VCC3V3_MP

MMC

S1

Other

FT2232H XC3S200AN

VCC3V3_AUX

XC3S200AN

VCC1V8_AUX

XC3S200AN

VCC1V2

S3

T0

1ms

S4

Description

S2 plane power stable to S3 enable signal assertion

88E1111

S5

PMBUS &

UCD9222_ENA1

S6

CVDD

DSP TMS320C6678

S7

UCD9222_VID2 &

UCD9222_ENA2

S8

VCC1V0

DSP TMS320C6678

S9

T=5mS

T=5mS

T=5mS

VCC1V8_EN

S10

C

D

VCC12

S2

Time

1

VCC3V3_MP_AMC

D

Label

2

DSP TMS320C6678

S11

S12

DDR3

DSP TMS320C6678

C

T=5mS

DDR3 SDRAM

VCC1V5

VCC0V75_EN

DDR3

DSP TMS320C6678

S15

T=5mS

DDR3 Vref

VCC0V75

VCC2V5_EN

S16

VCC2V5

88E1111

S17

S18

T=5mS

VCC1V8

VCC1V5_EN

S13

S14

Power Sequence

VCC5_EN

XDS560V2 Mazzenine Board

VCC5

T=0mS

RESET#

including peripherals.

B

T=5mS

POR#

B

Reset Sequence

T=5mS

RESETFULL#

by DSP chip

RESETSTAT#

REFCLKP&N

by REFCLK2_PD#

CLOCK2_PLL_LOCK

CLK Sequence

DDRCLKP&N

by REFCLK3_PD#

DSP

TMS320C6678

VCC1V8

VCC1V0 Scaled/(CVDD)

VCC1V0 Fixed/(CVDD1)

VCC1V8/ (DVDD18)

1.5V/(DDR3_IO)

0.75V/(DDR3_Vref)

0ms<t<100us

0ms<t<100ms

VCC_1V0 scaled

VCC_1V0 Fixed

DSP

TMS320C6678

0.75V (DSP)

0ms<t<100us

1.5V/(DDR3_IO)

0.75V/(DDR3_Vref)

VCC_1V0 Fixed

1.5V/(DDR3_IO)

0.75V/(DDR3_Vref)

1.5V (DSP)

When power down

VCC1V8

VCC1V8

A

0ms<t<100us

0ms<t<100us

1.0V_fixed

VCC_1V0 scaled

0ms<t<100us

3.3V / 1.8V/ 1.2V

VDD

CLOCK3_PLL_LOCK

XILINX_XC3S200AN

A

VDD

Designed for TI by ADVANTECH

88E1111 (PHY)

Ther is no specific power-up nor

power-down sequence.

2.5V/ 1.2V

When power on

1.2V_AUX (VCCINT)

1.8V_AUX (VCC1V8_AUX)

3.3V_AUX (VCCAUX)

1.0V_scaled

XILINX_XC3S200AN

Ther is no specific power-up nor

power-down sequence.

88E1111

Title

Power Sequence

2.5V

1.2V

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

4

of

40

5

4

3

2

1

POWER CONSUMPTION

D

D

C

C

B

B

A

A

Designed for TI by ADVANTECH

Title

POWER CONSUMPTION

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

5

of

40

5

4

3

2

1

POWER DISTRIBUTION

AMC Gold Finger

D

3.3V_MP

165uA

VCC3V3_MP_AMC @ 165uA

D

Efficiency=80%

VCC12

3.04A

1.4A

PM_BUS

SmartReflex

CVDD @ 8A

UCD9222 +

UCD7242

VCC1V0 @ 5A

UCD9222_ENA [ 1..2]

XILINX_XC3S200AN

1.2V_AUX/ 0.125A (VCCINT)

3.3V_AUX/ 0.024A (VCCAUX)

DSP

TMS320C6678

DC Jack

VCC1V0 / 8A Scaled/(CVDD)

VCC1V0 / 5A Fixed/(CVDD1)

VCC1V8 / 0.33A (DVDD18)

1.5V / 0.85A (DDR3_IO)

0.75V/(DDR3_Vref)

Efficiency=90%

2.585

C

0.79A

C

VCC3V3_AUX @1.2A

TPS54620

DDR3

1.5V / 1.2A (DDR3_VDD)

0.75V / 0.25A (DDR3_Vref)

TPS73701DCQ

VCC1V2 @0.375A

88E1111 (PHY)

2.5V / 0.21A

1.2V / 0.25A

FT2232H(USB-JTAG)

TPS73701DCQ

3.3V / 0.21A

VCC1V8_AUX @0.3A

RS232

3.3V

TPS73701DCQ

VCC1V8_EN1

B

VCC1V8 @0.5A

B

FLASH

1.8V

TPS73701DCQ

VCC2V5_EN

VCC2V5 @0.21A

SPI NOR FLASH

1.8V

Efficiency=90%

0.33A

XDS560V2

Mazzenine Board

2.35A

TPS54620

5.0V / 1A

3.3V / 0.3A

VCC1V5 @2.1A

VCC1V5_EN

VCC0V75_EN

TPS51200

(3.3 Control)

VCC0V75 @0.25A

A

A

Efficiency=80%

0.52A

TPS54231

VCC_5V_EN

VCC5 @1A

Designed for TI by ADVANTECH

Title

POWER DISTRIBUTION

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

6

of

40

5

4

3

2

1

NU

AC-coupling

capacitors

CLOCK DIAGRAM

100MHz

PCIe_CLKP/N (AMC)

AC-coupling

capacitors

100.00MHz

D

U0

CDCE62005

PRI_REF

PCIe_CLKP/N

DSP

TMS320C6678

D

X'TAL

312.50MHz

U2

312.50MHz

SRIO_SGMII_CLKP/N

U3

100.00MHz

PA_SS_CLKP/N

FT2232HL

12MHZ

MCM_CLKP/N

For HyperLink

U1

U4

U0

X'TAL

100.00MHz

88E1111

25MHZ

U1

X'TAL

CDCE62005

25MHZ

C

U2

66.667MHz

DDR_CLKP/N

U3

100MHz

CORE_CLKP/N

C

U4

XILINX

XC3S200AN

TSIP CLOCK

TSIP0_CLKA

TDM_CLKA +/TDM_CLKB +/-

+

TSIP0_CLKB

TSIP1_CLKA

TSIP1_CLKB

B

B

TSIP Frame Sync

100MHz

PCIe_CLKP/N (AMC)

TSIP0_FSA

TDM_CLKC +/TDM_CLKD +/-

+

TSIP0_FSB

-

TSIP1_FSA

TSIP1_FSB

AMC Gold Finger

A

A

Designed for TI by ADVANTECH

Title

CLOCK DIAGRAM

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

7

of

40

5

4

3

TI MMC

TI_MSP430F5435IPN

MMC

Control

SPI_MMC_CS#

SPI_MMC_MISO

SPI_MMC_SCK

SPI_MMC_MOSI

PIN HEADER

+V3.3

+V3.3

MMC_DETECT#

MMC_RESETSTAT#

MMC_POR#

MMC_WARM_RST#

1

PM BUS

TMS320C6678 EVM (AMC)

XILINX_XC3S200AN-4FTG256C

FPGA_BLOCK

D

2

UCD9222

Control

PMBUS_ALT#

PMBUS_CTL

PMBUS_CLK

PMBUS_DAT

Alert

Control

Clk

Data

PGUCD9222

UCD9222_RST

UCD9222_PG1

UCD9222_ENA1

UCD9222_PG2

UCD9222_ENA2

PG

RESET

PG1

ENA1

PG2

ENA2

UCD9222_VID2

UCD9222_VID2

D

TI UCD9222

+V3.3

VCC2V5_PGOOD

VCC0V75_PGOOD

VCC3V3_AUX_PGOOD

VCC5_PGOOD

VCC1V5_PGOOD

Power Group

+V1.8

Power

Sequences

Control

TI_TPS54620RGY x3

TI_TPS73701DRBT x4

TI_TPS54231D x1

C

VCC2V5_EN

VCC0V75_EN

VCC1V8_EN1

VCC5_EN

VCC1V5_EN

PCIESSEN

User Switch

DSP

Default : TBD

Default : TBD

+V1.8

Boot & Device

configurations

GPIO[0:3] GPIO[8:11]

GPIO[4:7] GPIO[12:15]

BM_GPIO[0 : 15]

+V1.8 DSP_GPIO[0 : 15]

Test Connector 80-pin

(Female)

C

TIMI0

+V3.3

SPI_CLK_CS#[1..2]

CLOCK Group

SPI_CLK_CK[1..2]

TI_CDCE62005 #1

TI_CDCE62005 #2

SPI_CLK_MOSI[1..2]

GPIO[0:15]

TIMI[0]

+V1.8

CLOCK

Configurations

DSP_POR#

DSP_RESETFULL#

DSP_RESET#

DSP_PACLKSEL

DSP_LRRESETNMIEN#

DSP_CORESEL[0..3]#

DSP_NMI#

DSP_LRESET#

DSP_BOOTCOMPLETE

DSP_HOUT

DSP_SYSCLKOUT

DSP

RESET &

Interrupts

Control

SPI_CLK_MISO[1..2]

REFCLK1_PD#[1..2]

PLL_LOCK[1..2]

POR#

RESETFULL#

RESET#

PACLKSEL

LRRESETNMIEN#

CORESEL[0:3]

NMI#

LRESET#

BOOTCOMPLETE

HOUT

SYSCLKOUT

DSP

TMS320C6678

SPI_FPGA_CS1

DSP

SPI_FPGA_MISO

SPI_FPGA_SCK

SPI_FPGA_MOSI

SPI

MARVELL

B

PHY_INT#

PHY_RST#

PHY

Control

SPI ROM

ATMEL

AT25128B

B

+V3.3

88E1111-B2

+V1.8

DSP_TDM_FS[0:1]A/B

TDM CLK

DSP_TDM_CLK[0:1]A/B TDM_CLK[0:1] A/B

+V3.3

CS#

SPI_FPGA_CS#

MISO

SPI_FPGA_MISO

CLK

SPI_FPGA_SCK

MOSI

SPI_FPGA_MOSI

TDM_FS[0:1] A/B

DSP

LVDS

AMC_TDM_CLKA/B[p/n]

AMC_TDM_CLKC/D[p/n]

FPGA

Storage

AMC Edge Connector

(Golden Finger)

+V3.3

FPGA_JTAG_TCK

+V3.3

COLD RESET

WARM RESET

A

RESET

FPGA

JTAG

FULL RESET

TRGRSTZ

60-pin emulation

BSC_JTAG_TCK

BSC_JTAG_TDO

FPGA_JTAG_TDI

FPGA_JTAG_TDO

Buffer

BSC_JTAG_TDI

FPGA_JTAG_TMS

BSC_JTAG_TMS

FPGA_JTAG_RST#

BSC_JTAG_RST#

Designed for TI by ADVANTECH

Title

+V1.8

FPGA_BLOCK

(Female)

Size

B

Date:

5

A

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

8

of

40

5

4

3

2

1

Management Map

EMU_DETz

D

MDC

ENET PHY MDI/O

(88E1111) JTAG

MDC

MDI/O

+V2.5

Level Shifter

PCA9306DCUT

MDC

MDI/O

SEL

MDC

MDI/O

+V1.8

JTAG

+V1.8

EMU CONN.

JTAG

High-Speed

SWITCH

(TS3L301)

JTAG

EMU_DET PIN

+V1.8

D

JTAG

Level Shifter

+V1.8

JTAG

DSP

TMS320C6678

( 0xA0h )

I2C

I2C

UART

UART

+V1.8

DSP_RESETSTAT#

Level Shifter

SN74AVC4T245

EEPROM

(24AA1025)

(128KB)

+V3.3

USB-JTAG

FT2232HL

UART

+V3.3

Mini-USB

Console port

(Jumper Option)

RS232

MAX3221EAE

SPI (CS1z)

RESETZ#

POR#

RESETFULLZ#

C

USB

RS232

(Pin-Header 3x1)

80-pin Header

C

MSP430 (MMC)

NU Resistors

SPI1

JTAG

The NU resistors on these connections to the MSP430 are for debug use only

and will be used only with the shunts removed from pins 1 and 2 of CN7

Power Sequences Control

GPIO

PMBus

0-ohm

FPGA

(XILINX_XC3S200AN)

SmartReflex

(UCD9222)

JTAG

JTAG and

Boundary Scan

CN10

JTAG

CDCE62005

SPI2

TDO

TDI

DSP_RESETSTAT#

SPI3

TMS/TCK/TRSTn

CDCE62005

SPI

JTAG_EN# Buffer1

BS_EN#_1

Buffer2

B

B

WARM_RESET_AMC#

AMC_DETECT#

FP_POR_IN_AMC#

MMC_RESETSTAT#

MMC

(MSP430)

EEPROM

(AT25128B)

(128kb)

TDI

TDO

FPGA

XC3S200AN

JTAG

Buffer2

JTAG

IPMB-L

TDO

TDI

MMC_ENABLE_N

UCD9222

Level Shifter

PCA9306DCUT

PHY (88E1111)

JTAG

I2C

JTAG

TDI

NU Resistors

A

TDO

Buffer2

A

AMC Gold Finger

Designed for TI by ADVANTECH

MMC_PS_N0

Title

MMC_PS_N1

Management Map

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

9

of

40

5

4

3

2

OVP: ~12.7V+0.6V = ~13.3V

FAN1

Front panel and ESD Strip

1

2

3

1

VCC12

DC_IN1

5%

R937

JACK_3H

10M

TRIP2

TRIP3

2

3

2

C525

1uF

16V

D

R931

100K

5%

R932

100K

5%

D

ESD1

R935

1K

5%

AMC-ESD-B

1

VCC12

2

1

R934

100K

5%

G

Q11

2N7002

300mA/60v

S

3

TRIP1

1

4

VCC12

C466

10uF

16V

5%

1

TRIP1

R930

1uF

25V

100K

5%

1

10M

D12

BZX84-C12

12.7V

3

R936

C516

1000pF

50V

Q12

MMBT3904LT1

200mA

C549

0.1uF

50V

R933

100K

5%

2

5%

D

C552

C550

0.1uF

50V

Q10

AO3401

4.2A/30V

3

G

NL/0

WB_3V_2.0mm

3

5%

S

R157

NL/0

2

D

R158

1

3

2

C526

1uF

16V

AMC1

IN

IN

(12)

(12)

AMC0_SGMII0_RX_DP

AMC0_SGMII0_RX_DN

(11)

MMC_GA1

AMC0_SGMII0_TX_DP

AMC0_SGMII0_TX_DN

OUT

OUT

AMC0_SGMII0_RX_DP

AMC0_SGMII0_RX_DN

MMC_GA1

IN

C

(11)

MMC_GA2

(11)

MMC_ENABLE_N

AMCC_P4_PCIe_TX1P

AMCC_P4_PCIe_TX1N

(12)

(12)

IN

IN

OUT

C301

C302

AMCC_P4_PCIe_RX1P

AMCC_P4_PCIe_RX1N

AMCC_P5_PCIe_TX2P

AMCC_P5_PCIe_TX2N

B

IN

IN

MMC_GA2

IN

OUT

OUT

C326

C369

AMCC_P5_PCIe_RX2P

AMCC_P5_PCIe_RX2N

OUT

OUT

(11)

SMB_SCL_IPMBL

OUT

BI

(30)

(30)

TDM_CLKA_P

TDM_CLKA_N

OUT

OUT

(30)

(30)

TDM_CLKB_P

TDM_CLKB_N

OUT

OUT

(17)

(17)

MMC_PS_N1

PCIE_REF_CLK_P

PCIE_REF_CLK_N

1

D3

ASD500V

100mA

2

AMCC_P4_PCIe_TX1P_C

(12)

AMCC_P4_PCIe_TX1N_C

(12)

AMCC_P4_PCIe_RX1P

AMCC_P4_PCIe_RX1N

0.1uF 16V

0.1uF 16V

(12)

(12)

SMB_SDA_IPMBL

MMC_ENABLE_N

0.1uF 16V

0.1uF 16V

AMCC_P5_PCIe_TX2P_C

(12)

AMCC_P5_PCIe_TX2N_C

(12)

AMCC_P5_PCIe_RX2P

AMCC_P5_PCIe_RX2N

SMB_SCL_IPMBL

SMB_SDA_IPMBL

(11)

TDM_CLKA_P

TDM_CLKA_N

TDM_CLKB_P

TDM_CLKB_N

OUT

OUT

MMC_PS_N0

VCC1V8

VCC3V3_AUX

R339

100K

1%

C355

0.1uF

16V

(16,29)

DSP_SCL

DSP_SDA

VCC1V8

TDM_CLKD_P

TDM_CLKD_N

TDM_CLKC_P

TDM_CLKC_N

R160

R161

NL/0

NL/0

OUT

OUT

TDM_CLKD_P

TDM_CLKD_N

(30)

(30)

OUT

OUT

TDM_CLKC_P

TDM_CLKC_N

(30)

(30)

VCC3V3_AUX

DSP_SDA_AMC

DSP_SCL_AMC

20

18

17

16

15

14

13

12

AMCC_P13_TDM1_TX2

AMCC_P13_TDM1_TX0

AMCC_P12_TDM0_TX3

AMCC_P12_TDM0_TX1

B1

B2

B3

B4

B5

B6

B7

B8

AMCC_P12_TDM0_TX2

AMCC_P12_TDM0_TX0

AMCC_P11_SRIO4_TXP

AMCC_P11_SRIO4_TXN

IN

IN

AMCC_P11_SRIO4_RXP

AMCC_P11_SRIO4_RXN

AMCC_P10_SRIO3_TXP

AMCC_P10_SRIO3_TXN

AMCC_P10_SRIO3_RXP

AMCC_P10_SRIO3_RXN

OUT

OUT

IN

IN

OUT

OUT

AMCC_P9_SRIO2_TXP

AMCC_P9_SRIO2_TXN

AMCC_P8_SRIO1_TXP

AMCC_P8_SRIO1_TXN

AMCC_P8_SRIO1_RXP

AMCC_P8_SRIO1_RXN

OUT

OUT

AMCC_P11_SRIO4_RXP

AMCC_P11_SRIO4_RXN

(12)

(12)

(12)

(12)

AMCC_P10_SRIO3_RXP

AMCC_P10_SRIO3_RXN

(12)

(12)

OUT

OUT

IN

IN

(12)

(12)

AMCC_P10_SRIO3_TXP

AMCC_P10_SRIO3_TXN

IN

IN

AMCC_P9_SRIO2_RXP

AMCC_P9_SRIO2_RXN

AMCC_P11_SRIO4_TXP

AMCC_P11_SRIO4_TXN

AMCC_P9_SRIO2_TXP

AMCC_P9_SRIO2_TXN

(12)

(12)

AMCC_P9_SRIO2_RXP

AMCC_P9_SRIO2_RXN

(12)

(12)

AMCC_P8_SRIO1_TXP

AMCC_P8_SRIO1_TXN

(12)

(12)

AMCC_P8_SRIO1_RXP

AMCC_P8_SRIO1_RXN

(12)

(12)

R180

10K

R964

10K

1

2

3

(16,29) 4

GND

VREF1

SCL1

SDA1

EN

VREF2

SCL2

SDA2

8

7

6

5

C411

0.1uF

16V

C

DSP_SCL_AMC

DSP_SDA_AMC

TI_PCA9306DCUT

R90

2K

1%

R175

2K

1%

VCC3V3_AUX

VCC1V8_AUX

C128

0.1uF

16V

R958

C160

0.1uF

16V

AMCC_P13_TDM1_TX3

AMCC_P13_TDM1_TX1

U245

DSP_SCL

DSP_SDA

IN

BI

4.7K

2

AMC0_SGMII0_TX_DP

AMC0_SGMII0_TX_DN

19

(12)

(12)

MMC_GA0

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

VCCA

IN

GND_56

TDI

TDO

TRST

TMS

TCK

GND_55

Tx20+

Tx20GND_54

Rx20+

Rx20GND_53

Tx19+

Tx19GND_52

Rx19+

Rx19GND_51

Tx18+

Tx18GND_50

Rx18+

Rx18GND_49

Tx17+

Tx17GND_48

Rx17+

Rx17GND_47

TCLKD+

TCLKDGND_46

TCLKC+

TCLKCGND_45

Tx15+

Tx15GND_44

Rx15+

Rx15GND_43

Tx14+

Tx14GND_42

Rx14+

Rx14GND_41

Tx13+

Tx13GND_40

Rx13+

Rx13GND_39

Tx12+

Tx12GND_38

Rx12+

Rx12GND_37

Tx11+

Tx11GND_36

Rx11+

Rx11GND_35

Tx10+

Tx10GND_34

Rx10+

Rx10GND_33

Tx9+

Tx9GND_32

Rx9+

Rx9GND_31

Tx8+

Tx8GND_30

Rx8+

Rx8GND_29

VCCB

MMC_GA0

Management Power

GND_1

PWR_12V_1

PS1

MP

GA0

RSRVD6

GND_2

RSRVD8

PWR_12V_2

GND_3

Tx0+

Tx0GND_4

Rx0+

Rx0GND_5

GA1

PWR_12V_3

GND_6

Tx1+

Tx1GND_7

Rx1+

Rx1GND_8

GA2

PWR_12V_4

GND_9

Tx2+

Tx2GND_10

Rx2+

Rx2GND_11

Tx3+

Tx3GND_12

Rx3+

Rx3GND_13

ENABLE

PWR_12V_5

GND_14

Tx4+

Tx4GND_15

Rx4+

Rx4GND_16

Tx5+

Tx5GND_17

Rx5+

Rx5GND_18

SCL_L

PWR_12V_6

GND_19

Tx6+

Tx6GND_20

Rx6+

Rx6GND_21

Tx7+

Tx7GND_22

Rx7+

Rx7GND_23

SDA_L

PWR_12V_7

GND_24

TCLKA+

TCLKAGND_25

TCLKB+

TCLKBGND_26

FCLKA+

FCLKAGND_27

PS0

PWR_12V_8

GND_28

GND

VCC3V3_MP_AMC

(11)

11

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

MMC_PS_N1

VCC1V8

TSIP1_TX3_R

TSIP1_TX1_R

OE

A1

A2

A3

A4

A5

A6

A7

A8

10

1

3

4

5

6

7

8

9

TSIP1_TX2_R

TSIP1_TX0_R

TSIP0_TX3_R

TSIP0_TX1_R

TSIP0_TX2_R

TSIP0_TX0_R

U13

TI_TXS0108EPWR

R124

R150

R151

R152

R122

R148

R149

R123

R119

R146

R147

R120

R105

R144

R145

R106

22

0

0

22

22

0

0

22

22

0

0

22

22

0

0

22

TSIP1_TX3

TSIP1_RX1

TSIP1_RX3

TSIP1_TX1

TSIP1_TX2

TSIP1_RX0

TSIP1_RX2

TSIP1_TX0

TSIP0_TX3

TSIP0_RX1

TSIP0_RX3

TSIP0_TX1

TSIP0_TX2

TSIP0_RX0

TSIP0_RX2

TSIP0_TX0

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

TSIP1_TX3

TSIP1_RX1

TSIP1_RX3

TSIP1_TX1

TSIP1_TX2

TSIP1_RX0

TSIP1_RX2

TSIP1_TX0

TSIP0_TX3

TSIP0_RX1

TSIP0_RX3

TSIP0_TX1

TSIP0_TX2

TSIP0_RX0

TSIP0_RX2

TSIP0_TX0

B

GF-AMC-B

A

A

Designed for TI by ADVANTECH

Title

AMC GF

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

10

of

40

5

4

3

2

1

Power for MSP430

VCC3V3_MP

D

D10

2

RB751V40

1

200mA

VCC3V3_MP_AMC

D9

2

RB751V40

1

200mA

VCC3V3_AUX

D

C524

0.1uF

16V

VCC3V3_MP

MMC JTAG

MMC_TEST

MMC_TDO

MMC_TDI

MMC_TMS

MMC_TCK

C598

2200pF

50V

MMC1

C

1

Y1

2 32.768KHz_12.5pF

4

3

C8

22pF

50V

VCC3V3_MP

MMC_XTAL2

C6

0.1uF

16V

B1

120_100MHz

0.5A

MMC_XTAL1

MMC_XTAL2

VCC3V3_MP

(10)

(10)

(10)

MMC_GA0

MMC_GA1

MMC_GA2

OUT

OUT

OUT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

P6.4/A4

P6.5/A5

P6.6/A6

P6.7/A7

P7.4/A12

P7.5/A13

P7.6/A14

P7.7/A15

P5.0/A8/VREF+/VeREF+

P5.1/A9/VREF-/VeREFAVCC

AVSS

P7.0/XIN

P7.1/XOUT

DVSS1

DVCC1

P1.0/TA0CLK/ACLK

P1.1/TA0.0

P1.2/TA0.1

P1.3/TA0.2

TI_MSP430F5435IPN

P1.4/TA0.3

P1.5/TA0.4

P1.6/SMCLK

P1.7

P2.0/TA1CLK/MCLK

P2.1/TA1.0

P2.2/TA1.1

P2.3/TA1.2

P2.4/RTCCLK

DVSS3

DVCC3

P2.5

P2.6/ACLK

P2.7/ADC12CLK/DMAE0

P3.0/UCB0STE/UCA0CLK

P3.1/UCB0SIMO/UCB0SDA

P3.2/UCB0SOMI/UCB0SCL

P3.3/UCB0CLK/UCA0STE

P3.4/UCA0TXD/UCA0SIMO

P3.5/UCA0RXD/UCA0SOMI

MMC_XTAL1

22pF

50V

(RED LED)

VCC3V3_MP

R3

330

R4

330

1

D1

R

2

MMC_LED1

KP-1608EC

B

2

MMC_LED2

19-215SUBC/S280/TR8

1

D2

C2

0.1uF

16V

C3

0.1uF

16V

C4

0.1uF

16V

MMC_RST_N

PH_7x2V_2.54mm

C5

C1

0.1uF

16V

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

VCC3V3_MP

TAP_MMC1

1

3

5

7

9

11

13

P6.3/A3

P6.2/A2

P6.1/A1

P6.0/A0

RST/NMI/SBWTDIO

PJ.3/TCK

PJ.2/TMS

PJ.1/TDI/TCLK

PJ.0/TDO

TEST/SBWTCLK

P5.3/XT2OUT

P5.2/XT2IN

DVSS4

DVCC4

P8.6/TA1.1

P8.5/TA1.0

P8.4/TA0.4

P8.3/TA0.3

P8.2/TA0.2

P8.1/TA0.1

2

4

6

8

10

12

14

VCC3V3_MP

MMC_TEST

MMC_TDO

MMC_TDI

MMC_TMS

MMC_TCK

MMC_RST_N

(BLUE LED)

C

P8.0/TA0.0

P7.3/TA1.2

P7.2/TB0OUTH/SVMOUT

P5.7/UCA1RXD/UCA1SOMI

P5.6/UCA1TXD/UCA1SIMO

P5.5/UCB1CLK/UCA1STE

P5.4/UCB1SOMI/UCB1SCL

P4.7/TB0CLK/SMCLK

P4.6/TB0.6

DVCC2

DVSS2

VCORE

P4.5/TB0.5

P4.4/TB0.4

P4.3/TB0.3

P4.2/TB0.2

P4.1/TB0.1

P4.0/TB0.0

P3.7/UCB1SIMO/UCB1SDA

P3.6/UCB1STE/UCA1CLK

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

R960

R961

R962

NL/0

NL/0

NL/0

C7

0.47uF

10V

OUT

IN

IN

(31)

(31)

(31)

MMC_SPI_MISO

MMC_SPI_MOSI

MMC_SPI_STE

VCC3V3_MP

MMC_SCK

R17

NL/0 MMC_HANDLE

R963

NL/0

IN

(31)

MMC_SPI_SCK

The NU resistors on these connections to the MSP430 are for debug use only

and will be used only with the shunts removed from pins 1 and 2 of CN7

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

B

R7

R6

MMC_GAPU

MMC_LED1

SPI I/F is for Advantech FPGA debugging.

MMC_MISO

MMC_MOSI

MMC_STE

TP7

NL/0

NL/0

IN

BI

MMC_LED2

OUT

IN

UART_FT_RX

UART_FT_TX

SMB_SCL_IPMBL

SMB_SDA_IPMBL

(10)

(10)

(16,26)

(16,26)

B

VCC3V3_MP

SMB_SCL_IPMBL

R2

33K

SMB_SDA_IPMBL

R1

33K

TP8

TP9

OUT

MMC_DETECT#

(30)

IN

IN

OUT

OUT

MMC_RESETSTAT#

MMC_BOOTCOMPLETE

MMC_POR_IN_AMC#

MMC_WR_AMC#

(30)

(30)

(30)

(30)

VCC3V3_MP

VCC3V3_MP

VCC3V3_MP

R10

8.2K

5%

SW2-P1

C

D

A

H2

H1

R12

100

1%

MMC_HANDLE

C10

0.01uF

16V

R11

NL/10K

1%

R14

3.3K

5%

R15

3.3K

5%

MMC_GA0

3

MMC_RST_N

R13

3.3K

5%

Q1

2N7002

300mA/60v

D

A

G

1

MMC_ENABLE_N

S

MMC_GA1

MMC_GA2

A

B

SW2

NL/MPU-101-127

MMC_GAPU

IN

MMC_ENABLE_N

(10)

2

R9

8.2K

5%

R16

10K

1%

R18

NL/0

R19

NL/0

Designed for TI by ADVANTECH

R20

NL/0

Title

MMC

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

11

of

40

5

4

3

2

1

SRIO

Caution!

DSP1P

(10)

(10)

AMCC_P8_SRIO1_RXP

AMCC_P8_SRIO1_RXN

IN

IN

(10)

(10)

AMCC_P9_SRIO2_RXP

AMCC_P9_SRIO2_RXN

IN

IN

(10)

(10)

AMCC_P10_SRIO3_RXP

AMCC_P10_SRIO3_RXN

IN

IN

(10)

(10)

AMCC_P11_SRIO4_RXP

AMCC_P11_SRIO4_RXN

IN

IN

D

AMCC_P8_SRIO1_RXP

AMCC_P8_SRIO1_RXN

C164

C167

0.1uF 16V

0.1uF 16V

AMCC_P8_SRIO1_RXP_C

AMCC_P8_SRIO1_RXN_C

AJ12

AJ11

AMCC_P9_SRIO2_RXP

AMCC_P9_SRIO2_RXN

C165

C166

0.1uF 16V

0.1uF 16V

AMCC_P9_SRIO2_RXP_C

AMCC_P9_SRIO2_RXN_C

AH11

AH10

AMCC_P10_SRIO3_RXP

AMCC_P10_SRIO3_RXN

C168

C169

0.1uF 16V

0.1uF 16V

AMCC_P10_SRIO3_RXP_C

AMCC_P10_SRIO3_RXN_C

AH13

AH14

AMCC_P11_SRIO4_RXP

AMCC_P11_SRIO4_RXN

C170

C171

0.1uF 16V

0.1uF 16V

AMCC_P11_SRIO4_RXP_C

AMCC_P11_SRIO4_RXN_C

AJ14

AJ15

RIORXP0

RIORXN0

SERIAL RAPIDIO

SERDES

RIOTXP0

RIOTXN0

RIORXP1

RIORXN1

RIOTXP1

RIOTXN1

RIORXP2

RIORXN2

RIOTXP2

RIOTXN2

RIORXP3

RIORXN3

RIOTXP3

RIOTXN3

pinout_rev0_3_2_customer

AF11

AF10

AMCC_P8_SRIO1_TXP

AMCC_P8_SRIO1_TXN

AG12

AG11

AMCC_P9_SRIO2_TXP

AMCC_P9_SRIO2_TXN

AG14

AG15

AMCC_P10_SRIO3_TXP

AMCC_P10_SRIO3_TXN

AF13

AF14

AMCC_P11_SRIO4_TXP

AMCC_P11_SRIO4_TXN

OUT

OUT

AMCC_P8_SRIO1_TXP

AMCC_P8_SRIO1_TXN

(10)

(10)

OUT

OUT

AMCC_P9_SRIO2_TXP

AMCC_P9_SRIO2_TXN

(10)

(10)

OUT

OUT

AMCC_P10_SRIO3_TXP

AMCC_P10_SRIO3_TXN

(10)

(10)

OUT

OUT

AMCC_P11_SRIO4_TXP

AMCC_P11_SRIO4_TXN

(10)

(10)

"Place ALL SERDES DC-blocking

caps on top layer adjacent to the

DSP’s RX pins so that there are

no additional vias"

D

TI_TMS320C6678

SGMII

VCC1V8

VCC3V3_AUX

C327

0.1uF

16V

DSP1O

(10)

(10)

AMC0_SGMII0_RX_DP

AMC0_SGMII0_RX_DN

IN

IN

(27)

(27)

DSP_SGMII_RXP

DSP_SGMII_RXN

IN

IN

AMC0_SGMII0_RX_DP

AMC0_SGMII0_RX_DN

C172

C173

0.1uF 16V

0.1uF 16V

AMC0_SGMII0_RX_DP_C

AMC0_SGMII0_RX_DN_C

AJ17

AJ18

DSP_SGMII_RXP

DSP_SGMII_RXN

C465

C468

0.1uF 16V

0.1uF 16V

DSP_SGMII_RXP_C

DSP_SGMII_RXN_C

AH16

AH17

SGMII0RXP

SGMII0RXN

SGMII SERDES

SGMII1RXP

SGMII1RXN

SGMII0TXP

SGMII0TXN

SGMII1TXP

SGMII1TXN

AG17 AMC0_SGMII0_TX_DP

AG18 AMC0_SGMII0_TX_DN

AF16 DSP_SGMII_TXP

AF17 DSP_SGMII_TXN

OUT

OUT

AMC0_SGMII0_TX_DP

AMC0_SGMII0_TX_DN

(10)

(10)

OUT

OUT

DSP_SGMII_TXP

DSP_SGMII_TXN

(27)

(27)

R316

100K

1%

U244

DSP_MDC

DSP_MDIO

MDIO

pinout_rev0_3_2_customer

MDIO

MDCLK

G26 DSP_MDIO

H26 DSP_MDC

VCC1V8

TI_TMS320C6678

R85

10K

R957

10K

1

2

3

4

GND

VREF1

SCL1

SDA1

EN

VREF2

SCL2

SDA2

8

7

6

5

C401

0.1uF

16V

DSP_MDC_1

DSP_MDIO_1

DSP_MDC_1

DSP_MDIO_1

OUT

BI

TI_PCA9306DCUT

R82

2K

1%

R83

2K

1%

(27)

(27)

VCC2V5

C

C

PCIE

DSP1Q

AMCC_P4_PCIe_RX1P

AMCC_P4_PCIe_RX1N

IN

IN

AMCC_P4_PCIe_RX1P (10)

AMCC_P4_PCIe_RX1N (10)

C305

C306

0.1uF 16V

0.1uF 16V

AMCC_P4_PCIe_RX1P_C

AMCC_P4_PCIe_RX1N_C

AH8

AH7

AMCC_P5_PCIe_RX2P

AMCC_P5_PCIe_RX2N

IN

IN

AMCC_P5_PCIe_RX2P (10)

AMCC_P5_PCIe_RX2N (10)

C307

C308

0.1uF 16V

0.1uF 16V

AMCC_P5_PCIe_RX2P_C

AMCC_P5_PCIe_RX2N_C

AJ8

AJ9

PCIERXP0

PCIERXN0

PCIETXP0

PCIETXN0

PCIe SERDES

PCIERXP1

PCIERXN1

PCIETXP1

PCIETXN1

AF7 AMCC_P4_PCIe_TX1P

AF8 AMCC_P4_PCIe_TX1N

AG8 AMCC_P5_PCIe_TX2P

AG9 AMCC_P5_PCIe_TX2N

OUT

OUT

AMCC_P4_PCIe_TX1P

AMCC_P4_PCIe_TX1N

(10)

(10)

OUT

OUT

AMCC_P5_PCIe_TX2P

AMCC_P5_PCIe_TX2N

(10)

(10)

pinout_rev0_3_2_customer

TI_TMS320C6678

B

B

HyperLink

DSP1R

(29)

(29)

HyperLink_RXP0

HyperLink_RXN0

IN

IN

(29)

(29)

HyperLink_RXP1

HyperLink_RXN1

IN

IN

(29)

(29)

HyperLink_RXP2

HyperLink_RXN2

IN

IN

(29)

(29)

HyperLink_RXP3

HyperLink_RXN3

IN

IN

HyperLink_RXP0

HyperLink_RXN0

C505

C470

0.1uF 16V

0.1uF 16V

HyperLink_RXP0_C

HyperLink_RXN0_C

T2

U2

HyperLink_RXP1

HyperLink_RXN1

C512

C511

0.1uF 16V

0.1uF 16V

HyperLink_RXP1_C

HyperLink_RXN1_C

R1

T1

HyperLink_RXP2

HyperLink_RXN2

C14

C12

0.1uF 16V

0.1uF 16V

HyperLink_RXP2_C

HyperLink_RXN2_C

N1

M1

HyperLink_RXP3

HyperLink_RXN3

C20

C19

0.1uF 16V

0.1uF 16V

HyperLink_RXP3_C

HyperLink_RXN3_C

N2

P2

MCMRXP0

MCMRXN0

MCMTXP0

MCMTXN0

VUSR

SERDES

MCMRXP1

MCMRXN1

MCMTXP1

MCMTXN1

MCMRXP2

MCMRXN2

MCMTXP2

MCMTXN2

MCMRXP3

MCMRXN3

MCMTXP3

MCMTXN3

MCMREFCLKOUTP

MCMREFCLKOUTN

N5

M5

U4

T4

T5

R5

P4

N4

Y1

W1

OUT

OUT

HyperLink_TXP0

HyperLink_TXN0

(29)

(29)

OUT

OUT

HyperLink_TXP1

HyperLink_TXN1

(29)

(29)

OUT

OUT

HyperLink_TXP2

HyperLink_TXN2

(29)

(29)

OUT

OUT

HyperLink_TXP3

HyperLink_TXN3

(29)

(29)

HyperLink_REFCLKOUTP

HyperLink_REFCLKOUTN

“The HyperLink routes must

have a maximum of 2 vias and

no via stubs – top layer routing

recommended”

TP5

TP6

A

A

(29)

(29)

(29)

(29)

HyperLink_RXFLCLK

HyperLink_RXFLDAT

HyperLink_RXPMCLK

HyperLink_RXPMDAT

W3

W4

Y3

Y4

OUT

OUT

IN

IN

MCMRXFLCLK

MCMRXFLDAT

MCMRXPMCLK

MCMRXPMDAT

VUSR

SMBUS

MCMTXFLCLK

MCMTXFLDAT

MCMTXPMCLK

MCMTXPMDAT

AA1

AA3

AA2

AA4

IN

IN

OUT

OUT

HyperLink_TXFLCLK

HyperLink_TXFLDAT

HyperLink_TXPMCLK

HyperLink_TXPMDAT

(29)

(29)

(29)

(29)

pinout_rev0_3_2_customer

TI_TMS320C6678

Designed for TI by ADVANTECH

Title

DSP_SERDES_PORTS

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

12

of

40

5

4

3

DSP1K

D

(24,25)

(24,25)

DSP0_DDR3_ECKP_0

DSP0_DDR3_ECKN_0

OUT

OUT

(24,25)

DSP0_DDR3_ECKE_0

OUT

(24,25)

DSP0_DDR3_ECS_0#

OUT

(24,25)

(24,25)

(24,25)

DSP0_DDR3_ECAS#

DSP0_DDR3_ERAS#

DSP0_DDR3_EWE#

(24,25)

(24,25)

(24,25)

C

OUT

OUT

OUT

DSP0_DDR3_EBA_0

DSP0_DDR3_EBA_1

DSP0_DDR3_EBA_2

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(25)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(24)

(25)

(25)

OUT

OUT

OUT

DSP0_DDR3_EDM_0

DSP0_DDR3_EDM_1

DSP0_DDR3_EDM_2

DSP0_DDR3_EDM_3

DSP0_DDR3_EDM_4

DSP0_DDR3_EDM_5

DSP0_DDR3_EDM_6

DSP0_DDR3_EDM_7

DSP0_DDR3_EDM_8

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

DSP0_DDR3_EDQSP_0

DSP0_DDR3_EDQSN_0

DSP0_DDR3_EDQSP_1

DSP0_DDR3_EDQSN_1

DSP0_DDR3_EDQSP_2

DSP0_DDR3_EDQSN_2

DSP0_DDR3_EDQSP_3

DSP0_DDR3_EDQSN_3

DSP0_DDR3_EDQSP_4

DSP0_DDR3_EDQSN_4

DSP0_DDR3_EDQSP_5

DSP0_DDR3_EDQSN_5

DSP0_DDR3_EDQSP_6

DSP0_DDR3_EDQSN_6

DSP0_DDR3_EDQSP_7

DSP0_DDR3_EDQSN_7

DSP0_DDR3_EDQSP_8

DSP0_DDR3_EDQSN_8

(25) DSP0_DDR3_ECC[0..7]

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

(24,25)DSP0_DDR3_EMRESETN

OUT

(24,25)

OUT

DSP0_DDR3_EODT_0

DSP0_DDR3_ECKP_0

DSP0_DDR3_ECKN_0

A12

B12

A16

B16

DSP0_DDR3_ECKE_0

D11

E18

C11

C12

DSP0_DDR3_ECS_0#

DSP0_DDR3_ECAS#

DSP0_DDR3_ERAS#

DSP0_DDR3_EWE#

D12

C10

E12

DSP0_DDR3_EBA_0

DSP0_DDR3_EBA_1

DSP0_DDR3_EBA_2

A13

B13

C13

DSP0_DDR3_EDM_0

DSP0_DDR3_EDM_1

DSP0_DDR3_EDM_2

DSP0_DDR3_EDM_3

DSP0_DDR3_EDM_4

DSP0_DDR3_EDM_5

DSP0_DDR3_EDM_6

DSP0_DDR3_EDM_7

DSP0_DDR3_EDM_8

E29

C27

A25

A22

A10

A8

B5

B2

A20

DSP0_DDR3_EDQSP_0

DSP0_DDR3_EDQSN_0

DSP0_DDR3_EDQSP_1

DSP0_DDR3_EDQSN_1

DSP0_DDR3_EDQSP_2

DSP0_DDR3_EDQSN_2

DSP0_DDR3_EDQSP_3

DSP0_DDR3_EDQSN_3

DSP0_DDR3_EDQSP_4

DSP0_DDR3_EDQSN_4

DSP0_DDR3_EDQSP_5

DSP0_DDR3_EDQSN_5

DSP0_DDR3_EDQSP_6

DSP0_DDR3_EDQSN_6

DSP0_DDR3_EDQSP_7

DSP0_DDR3_EDQSN_7

DSP0_DDR3_EDQSP_8

DSP0_DDR3_EDQSN_8

C28

C29

A27

B27

A24

B24

A21

B21

A9

B9

B6

A6

B3

A3

D1

C1

A19

B19

DSP0_DDR3_ECC0

DSP0_DDR3_ECC1

DSP0_DDR3_ECC2

DSP0_DDR3_ECC3

DSP0_DDR3_ECC4

DSP0_DDR3_ECC5

DSP0_DDR3_ECC6

DSP0_DDR3_ECC7

E19

C20

D19

B20

C19

C18

B18

A18

DSP0_DDR3_EMRESETN

E11

DSP0_DDR3_EODT_0

D13

E13

U1_DDRSLRATE0

U1_DDRSLRATE1

G27

H27

DSP_VREFSSTL

E14

G22

C114

0.1uF

16V

DDRCKE0

DDRCKE1

DDRCE0z

DDRCE1z

DDR3

CONTROLLER

DDRCASz

DDRRASz

DDRWEz

DDRBA0

DDRBA1

DDRBA2

DDRDQM0

DDRDQM1

DDRDQM2

DDRDQM3

DDRDQM4

DDRDQM5

DDRDQM6

DDRDQM7

DDRDQM8

DDRDQS0P

DDRDQS0N

DDRDQS1P

DDRDQS1N

DDRDQS2P

DDRDQS2N

DDRDQS3P

DDRDQS3N

DDRDQS4P

DDRDQS4N

DDRDQS5P

DDRDQS5N

DDRDQS6P

DDRDQS6N

DDRDQS7P

DDRDQS7N

DDRDQS8P

DDRDQS8N

DDRCB00

DDRCB01

DDRCB02

DDRCB03

DDRCB04

DDRCB05

DDRCB06

DDRCB07

DDRRESETz

DDRODT0

DDRODT1

DDRSLRATE0

DDRSLRATE1

VREFSSTL

PTV15

R58

45.3

1%

DDR3 Drive Stength:

70-ohm: 6mA

60-ohm: 7mA

50-ohm: 8mA

45-ohm: 9mA

40-ohm: 10mA

36-ohm: 11mA

B

DDRCLKOUTP0

DDRCLKOUTN0

DDRCLKOUTP1

DDRCLKOUTN1

pinout_rev0_3_2_customer

DSP0_DDR3_EA0

DSP0_DDR3_EA1

DSP0_DDR3_EA2

DSP0_DDR3_EA3

DSP0_DDR3_EA4

DSP0_DDR3_EA5

DSP0_DDR3_EA6

DSP0_DDR3_EA7

DSP0_DDR3_EA8

DSP0_DDR3_EA9

DSP0_DDR3_EA10

DSP0_DDR3_EA11

DSP0_DDR3_EA12

DSP0_DDR3_EA13

DSP0_DDR3_EA14

DSP0_DDR3_EA15

E28

D29

E27

D28

D27

B28

E26

F25

F24

E24

E25

D25

D26

C26

B26

A26

F23

F22

D24

E23

A23

B23

C24

E22

D21

F20

E21

F21

D22

C21

B22

C22

E10

D10

B10

D9

E9

C9

B8

E8

A7

D7

E7

C7

B7

E6

D6

C6

C5

A5

B4

A4

D4

E4

C4

C3

F4

D2

E2

C2

F2

F3

E1

F1

DSP0_DDR3_EDQ0

DSP0_DDR3_EDQ1

DSP0_DDR3_EDQ2

DSP0_DDR3_EDQ3

DSP0_DDR3_EDQ4

DSP0_DDR3_EDQ5

DSP0_DDR3_EDQ6

DSP0_DDR3_EDQ7

DSP0_DDR3_EDQ8

DSP0_DDR3_EDQ9

DSP0_DDR3_EDQ10

DSP0_DDR3_EDQ11

DSP0_DDR3_EDQ12

DSP0_DDR3_EDQ13

DSP0_DDR3_EDQ14

DSP0_DDR3_EDQ15

DSP0_DDR3_EDQ16

DSP0_DDR3_EDQ17

DSP0_DDR3_EDQ18

DSP0_DDR3_EDQ19

DSP0_DDR3_EDQ20

DSP0_DDR3_EDQ21

DSP0_DDR3_EDQ22

DSP0_DDR3_EDQ23

DSP0_DDR3_EDQ24

DSP0_DDR3_EDQ25

DSP0_DDR3_EDQ26

DSP0_DDR3_EDQ27

DSP0_DDR3_EDQ28

DSP0_DDR3_EDQ29

DSP0_DDR3_EDQ30

DSP0_DDR3_EDQ31

DSP0_DDR3_EDQ32

DSP0_DDR3_EDQ33

DSP0_DDR3_EDQ34

DSP0_DDR3_EDQ35

DSP0_DDR3_EDQ36

DSP0_DDR3_EDQ37

DSP0_DDR3_EDQ38

DSP0_DDR3_EDQ39

DSP0_DDR3_EDQ40

DSP0_DDR3_EDQ41

DSP0_DDR3_EDQ42

DSP0_DDR3_EDQ43

DSP0_DDR3_EDQ44

DSP0_DDR3_EDQ45

DSP0_DDR3_EDQ46

DSP0_DDR3_EDQ47

DSP0_DDR3_EDQ48

DSP0_DDR3_EDQ49

DSP0_DDR3_EDQ50

DSP0_DDR3_EDQ51

DSP0_DDR3_EDQ52

DSP0_DDR3_EDQ53

DSP0_DDR3_EDQ54

DSP0_DDR3_EDQ55

DSP0_DDR3_EDQ56

DSP0_DDR3_EDQ57

DSP0_DDR3_EDQ58

DSP0_DDR3_EDQ59

DSP0_DDR3_EDQ60

DSP0_DDR3_EDQ61

DSP0_DDR3_EDQ62

DSP0_DDR3_EDQ63

VCC1V5

R77

1K

1%

DSP_VREFSSTL

C59

0.1uF

16V

DDRD00

DDRD01

DDRD02

DDRD03

DDRD04

DDRD05

DDRD06

DDRD07

DDRD08

DDRD09

DDRD10

DDRD11

DDRD12

DDRD13

DDRD14

DDRD15

DDRD16

DDRD17

DDRD18

DDRD19

DDRD20

DDRD21

DDRD22

DDRD23

DDRD24

DDRD25

DDRD26

DDRD27

DDRD28

DDRD29

DDRD30

DDRD31

DDRD32

DDRD33

DDRD34

DDRD35

DDRD36

DDRD37

DDRD38

DDRD39

DDRD40

DDRD41

DDRD42

DDRD43

DDRD44

DDRD45

DDRD46

DDRD47

DDRD48

DDRD49

DDRD50

DDRD51

DDRD52

DDRD53

DDRD54

DDRD55

DDRD56

DDRD57

DDRD58

DDRD59

DDRD60

DDRD61

DDRD62

DDRD63

A14

B14

F14

F13

A15

C15

B15

D15

F15

E15

E16

D16

E17

C16

D17

C17

OUT

DSP0_DDR3_EA[0..15]

D

BI

DSP0_DDR3_EDQ[0..7]

BI

DSP0_DDR3_EDQ[8..15]

BI

DSP0_DDR3_EDQ[16..23]

BI

DSP0_DDR3_EDQ[24..31]

BI

DSP0_DDR3_EDQ[32..39]

DSP_VREFSSTL

(24,25)

(24)

(24)

(24)

(24)

DSP0_DDR3_EDQ[40..47]

(24)

BI

DSP0_DDR3_EDQ[48..55]

(24)

BI

DSP0_DDR3_EDQ[56..63]

(24)

R37

39.2

1%

DSP0_DDR3_ECKN_0

R38

39.2

1%

C31

0.1uF

16V

VCC1V5

VCC0V75

DSP0_DDR3_EA0

R41

39.2

1%

C33

0.01uF 16V

DSP0_DDR3_EA1

R42

39.2

1%

C34

0.1uF 16V

DSP0_DDR3_EA2

R43

39.2

1%

C35

0.01uF 16V

DSP0_DDR3_EA3

R44

39.2

1%

C36

0.1uF 16V

DSP0_DDR3_EA4

R45

39.2

1%

C37

0.01uF 16V

DSP0_DDR3_EA5

R46

39.2

1%

C38

0.1uF 16V

DSP0_DDR3_EA6

R47

39.2

1%

DSP0_DDR3_EA7

R48

39.2

1%

DSP0_DDR3_EA8

R49

39.2

1%

DSP0_DDR3_EA9

R50

39.2

1%

DSP0_DDR3_EA10

R51

39.2

1%

DSP0_DDR3_EA11

R52

39.2

1%

DSP0_DDR3_EA12

R53

39.2

1%

DSP0_DDR3_EA13

R54

39.2

1%

DSP0_DDR3_EA14

R55

39.2

1%

DSP0_DDR3_EA15

R86

39.2

1%

C

Place these resistors at the

end of the trace.

VCC0V75

DSP0_DDR3_EBA_0

R56

39.2

1%

C39

0.01uF 16V

DSP0_DDR3_EBA_1

R57

39.2

1%

C40

0.1uF 16V

DSP0_DDR3_EBA_2

R59

39.2

1%

C41

0.01uF 16V

DSP0_DDR3_EODT_0

R60

39.2

1%

C42

0.1uF 16V

DSP0_DDR3_EWE#

R61

39.2

1%

C43

0.01uF 16V

DSP0_DDR3_ERAS#

R62

39.2

1%

C44

0.1uF 16V

DSP0_DDR3_ECAS#

R63

39.2

1%

DSP0_DDR3_ECKE_0

R64

39.2

1%

DSP0_DDR3_ECS_0#

R65

39.2

1%

DSP0_DDR3_EMRESETN

R66

39.2

1%

B

VCC1V5

R70

10K

1%

U1_DDRSLRATE0

R78

1K

1%

DSP0_DDR3_ECKP_0

(24)

BI

R69

NL/10K

1%

OUT

1

(24,25)

TI_TMS320C6678

VCC1V5

C60

0.1uF

16V

DDRA00

DDRA01

DDRA02

DDRA03

DDRA04

DDRA05

DDRA06

DDRA07

DDRA08

DDRA09

DDRA10

DDRA11

DDRA12

DDRA13

DDRA14

DDRA15

2

U1_DDRSLRATE1

R71

10K

1%

R72

NL/10K

1%

A

A

Trace need 20 mil.

DDR3 Slew-Rate Setting (DDRSLRATE[1:0]):

00

10

01

11

Fastest

Fast

Slow

Slowest

Designed for TI by ADVANTECH

Title

DSP_DDR3

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

13

of

40

5

4

3

2

1

D

D

NAND1

DSP1N

DSP_EMIFD0

DSP_EMIFD1

DSP_EMIFD2

DSP_EMIFD3

DSP_EMIFD4

DSP_EMIFD5

DSP_EMIFD6

DSP_EMIFD7

DSP_EMIFD8

DSP_EMIFD9

DSP_EMIFD10

DSP_EMIFD11

DSP_EMIFD12

DSP_EMIFD13

DSP_EMIFD14

DSP_EMIFD15

C

(29)

DSP_EMIFWAIT1

VCC1V8

DSP_EMIFD0

DSP_EMIFD1

DSP_EMIFD2

DSP_EMIFD3

DSP_EMIFD4

DSP_EMIFD5

DSP_EMIFD6

DSP_EMIFD7

DSP_EMIFD8

DSP_EMIFD9

DSP_EMIFD10

DSP_EMIFD11

DSP_EMIFD12

DSP_EMIFD13

DSP_EMIFD14

DSP_EMIFD15

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

DSP_EMIFWAIT0

DSP_EMIFWAIT1

IN

R183

Y27

(29)

AB29

(29)

AA29

(29)

Y26

(29)

AA27

(29)

AB27

(29)

AA26

(29)

AA25

(29)

Y25

(29)

AB25

(29)

AA24

(29)

Y24

(29)

AB23

(29)

AB24

(29)

AB26

(29)

AC25

(29)

T29

T28

EMIFD00

EMIFD01

EMIFD02

EMIFD03

EMIFD04

EMIFD05

EMIFD06

EMIFD07

EMIFD08

EMIFD09

EMIFD10

EMIFD11

EMIFD12

EMIFD13

EMIFD14

EMIFD15

EMIFWAIT0

EMIFWAIT1

EMIFA00

EMIFA01

EMIFA02

EMIFA03

EMIFA04

EMIFA05

EMIFA06

EMIFA07

EMIFA08

EMIFA09

EMIFA10

EMIFA11

EMIFA12

EMIFA13

EMIFA14

EMIFA15

EMIFA16

EMIFA17

EMIFA18

EMIFA19

EMIFA20

EMIFA21

EMIFA22

EMIFA23

T27

T24

U29

T25

U27

U28

U25

U24

V28

V29

V27

V26

V25

V24

W28

W27

W29

W26

W25

W24

W23

Y29

Y28

U23

DSP_EMIFA00

DSP_EMIFA01

DSP_EMIFA02

DSP_EMIFA03

DSP_EMIFA04

DSP_EMIFA05

DSP_EMIFA06

DSP_EMIFA07

DSP_EMIFA08

DSP_EMIFA09

DSP_EMIFA10

DSP_EMIFA11

DSP_EMIFA12

DSP_EMIFA13

DSP_EMIFA14

DSP_EMIFA15

DSP_EMIFA16

DSP_EMIFA17

DSP_EMIFA18

DSP_EMIFA19

DSP_EMIFA20

DSP_EMIFA21

DSP_EMIFA22

DSP_EMIFA23

P25

R27

R28

R25

R236

R248

R249

R24

R23

DSP_EMIFBE0Z

DSP_EMIFBE1Z

P24

R26

DSP_EMIFWEZ

DSP_EMIFOEZ

P26

DSP_EMIFRNW

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

DSP_EMIFA00

DSP_EMIFA01

DSP_EMIFA02

DSP_EMIFA03

DSP_EMIFA04

DSP_EMIFA05

DSP_EMIFA06

DSP_EMIFA07

DSP_EMIFA08

DSP_EMIFA09

DSP_EMIFA10

DSP_EMIFA11

DSP_EMIFA12

DSP_EMIFA13

DSP_EMIFA14

DSP_EMIFA15

DSP_EMIFA16

DSP_EMIFA17

DSP_EMIFA18

DSP_EMIFA19

DSP_EMIFA20

DSP_EMIFA21

DSP_EMIFA22

DSP_EMIFA23

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(29)

(30)

EMIFCE0z

EMIFCE1z

EMIFCE2z

EMIFCE3z

EMIFBE0z

EMIFBE1z

EMIF16

pinout_rev0_3_2_customer

EMIFWEz

EMIFOEz

EMIFRnW

DSP_EMIFCE0Z

DSP_EMIFCE1Z

DSP_EMIFCE2Z

OUT

OUT

DSP_EMIFCE1Z

DSP_EMIFCE2Z

OUT

OUT

DSP_EMIFBE0Z

DSP_EMIFBE1Z

(29)

(29)

OUT

OUT

DSP_EMIFWEZ

DSP_EMIFOEZ

(29)

(29)

OUT

DSP_EMIFRNW

(29)

H4

J4

K4

K5

K6

J7

K7

J8

DSP_EMIFWEZ

C7

C3

DSP_EMIFOEZ

DSP_EMIFWAIT0

D4

C8

DSP_EMIFCE0Z

DSP_EMIFA12

C6

D5

DSP_EMIFA11

C4

IN

G3

G8

VCC1V8

4.7K

22

22

22

NAND_WP#

DSP_EMIFD0

DSP_EMIFD1

DSP_EMIFD2

DSP_EMIFD3

DSP_EMIFD4

DSP_EMIFD5

DSP_EMIFD6

DSP_EMIFD7

R134

4.7K

DSP_EMIFWAIT0

R135

4.7K

NAND_WP#

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

WE

WP

RE

R/B

CE

CLE

ALE

DNU1

DNU2

(29)

(29)

F7

K8

K3

C5

TI_TMS320C6678

VSS1

VSS2

VSS3

VSS4

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC38

VCC1

VCC2

VCC3

VCC4

NUMONYX_NAND512R3A2DZA6E

A1

A10

A2

A9

B1

B10

B9

D6

D7

D8

E3

E4

E5

E6

E7

E8

F3

F4

F5

F6

F8

G5

G6

G7

H3

H5

H6

H7

J3

J5

L1

L10

L2

L9

M1

M10

M2

M9

G4

D3

H8

J6

C

VCC1V8

C519

0.1uF

16V

C159

0.1uF

16V

C158

10uF

6.3V

B

B

A

A

Designed for TI by ADVANTECH

Title

DSP_EMIF

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

14

of

40

5

4

3

2

1

JTAG & EMU

DSP_TRST#_R

XDS560V2 power connector

R905

4.7K

VCC5

(30)

VCC1V8

C555

8.2pF

50V

DSP_TMS

R893

4.7K

DSP_TDI

R895

4.7K

DSP_TCK

R896

4.7K

DSP_TDO

R897

4.7K

DSP_TRST#

R900

NL/4.75K

XDS560_IL

560V2_PWR1

1

2

3

4

5

6

7

8

IN

VCC3V3_AUX

C537

10uF

6.3V

C536

0.1uF

16V

C553

10uF

16V

(26)

EXT_EMU_DET0

R904

(26)

DSP1I

VCC1V8

P28

P29

P27

N29

R29

R226

R232

R233

N23

NL/0

N24

NL/0

1K 1% AH28

R234

R235

NL/0

0

AH19

AF19

TRSTz

TMS

TDI

TCK

TDO

JTAG/EMU/DFT

RSV03

RSV02

RSV01

RSV08

RSV09

C

pinout_rev0_3_2_customer

EMU00

EMU01

EMU02

EMU03

EMU04

EMU05

EMU06

EMU07

EMU08

EMU09

EMU10

EMU11

EMU12

EMU13

EMU14

EMU15

EMU16

EMU17

EMU18

AC29

AC28

AC27

AC26

AD29

AD28

AD27

AE29

AE28

AF29

AE27

AF28

AG29

AD26

AG28

AG27

AJ27

AF27

AH27

DSP_EMU_00

DSP_EMU_01

DSP_EMU_02

DSP_EMU_03

DSP_EMU_04

DSP_EMU_05

DSP_EMU_06

DSP_EMU_07

DSP_EMU_08

DSP_EMU_09

DSP_EMU_10

DSP_EMU_11

DSP_EMU_12

DSP_EMU_13

DSP_EMU_14

DSP_EMU_15

DSP_EMU_16

DSP_EMU_17

DSP_EMU_18

D

NL/10K

1%

BI

BI

DSP_EMU_00

DSP_EMU_01

(26)

EMU_TMS

(26)

(26)

EMU_TDI

OUT

OUT

(26)

EMU_TDO

IN

VCC1V8

(26)

EMU_TCK

OUT

EMU_EMU_00

OUT

TRGRSTZ

BI

R290

EMU_TMS

DSP_EMU_17

EMU_TDI

DSP_EMU_14

DSP_EMU_12

EMU_TDO

DSP_EMU_09

DSP_EMU_07

DSP_EMU_05

EMU_TCK

DSP_EMU_02

EMU_EMU_00

4.7K

R295

R279

R294

R280

R276

R293

R658

R271

R270

R268

R292

R266

R287(26)

TRGRSTZ

10

10

10

10

10

10

100 1%

10

10

10

10

10

10

DSP_TMS_R

DSP_EMU_17_R

DSP_TDI_R

DSP_EMU_14_R

DSP_EMU_12_R

DSP_TDO_R

DSP_TVD

DSP_EMU_09_R

DSP_EMU_07_R

DSP_EMU_05_R

EMU_TCK_R

DSP_EMU_02_R

DSP_EMU_00_R

B1

D1

A1

C1

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

DSP_EMU_18_R

DSP_TRST#_R

DSP_EMU_16_R

DSP_EMU_15_R

DSP_EMU_13_R

DSP_EMU_11_R

DSP_TCK_R

DSP_EMU_10_R

DSP_EMU_08_R

DSP_EMU_06_R

DSP_EMU_04_R

DSP_EMU_03_R

DSP_EMU_01_R

R282

R288

R278

R277

R275

R274

R291

R281

R272

R273

R269

R267

R286

DSP_EMU_18

EMU_TRST#

DSP_EMU_16

DSP_EMU_15

DSP_EMU_13

DSP_EMU_11

EMU_TCK_R

DSP_EMU_10

DSP_EMU_08

DSP_EMU_06

DSP_EMU_04

DSP_EMU_03

EMU_EMU_01

10

10

10

10

10

10

10

10

10

10

10

10

10

OUT

BI

EMU_TRST#

(26)

EMU_EMU_01

(26)

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

PTH

H1

DSP_TRST#

DSP_TMS

DSP_TDI

DSP_TCK

DSP_TDO

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

1%

VCC1V8

IN

IN

IN

IN

OUT

1%

EXT_EMU_DET0

OUT

PH_4x2V_2.54mm

(30)

DSP_TRST#

DSP_TMS

DSP_TDI

DSP_TCK

DSP_TDO

4.75K

PTH

VCC3V3_AUX

R67

49.9

1%

(26)

(26)

(26)

(26)

(26)

R903

VCC3V3_AUX

H2

C551

0.1uF

16V

D

EMU_EMU_00

R901

4.75K

EMU_EMU_01

R902

4.75K

VCC1V8

EMU1

BB_30x2V_S1.27mm

C

TI_TMS320C6678

TSIP0, 1

DSP1T

B

(10)

(10)

(10)

(10)

TSIP0_RX0

TSIP0_RX1

TSIP0_RX2

TSIP0_RX3

(30)

(30)

DSP_TSIP0_FSA0

DSP_TSIP0_FSB0

AH26

AJ25

AD23

AD24

AC23

AH25

AC24

AE25

IN

IN

IN

IN

IN

IN

(30)

(30)

DSP_TSIP0_CLKA0

DSP_TSIP0_CLKB0

IN

IN

(10)

(10)

(10)

(10)

TSIP1_RX0

TSIP1_RX1

TSIP1_RX2

TSIP1_RX3

IN

IN

IN

IN

(30)

(30)

DSP_TSIP1_FSA1

DSP_TSIP1_FSB1

IN

IN

(30)

(30)

DSP_TSIP1_CLKA1

DSP_TSIP1_CLKB1

IN

IN

DSP_TSIP0_FSA0

DSP_TSIP0_FSB0

AJ26

AG26

DSP_TSIP0_CLKA0

DSP_TSIP0_CLKB0

AF25

AG25

AE22

AD21

AC21

AJ21

AH22

AJ20

AH21

AG21

DSP_TSIP1_FSA1

DSP_TSIP1_FSB1

AG23

AJ22

DSP_TSIP1_CLKA1

DSP_TSIP1_CLKB1

AJ23

AH23

TR00

TR01

TR02

TR03

TR04

TR05

TR06

TR07

TSIP0

TX00

TX01

TX02

TX03

TX04

TX05

TX06

TX07

AE24

AD25

AJ24

AG24

AH24

AF24

AE23

AF23

OUT

OUT

OUT

OUT

TSIP0_TX0

TSIP0_TX1

TSIP0_TX2

TSIP0_TX3

(10)

(10)

(10)

(10)

OUT

OUT

OUT

OUT

TSIP1_TX0

TSIP1_TX1

TSIP1_TX2

TSIP1_TX3

(10)

(10)

(10)

(10)

B

FSA0

FSB0

CLKA0

CLKB0

TR10

TR11

TR12

TR13

TR14

TR15

TR16

TR17

TSIP1

TX10

TX11

TX12

TX13

TX14

TX15

TX16

TX17

AF21

AD22

AC22

AE21

AG20

AE20

AH20

AF20

FSA1

FSB1

CLKA1

CLKB1

pinout_rev0_3_2_customer

TI_TMS320C6678

A

A

Designed for TI by ADVANTECH

Title

DSP_JTAG_EMU_TSIP

Size

C

Date:

5

4

3

2

Document Number

Rev

A101-1

DSPM-8301E

Tuesday, March 08, 2011

Sheet

1

15

of

40

5

4

3

2

I2C, TIMER0,1, SPI, UART

1

16M SPI NOR Flash

1M-bit I2C EEPROM

VCC1V8

VCC1V8

C303

0.1uF

16V

(10,29)

(29,31)

(29)

(29)

(29) D

DSP_SCL

DSP_SDA

DSP_TIMI0

DSP_TIMI1

DSP_TIMO0

DSP_TIMO1

IN

IN

OUT

OUT

R341

R347

DSP1M

AD3

SCL

AC4 (10,29)

SDA

L24

L26 TIMI0/PCIESSEN

L25 TIMI1

M26 TIMO0

TIMO1

DSP_SCL

DSP_SDA

OUT

BI

10

10

R185

4.7K

I2C

TIMER0

TIMER1

SPI UART

SPISCS0

SPISCS1

SPICLK

SPIDIN

SPIDOUT

UARTRTS

UARTCTS

UARTTXD

UARTRXD

R186

4.7K

pinout_rev0_3_2_customer

AG1 R337

AG2

AE1 R340

AD2

AB1 R363

10

AB2 R377

AB3 R378

AC1

AD1

10

10

10

10

DSP_SSPCS0

DSP_SSPCS1

DSP_SSPCK

DSP_SSPMISO

DSP_SSPMOSI

VCC1V8

R427

NL/0

SPI1

OUT

DSP_SSPCS1

(29,30)

IN

OUT

DSP_SSPMISO

DSP_SSPMOSI

(29,30)

(29,30)

VCC1V8

DSP_UARTRTS_V1P8

DSP_UARTCTS_V1P8

DSP_UARTTXD_V1P8

DSP_UARTRXD_V1P8

(30)

NOR_WP#

NOR_HD#

4.7K

DSP_SSPCS0

NOR_SSPCK

DSP_SSPMOSI

DSP_SSPMISO

R398

10

NOR_WP#

R163

4.7K

R162

2

1

7

16

15

8

9

10

IN

VCC

HOLD/DQ3

S

SCK

DQ0

DQ1

W/Vpp/DQ2

VSS

DU/NC8

DU/NC7

DU/NC6

DU/NC5

DU/NC4

DU/NC3

DU/NC2

DU/NC1

14

13

12

11

6

5

4

3

R428

NL/0

R429

NL/0

EEPROM1

STMicro_M24M01-HRMN6TP

1

2

3

4

R164

NL/0

R165

0

A0

A1

A2

VSS

VCC

WP

SCL

SDA

C304

0.1uF

16V

8

7

6

5

EEPROM_WP

DSP_SCL

DSP_SDA

R168

R169

4.7K

4.7K

D

R167

0

R179

4.7K

5%

NUMONYX_N25Q128A21BSF40F

IN

(30)

EEPROM_WP

VCC1V8

TI_TMS320C6678

DSP_SSPMISO

R166

4.7K

VCC1V8

B21

2200pF

700mA

1

GPIO

3

VCC1V8

U255

R369

33

R368

33

1

2

3

4

5

6

7

DSP1L

DSP_GPIO_00

DSP_GPIO_01

DSP_GPIO_02

DSP_GPIO_03

DSP_GPIO_04

DSP_GPIO_05

DSP_GPIO_06

DSP_GPIO_07

DSP_GPIO_08

DSP_GPIO_09

DSP_GPIO_10

DSP_GPIO_11

DSP_GPIO_12

DSP_GPIO_13

DSP_GPIO_14

DSP_GPIO_15

C

R938

R939

R940

R941

R942

R943

R944

R945

R946

R947

R948

R949

R950

R951

R952

R953

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

DSP_GPIO_R_00

(29,31)

DSP_GPIO_R_01

(29,31)

DSP_GPIO_R_02

(29,31)

DSP_GPIO_R_03

(29,31)

DSP_GPIO_R_04

(29,31)

DSP_GPIO_R_05

(29,31)

DSP_GPIO_R_06

(29,31)

DSP_GPIO_R_07

(29,31)

DSP_GPIO_R_08

(29,31)

DSP_GPIO_R_09

(29,31)

DSP_GPIO_R_10

(29,31)

DSP_GPIO_R_11

(29,31)

DSP_GPIO_R_12

(29,31)

DSP_GPIO_R_13

(29,31)

DSP_GPIO_R_14

(29,31)

DSP_GPIO_R_15

(29,31)

H25

J28

J29

J26

J25

J27

J24

K27

K28

K26

K29

L28

L29

K25

K24

L27

GPIO00/LENDIAN

GPIO01/BOOTMODE00

GPIO02/BOOTMODE01

GPIO03/BOOTMODE02

GPIO04/BOOTMODE03

GPIO05/BOOTMODE04

GPIO06/BOOTMODE05

GPIO07/BOOTMODE06

GPIO08/BOOTMODE07

GPIO09/BOOTMODE08

GPIO10/BOOTMODE09

GPIO11/BOOTMODE10

GPIO12/BOOTMODE11

GPIO13/BOOTMODE12

GPIO14/PCIESSMODE0

GPIO15/PCIESSMODE1

(29)

GPIO

PH_SSPCK

OUT

1OE

1A

1Y

2OE

2A

2Y

GND

VCC

4OE

4A

4Y

3OE

3A

3Y

14

13

12

11

10

9

8

2

DSP_SSPCK

NOR_SSPCK

R202

DSP_SSPCK

33

OUT

(30)

FPGA_SSPCK

TI_SN74ALVC125PWR

C

pinout_rev0_3_2_customer

VCC1V8

VCC3V3_AUX

TI_TMS320C6678

C368

0.1uF

16V

C367

0.1uF

16V

U24

TI_SN74AVC4T245PWR

16

15

14

13

12

11

10

9

DSP_UARTRTS_V1P8

DSP_UARTTXD_V1P8

DSP_UARTCTS_V1P8

DSP_UARTRXD_V1P8

VCCB

1OE

2OE

1B1

1B2

2B1

2B2

GND2

1

2

3

4

5

6

7

8

VCCA

1DIR

2DIR

1A1

1A2

2A1

2A2

GND1

DSP_UARTRTS

DSP_UARTTXD

DSP_UARTCTS

DSP_UARTRXD

OUT

OUT

IN

IN

(29)

(29)

(29)

(29)

DSP_UARTRTS

DSP_UARTTXD

DSP_UARTCTS

DSP_UARTRXD

Reset Control

COM_SEL1(2-4)

DSP1J

B

(30)

(30)

(30)

DSP_PORZ

DSP_RESETFULLZ

DSP_RESETZ

DSP_PORZ

DSP_RESETFULLZ

DSP_RESETZ

IN

IN

IN

(30)

DSP_PACLKSEL

IN

(30)

(30)

(30)

(30)

(30)

(30)

(30)