3-phase VSC Modifications for Symmetrical and

advertisement

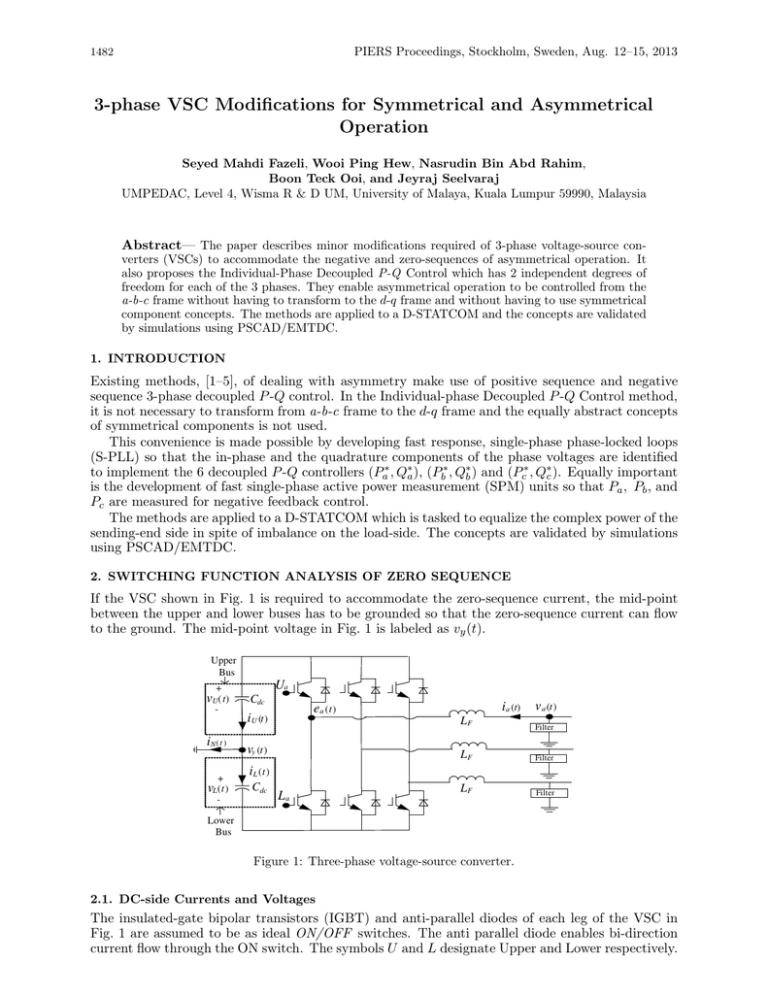

PIERS Proceedings, Stockholm, Sweden, Aug. 12–15, 2013 1482 3-phase VSC Modifications for Symmetrical and Asymmetrical Operation Seyed Mahdi Fazeli, Wooi Ping Hew, Nasrudin Bin Abd Rahim, Boon Teck Ooi, and Jeyraj Seelvaraj UMPEDAC, Level 4, Wisma R & D UM, University of Malaya, Kuala Lumpur 59990, Malaysia Abstract— The paper describes minor modifications required of 3-phase voltage-source converters (VSCs) to accommodate the negative and zero-sequences of asymmetrical operation. It also proposes the Individual-Phase Decoupled P-Q Control which has 2 independent degrees of freedom for each of the 3 phases. They enable asymmetrical operation to be controlled from the a-b-c frame without having to transform to the d-q frame and without having to use symmetrical component concepts. The methods are applied to a D-STATCOM and the concepts are validated by simulations using PSCAD/EMTDC. 1. INTRODUCTION Existing methods, [1–5], of dealing with asymmetry make use of positive sequence and negative sequence 3-phase decoupled P -Q control. In the Individual-phase Decoupled P -Q Control method, it is not necessary to transform from a-b-c frame to the d-q frame and the equally abstract concepts of symmetrical components is not used. This convenience is made possible by developing fast response, single-phase phase-locked loops (S-PLL) so that the in-phase and the quadrature components of the phase voltages are identified to implement the 6 decoupled P -Q controllers (Pa∗ , Q∗a ), (Pb∗ , Q∗b ) and (Pc∗ , Q∗c ). Equally important is the development of fast single-phase active power measurement (SPM) units so that Pa , Pb , and Pc are measured for negative feedback control. The methods are applied to a D-STATCOM which is tasked to equalize the complex power of the sending-end side in spite of imbalance on the load-side. The concepts are validated by simulations using PSCAD/EMTDC. 2. SWITCHING FUNCTION ANALYSIS OF ZERO SEQUENCE If the VSC shown in Fig. 1 is required to accommodate the zero-sequence current, the mid-point between the upper and lower buses has to be grounded so that the zero-sequence current can flow to the ground. The mid-point voltage in Fig. 1 is labeled as vy (t). Upper Bus Ua + vU( t) - iN ( t ) + vL (t) - Cdc ia (t) ea (t) iU (t) LF vy (t) v a (t) Filter LF Filter LF Filter iL (t) Cdc La Lower Bus Figure 1: Three-phase voltage-source converter. 2.1. DC-side Currents and Voltages The insulated-gate bipolar transistors (IGBT) and anti-parallel diodes of each leg of the VSC in Fig. 1 are assumed to be as ideal ON/OFF switches. The anti parallel diode enables bi-direction current flow through the ON switch. The symbols U and L designate Upper and Lower respectively. Progress In Electromagnetics Research Symposium Proceedings, Stockholm, Sweden, Aug. 12-15, 2013 1483 The upper and lower bus currents are the sums of the current contributions from the 3 phases, iU (t) = 0.5[(Sa (t) + 1)ia (t) + (Sb (t) + 1)ib (t) + (Sc (t) + 1)ic (t)] iL (t) = 0.5[(Sa (t) − 1)ia (t) + (Sb (t) − 1)ib (t) + (Sc (t) − 1)ic (t)] (1) (2) Note that applying Kirchhoff’s current law at the node of vy (t) iN (t) = iU (t) − iL (t) (3) Equations (1) and (2) can be rewritten as: iU (t) = iM (t) + 0.5iN (t) iL (t) = iM (t) − 0.5iN (t) (4) (5) iM (t) = 0.5[Sa (t)ia (t) + Sb (t)ib (t) + Sc (t)ic (t)] (6) where From definition of the zero sequence current i0 (t) = [ia (t) + ib (t) + ic (t)] 3 (7) From (7), iN (t) = 3 × i0 (t). The interpretation from (4) and (5) is: on admission into the VSC, the zero-sequence current or neutral current after entering the VSC divide into two, 0.5iN (t), one half flowing along the upper bus and the other half along the lower bus and merge again at the mid-point of the buses. 2.2. Charging of dc Capacitors The voltages across the upper and lower buses with capacitors of size C are based on the charging equations: dvU (t) = iU (t) = iM (t) + 0.5iN (t) dt dvL (t) Cdc = iL (t) = iM (t) − 0.5iN (t) dt Cdc (8) (9) Adding (18) and (19) d[vU (t) + vL (t)] = 2iM (t) (10) dt From (10) it is clear that [vU (t) + vL (t)] is charged by 2iM (t) and is not affected by iN (t). On the other hand, from (8) and (9) when iN (t) has a dc component, the average voltage of the upper and lower buses become unbalanced. Figure 2 shows the simulated voltages and currents in the dc side of the VSC under slight imbalance whereas ripples from PWM switching have been filtered. Fig. 2(a) shows the currents of the upper bus (see (4)) and the lower bus (see (5)) which contain 50 Hz components of the zero-sequence and 100 Hz components of single-phase power. Fig. 2(a) also shows the 50 Hz neutral current. Fig. 2(b) shows the bus-to-bus voltage [vdc (t) = vU (t) + vL (t)] (see (10)) which is a dc constant with a 100 Hz ripple. But it is free of the 50 Hz of the zero-sequence current. Fig. 2(c) shows a dc average together with 50 Hz and 100 Hz components in the voltages of the upper and lower buses (see (8) and (9) respectively). In Fig. 2(c), the average voltages of the upper and lower buses are not significantly imbalance because the zero-sequence is at the steady-state stage. In the long term, the accumulation of dc off-sets in the zero-sequence current in transient events can cause imbalance. Cdc 3. DOUBLE FREQUENCY POWER IN VSC Unless the double frequency components of individual single-phases ac power are cancelled by symmetrical balance, they appear as a double frequency ripple riding on the constant dc voltage in vdc (t). This has been attributed to the negative sequence but a correction needs to be made because the double frequency pulsation is inherent in all single-phase power. Therefore, the zero sequence voltage and current together also gives rise to the double frequency dc voltage ripple [9]. PIERS Proceedings, Stockholm, Sweden, Aug. 12–15, 2013 Up and Low buses and neutral currents 1484 1 (a) Neutral 0. 5 Lower Upper 0 -0.5 bus to bus voltage(p.u) -1 1.02 0.99 0.96 0.55 Up and Low bus voltages (p.u) (b) (c) Upper 0.5 Lower 0.45 0.4 5. 94 5. 95 5. 96 5. 97 5. 98 5. 99 6 Time (s) Figure 2: DC-side voltages and currents: (a) currents of upper and lower buses and neutral; (b) bus-to-bus voltage [vdc (t) = vU (t) + vL (t)]; (c) voltages of upper and lower buses. In Sinusoidal Pulse Width Modulation (SPWM), the fundamental component of the pulsed voltage at the terminal of the a-phase of the VSC is: va (t) = ma (t)vdc (t) 2Vtr (11) where ma (t) is the modulating signal and Vtr is the peak of the triangle carrier. In view of the double frequency fluctuation in the dc link voltage, vdc (t), the output voltage is no longer the linearly amplified form of the modulating signal ma (t). If the control signal of the a-phase of the VSC is MSP W M −a (t), the linear amplifier property of the VSC is restored by measuring vdc (t) and modifying the modulating signal as: ma (t) = MSPWM -a (t)Vdc-REF vdc (t) (12) va (t) = MSPWM -a (t)Vdc-REF 2Vtr (13) With this compensation As this technique is well known and widely applied since [11] for example, no further elaboration is necessary. 4. INDIVIDUAL-PHASE DECOUPLED P-Q CONTROL 4.1. Single-phase Decoupled P-Q Control The original time functions of the a-phase voltage and current are: va (t) = ImVa ej(ωt+θV -a ) = Va sin(ωt + θV -a ) ia (t) = ImIa ej(ωt+θI -a ) = Ia sin(ωt + θI -a ) (14) (15) Phasor representations of them are: V¯a = Va ejθV -a = Vpa + jVqa I¯a = Ia ejθI -a = Ipa + jIqa (16) (17) Progress In Electromagnetics Research Symposium Proceedings, Stockholm, Sweden, Aug. 12-15, 2013 1485 where the subscripts p and q are respectively the in-phase and in-quadrate components of the sinusoidal time-varying components of voltage and current. By definition, the complex power is: S¯a = Pa + jQa = (Vpa + jVqa )(Ipa − jIqa ) (18) When a single-phase phase-locked loop (S-PLL) is synchronized to the a-phase voltage waveform, using of the S-PLL which acquires (ωt+θV -a ) as reference for the sinusoidal time-varying functions, the phasor representation of (16) simplifies to: V¯a = Vpa Continuing to use the S-PLL, by injecting a controlled current of the a-phase as ¡ ∗ ¢ ∗ ∗ − jIqa I¯a = Ipa the controlled complex power is ¡ ∗ ¢ ∗ Pa∗ + jQ∗a = Vpa Ipa − jIqa (19) (20) (21) The symbol (*) is used to denote a control variable. In order to arrive at the controlled complex power of (21), the S-PLL generates the in-phase function sin(ωt + θV -a ) and in-quadrature function cos(ωt + θV -a ). Active power Pa∗ and the ∗ and I ∗ to sin(ωt + θ reactive power Q∗a control of the a-phase consists of multiplying Ipa V -a ) and qa cos(ωt + θV -a ) respectively to form the control signal ∗ ∗ MSPWM -a (t) = Ipa sin(ωt + θV -a ) − Iqa cos(ωt + θV -a ) (22) Although the voltage-source converter (VSC) outputs voltage pulses, a variety of methods, such as “dead-beat control” which make use feed forward and feedback, are available so that (35) is implemented. Decoupled control of the complex powers for b-phase (Pb∗ , Q∗b ) and c-phase (Pc∗ , Q∗c ) are also ∗ , I ∗ ) and (I ∗ , I ∗ ) to the in-phase and in-quadrature functions generachieved by multiplying (Ipb pc qc qb ated by the S-PLL of the b- and c-phase respectively. 5. SINGLE-PHASE MEASUREMENT UNITS 5.1. Single-phase Phase-locked Loop (S-PLL) Figure 3(a) is the schematic of the S-PLL of this paper. The R-L-C notch filter [12], shown in Fig. 3(b), eliminates the double frequency component in the output of the “detection stage” of the phase-locked loop. The components L and C are tuned to eliminate the double frequency 2f0 = 100 Hz. R is designed to ensure that there is sufficient attenuation of of frequencies at 2f0 (1 ± 0.05) Hz. This is because the line frequency is allowed deviation of 5%. The Bode diagram of the magnitude in Fig. 4(a) shows that attenuation below −25 dB at 5% deviation can be designed using the notch filter. Unlike a low pass filter in traditional S-PLL, the high frequency end of the spectrum is kept intact and therefore the speed of response is fast. The simulation of Fig. 4(b) shows that the response to step change is well within 10 ms. (a) (b) Figure 3: (a) Single-phase PLL based on a notch filter; (b) notch filter. PIERS Proceedings, Stockholm, Sweden, Aug. 12–15, 2013 1 0 -25 -150 Amplitude Magnitude (dB) 1486 0.5 0 90 110 Frequency (Hz) 1 200 1.01 Time (s) (b) (a) Figure 4: Notch filter. (a) Frequency response; (b) step response. 5.2. Single-phase Active Power Measurement Instantaneous active power is measured by electronically multiplying v(t) × i(t) and removing the double frequency term by a notch filter as illustrated in Fig. 5. - a + ZTa b + ZTb SLb =PLb+jQ Lb ZLb + ZTc SLc = PLc+jQ Lc ZLc SLa =PLa +jQ La ZLa v(t) Notch Filter - P iN(t) - i(t) Figure 5: Active power measurement. c iN(t) Figure 6: 3-phase network. 6. IMPLEMENTATION OF INDIVIDUAL-PHASE DECOUPLED P -Q CONTROL Figure 8 shows a balanced 3-phase ac voltage source at the sending-end connected to unequal load impedances ZLa , ZLb , ZLc by balanced transmission-line impedances (ZT a , ZT b , ZT c ). The complex powers of the loads, S̄La , S̄Lb , S̄Lc , are unequal. The neutrals of the wye (Y) connections aregrounded so that there is zero-sequence current under imbalance. The transmission line impedances are large so that there is voltage droop at the point of common connection (PCC). The complex powers can be equalized by redistributing the active powers of the unequal loads, PLa , PLb , PLc , between the transmission lines so that each transmission line carries the average 1 3 1 vdc (t ) Figure 7: Block diagram decoupled P -Q control of the a-phase. Progress In Electromagnetics Research Symposium Proceedings, Stockholm, Sweden, Aug. 12-15, 2013 1487 - a+ ZTa b - + ZTb Za CB- C c - + ZTc Zb Zc CB-D Zd STATCOM Figure 8: System of simulation test. power of the 3 loads, Pave , that is: Pave = PLa + PLb + PLc 3 (23) This can be accomplished by a complex power compensator. The compensator injects IndividualPhase complex powers at the PCC: ∗ ∗ S̄Ca = PRDa + jQ∗Ca ∗ ∗ S̄Cb = PRDb + jQ∗Cb ∗ S̄Cc = ∗ PRDc + (24) jQ∗Cc where ∗ PRDa = PLa − Pave ∗ PRDb = PLb − Pave ∗ PRDc = PLC − Pave (25) Because the total active power for compensator always is zero, here, a system such as a DSTATCOM can be considered as complex power compensator. The Q-control (Q∗Ca , Q∗Cb , Q∗Cc ) of each phase of the D-STATCOM is used to regulate the output ac voltage magnitude at the PCC. Figure 9 shows the function blocks leading to the SPWM input of the a-phase of the DSTATCOM: MSPWM -a (t) of (22) and ma (t) of (12). The function blocks of the b-phase and the c-phase are similar. The following blocks are common to all the three phases: (i) the computation of the average load active power, Pave , (23); (ii) the formation of the loss of the D-STATCOM, ∗ Pdc -loss ; (iii)0 the compensation of the dc voltage ripple by multiplication of (Vdc-Ref /vdc (t)) (located between MSPWM -a (t) and MSPWM -a (t)); (iv) Balancing the DC bus voltages. The ac voltage magnitude Va is compared with the ac voltage reference. The error after passing ∗ which is multiplied to cos(ωt+θ the proportional-integral gain (P-I) block becomes Iqa V -a ) (obtained from the S-PLL) to form one component of MSPWM -a (t). In P-control, the average active load power Pave of (23) (formed from SPM measurements of the active powers of all the phases at the load side) is applied as one component of active power ∗ reference. The other component is Pdc -loss , the active power required to replenish ohmic losses of the D-STATCOM so as to regulate the bus-to-bus voltage at Vdc-REF . The combined power ∗ line power PSa and the error after passing reference (Pave + Pdc -loss ) is compared with transmission ∗ which is multiplied to sin(ωt + θ a proportional-integral gain (P-I) block becomes Ipa V -a ) to form the other component of MSPWM-a (t). MSPWM-a (t) is multiplied by [Vdc-Ref /vdc (t)] to compensate for the dc voltage fluctuation (see (26)). Finally, the zero-sequence signal ibal (t) (see (21) to (23)) is added to balance the dc voltages of the upper and lower buses . 7. VALIDATION BY SIMULATIONS A continuous simulation test (0.0 s ≤ t < 6.0 s) has been conducted on the system of Fig. 8 with the D-STATCOM of Fig. 1. Originally, Circuit Breakers CB-C is closed and CB-D is open. Loss of a load is simulated by opening CB-C during 4.0 s ≤ t < 5.0 s. The simulation results are chosen to PIERS Proceedings, Stockholm, Sweden, Aug. 12–15, 2013 1488 c-pha se 0 -0.5 4 a-pha se 2 0.5 3.98 4.12 Time (s) b-phase 0 -1 -2 3.98 4 (b) 0.4 0.2 4 4.08 Time (s) 4.12 Time (s) (a) 0 3.98 c-pha se 1 4.12 Zero Sequence Current at the source side Negative sequence Current at the source side b-phase Phase Current (p.u) Phase Voltages (p.u) a-pha se 1 0.4 0.2 0 3.98 4 4.08 4.12 Time (s) (c) (d) Up and Low bus Voltages (p.u) Uppe r 0.55 0.5 0.45 0.4 3.98 Lower 4 4.12 Time (s) (e) Figure 9: Simulation results before and after t = 4.0 s. (a) ac voltages; (b) ac currents; (c) negative sequence current at the source side; (d) zero sequence current at the source side; (e) upper and lower bus voltages. show that voltages and the currents of the transmission lines are balanced at the Point of Common Coupling (PCC). Implicitly, the balanced voltages and currents imply balanced active and reactive powers of the three phases. The active and reactive powers of the individual phases are balanced. 7.1. Simulation Test Results At t = 4.0 s, CB-C is opened to simulate loss of the load, Zb . Figs. 9(a) and (b) show the voltages and currents. The transmission line currents decrease because the source voltages supply power to only 2 of the 3 load impedances. In order to high-light the fast response (transient duration about 80 ms), the negative-sequence and the zero sequence of the- currents are computed from the simulated currents and displayed in Figs. 9(c) and (d). Fig. 9(e) displays the upper vU (t) and lower vL (t) dc bus voltages proving that scheme for Balancing the DC buses in Fig. 9 is successful. 8. CONCLUSIONS The paper has described modifications by which the 3-phase voltage-source converter is suited to interface with the ac power system under asymmetrical operating conditions. Analysis is presented to show how the zero-sequence passes through the VSC and how dc capacitor voltage imbalance due to the zero sequence is eliminated by negative feedback. A compensation scheme is applied to counter the double frequency voltage pulsation across the dc buses. The method of Individual-Phase Decoupled P -Q Control enables both symmetrical and asymmetrical operation to be controlled from the straight forward a-b-c reference frame, without the need to use the complication of symmetrical component analysis. ACKNOWLEDGMENT This research is supported by the Research Grant ERGS/FASA 1/2011 ER027-2011A from the Ministry of Higher Education Malaysia. Progress In Electromagnetics Research Symposium Proceedings, Stockholm, Sweden, Aug. 12-15, 2013 1489 REFERENCES 1. Awad, H., J. Svensson, and M. Bollen, “Practical implementation of delayed signal cancellation method for phase-sequence separation,” IEEE Transactions on Power Electronics, Vol. 19, No. 3, 837–846, 2004. 2. Awad, H., J. Svensson, and M. J. Bollen, “Tuning software phase-locked loop for seriesconnected converters,” IEEE Transactions on Power Delivery, Vol. 20, No. 1, 300–308, 2005. 3. Li, Y., D. M. Vilathgamuwa, and P. C. Loh, “Microgrid power quality enhancement using a three-phase four-wire grid-interfacing compensator,” IEEE Transactions on Industry Applications, Vol. 41, No. 6, 1707–1719, 2005. 4. Svensson, J., M. Bongiorno, and A. Sannino, “Practical implementation of delayed signal cancellation method for phase-sequence separation,” IEEE Transactions on Power Delivery, Vol. 22, No. 1, 18–26, 2007. 5. Bongiorno, M., J. Svensson, and A. Sannino, “Effect of sampling frequency and harmonics on delay-based phase-sequence estimation method,” IEEE Transactions on Power Delivery, Vol. 23, No. 3, 1664–1672, 2008. 6. Hatano, N. and T. Ise, “Control scheme of cascaded H-bridge STATCOM using zero-sequence voltage and negative-sequence current,” IEEE Transactions on Power Delivery, Vol. 25, No. 2, 543–550, 2010. 7. Karimi-Ghartemani, M. and H. Karimi, “Processing of symmetrical components in timedomain,” IEEE Transactions on Power Systems, Vol. 22, No. 2, 572–579, 2007. 8. Aredes, M. and E. H. Watanabe, “New control algorithms for series and shunt three-phase fourwire active power filters,” IEEE Transactions on Power Delivery, Vol. 10, No. 3, 1649–1656, 1995. 9. Aredes, M. and E. H. Watanabe, “ Three-phase four-wire shunt active filter control strategies,” IEEE Transactions on Power Electronics, Vol. 12, No. 2, 311–318, 1997. 10. Enjeti, P. N. and W. Shireen, “A new technique to reject DC-link voltage ripple for inverters operating on programmed PWM waveforms,” IEEE Transactions on Power Electronics, Vol. 7, No. 1, 171–180, 1992. 11. Chen, W. K., The Circuits and Filters Handbook, 1st Edition, 2161–2192, CRC, USA, 1995. 12. Hsieh, G. C. and J. C. Hung, “Phase-locked loop techniques. A survey,” IEEE Trans. Industrial Elec., Vol. 43, No. 6, 609–615, Dec. 1996.