chapter 3 psm buck dc-dc converter under discontinuous conduction

advertisement

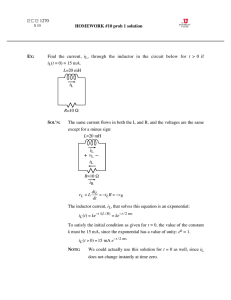

71 CHAPTER 3 PSM BUCK DC-DC CONVERTER UNDER DISCONTINUOUS CONDUCTION MODE Discontinuous conduction mode is the operating mode in which the inductor current reaches zero periodically. In pulse width modulated converters under discontinuous conduction mode the inductor current rises during ON time and when the switch is OFF the current falls and reaches zero before the end of the cycle. There is a brief duration of time over which the inductor current is zero and hence each switching cycle starts from zero inductor current. While this is happening during charging cycles in a PSM converter, the load discharges the capacitor during skipping cycle (Angkititrakul and Hu 2008). PSM buck converter discussed in this chapter is a DC-DC converter with constant frequency and constant duty cycle (D). Condition for DCM operation is discussed in section 3.1. Modeling of PSM converter and simulation results are provided in section 3.2. Modeling and simulation results of PSM converter operated in forced discontinuous conduction mode due to pulse skipping are provided in sections 3.3 and 3.4. Exhibition of nonlinear phenomena is studied and the results for PSM converter under DCM are included in sections 3.5 and for PSM converter under forced DCM in section 3.6. Discontinuous conduction mode with switched inductor is discussed in section 72 3.1 DISCONTINUOUS CONDUCTION MODE IN BUCK CONVERTER In a buck converter with constant frequency operation and with inductance and duty cycle fixed, discontinuous conduction mode sets in during loads when load resistance is greater than the critical resistance, Rcr (Erickson and Maksimovic 2001). In terms of K parameter, where K = 2L/RTs which depends on the circuit values and the choice of fsw and Kc, the critical parameter depending on the converter duty cycle D, discontinuous conduction results when K < Kc, where for buck converter Kc = (1-D). Figure 3.1 K Vs D plot showing DCM/CCM regions separated by the borderline As shown in the plot between K and D in Figure 3.1, for a buck converter, if the parameter values are so chosen that K>1, DCM would never occur. For PSM buck converter since the D value is fixed, Kc is fixed for charging cycles. If the parameter values make K < Kc, operation will be in DCM throughout. 73 It is possible to note that at K=Kc the average inductor current is equal to one half of inductor current ripple as shown in Figure 3.2. Any decrease in load current, which equals the average inductor current would result in discontinuous conduction in converters with devices that block negative current. With DCM the device peak current has to be higher than that in continuous conduction mode since the peak current has to be at least twice the load current. Figure 3.2 Average inductor current or the load DC current equals half the inductor ripple Referring to Figure 3.2 let the maximum and minimum currents are IU and IL. Then the ripple magnitude I IU IL (3.1) With upper and lower values fixed, the inductor current ripple is fixed and the dc component is midway and hence is equal to I/2. Hence I L,avg I 2 0 .5 I U IL (3.2) It is possible to express the inductor current ripple quantity as IL I L,avg Vin Vo ton 2L I L ,avg Vo toff 2L (3.3) 74 Vin Vo t on Vo t off (3.4) 2L Since the load current I0 = ILavg discontinuous conduction mode would be the result when I0 Vin Vo t on Vo t off 2L (3.5) While comparing the CCM and DCM operation in converters, output voltage in DCM is a function of load resistance, as given by Equation (3.36), and the peak inductor and device currents are higher. V0 Vin where 2 1 1 4 K / D1 2 (3.6) K=2L/RTs Valid for K<Kcr Since the extinction time tx is given by tx DVin fV0 (3.7) D2 can be determined from TX=D1+D2 in Seconds. 3.2 MODELLING AND SIMULATION OF PSM CONVERTER UNDER DCM A PSM converter is said to be operating in discontinuous conduction mode if inductor current reaches zero and stays at zero level for a brief period of time. Since a PSM converter operates with a constant duty 75 cycle if the condition for DCM is satisfied then in every cycle during the charging period the inductor current would start from zero. Due to the same reason the inductor current would remain zero throughout the skipping period. This results in third circuit configuration alone being considered during skipping period while modelling the converter operating under DCM. 3.2.1 Modelling To facilitate analysis and design of converters in various applications reduced-order models and full-order models for DCM PWM converters were reported (Cuk and Middlebrook 1977, Maksimovic and Cuk 1991, Vorperian 1990). In former, the inductor current does not appear as a state variable due to the fact that it becomes zero every cycle and the model predicts the low frequency behaviour correctly but the absence of inductor current is disadvantageous in certain control techniques, which rely on inductor current magnitude. In the latter the inductor current is retained and they are reported to be having improved accuracy over reduced-order models (Jian Sun 2001). In buck converters under discontinuous conduction mode of operation, there is an additional time interval in each cycle during which inductor current is clamped to zero. The converter is assumed to work in DCM and modeled using State Space Averaging technique (Luo Ping et al 2006, Middlebrook and Cuk 1977) with inductor current included. Let for p cycles the clock pulses are applied and for q cycles the pulses are skipped for a particular load resistance R and input voltage Vin. The duration pT is known as charging period and the duration qT is known as skipping period. During the charging period, in each cycle the switch is ON for duration equal to D1T and OFF for duration equal 76 to (1-D1) T. During this period inductor current drops to zero in D2T and hence the current is zero during the remaining (1-(D1+D2)) T. During the skipping period the switch is OFF throughout as the pulses are not applied and skipped. The state space equations, assuming discontinuous conduction mode, are obtained as: During charging period, x A1 x y C1x x A2 x y C2 x x A3 x y C3 x B1vin 0 t D1T ( 3.8) B2vin D1T t D1 D2 T (3.9) B3vin D1 D2 T t T (3.10) During skipping period, x A3 x B3 vin y C3 x 0 t T (3.11) where, 0 A1 A3 A2 A 0 0 1 RC 0 1 C 1 L 1 RC (3.12) (3.13) 77 x y iL vC , (3.14) v0 , (3.15) 1 L , 0 B1 (3.16) B2 B3 0 C1 C2 C3 (3.17) (3.18) 0 1 After State Space Averaging, x pA D1 D2 x pA3 D3 x qA3 x p q pD1 Bvin (3.19) Defining Modulation Factor M, M fa f 1 fa f (3.20) p (3.21) p q where, fa f Actual frequency of switch Clock frequency Then Equation (3.19) becomes x 1 M A D1 D2 A3 D3 MA3 x 1 M D1 Bvin (3.22) 78 M, the modulation factor is a measure of the number of skipping. When vin goes higher for the same V0 with constant D, M increases increasing the number of skipped pulses to maintain the voltage. Similarly when load decreases M increases decreasing the number of switching. M, the modulation factor, can be obtained from 2V02 fL Vin Vin V0 D12 R (1 M ) (3.23) Modulation Factor plotted as a function of Vin is shown in Figure 3.3. As voltage increases M increases indicating increased skipping of pulses. Modulation Factor plotted as a function of RL is shown in Figure 3.4. As load resistance increases M increases to signify regulation through pulse skipping. M Vs Vin 1.2 1 0.8 0.6 0.4 0.2 0 0 5 10 15 20 25 30 35 Vin in Volts Figure 3.3 Modulation factor Vs Vin (Increased skipping with Vin) 79 M Vs RL 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 0 5 10 15 20 25 30 35 RL in Ohms Figure 3.4 Modulation factor Vs RL( Increased skipping with RL) The averaged model including equivalent series resistance is obtained as below: The state space equations, assuming discontinuous conduction mode with rC<<R are obtained as: During charging period, x A1 x B1u y C1 x x A2 x B2u y C2 x x A3 x B3u y C3 x 0 t D1T D1T t D1 D2 T D1 (3.24) D2 T t T (3.25) (3.26) 80 During skipping period, x A3 x B3u y C3 x 0 t T (3.27) where, A1 A2 A3 0 x iL vC u y B1 , (3.31) v0 iin 0 B2 0 0 0 (3.28) (3.30) i0 1 L 1 L , 0 (3.29) vin 0 B3 A rC L 1 C (3.32) rC L , 1 C (3.33) rC L 1 C (3.34) 0 1 C (3.35) 81 C1 C2 C3 x rC 1 1 0 rC 1 0 0 3.2.2 (3.37) 0 1 (3.38) 0 0 1 M A D1 y (3.36) D2 x rC D1 D2 D1 1 M B1 B3 D1 B2 B3 D2 B3 u 1 x 0 (3.39) (3.40) Simulation For simulation of the PSM DC-DC buck converter under DCM the following parameters in Table 3.1 are considered. The load and inductance values considered result in discontinuous conduction within each cycle. Table 3.1 Parameters considered for PSM DC/DC converter under DCM Parameter vin V0 L 12 H C f R (minimum) D1 Value 12V to 20V 5V 470 F 40KHz. 10 Ohms 0.2 Simulation of the model of the converter under DCM is carried out with MATLAB and the circuit simulation carried out with PSIM. Simulation results for a load current of 500mA are shown in Figure 3.5. Pulses applied to 82 the switch are shown along with clock pulses to indicate the pulses skipped. Inductor current is discontinuous. Vin =12V and V0 is maintained at 5V. The load current is increased from 250mA to 500mA and the output voltage response is shown in Figure 3.6. It is observed that the inductor current and hence the switch current is high but does not change with increase in load current. Here it remains at 3A at both the loads. The number of pulses applied increases thus decreasing the number of pulses skipped. Load Current V0 Io(A) 6 4 2 0 Pulses Applied 0.8 0.4 IL (A) 0 Ind C urrent 3 2 1 0 C LK 0.8 0.4 0 0.0018 0.002 0.0022 0.0024 Time (s) Time (S) Load current, applied pulses, inductor current and clock 5.0 2 vo(V) 5.0 1 5 4.9 9 4.9 8 4.9 7 4.9 6 3 IL (A) 2 .5 2 1 .5 1 0 .5 0 0 .40 15 0.4 0 2 0.4 0 2 5 0 .4 0 3 T i m e (s) Output voltage and Inductor current waveforms Figure 3.5 PSM Buck converter waveforms for a load of 500mA 83 Output Voltage in V Load current in A Load Current 0.55 0.5 0.45 0.4 0.35 0.3 0.25 0.2 V0 5.2 5.1 5 4.9 4.8 0.0099 0.01 Time (s) 0.0101 (a) vo(V) 5.02 5 4.98 IL (A) 3 2.5 2 1.5 1 0.5 0 0.4015 0.402 0.4025 0.403 Time (S) (b) Figure 3.6 Step increase in load and response of output voltage. Load increased from 250mA to 500mA. (a) Load current and output voltage (b) Output voltage and inductor current Output voltage ripple at 250mA is less than 1% at 0.88% and at 500mA is slightly higher but less than 1% at 0.97%. At 1A the regulation is poor and the voltage falls to 4.4V. 84 v in(V) 20 18 16 14 12 vo(V) 5.12 [0.411044 , 5.10972] 5.1 5.08 5.06 5.04 5.02 [0.409586 , 5.02012] 5 4.98 [0.409525 , 4.9719] [0.411174 , 4.97087] 4.96 0.41 0.411 0.412 Time (S) Figure 3.7 Step increase in load and response of output voltage The input voltage is increased from 12 V to 20 V and the load is maintained constant. The ripple at an input of 12V is about 0.97% and at 20V it is about 2.5%. The inductor peak current and hence the device current is 2.5A which is around 5 times the load current. It is found that with selection of a constant D1 the ripple in DCM PSM Buck converter can be maintained low but increase in load may result in regulation failure. This is due to the fact that the reservoir capacitor would discharge to a larger extent than the charge it received in each cycle. Increased pulse width would result in poor ripple performance at lighter loads. Hence constant pulse width may regulate over a short range without considerable deterioration in performance. 85 3.3 MODELLING AND SIMULATION OF PSM CONVERTER UNDER FORCED DCM When conditions of a PSM converter do not favour discontinuous conduction the inductor current is nonzero in the beginning of each switching cycle during charging period. The inductor current reaches a peak value and the skipping period begins after which the current drops. Now, if the number of cycles that are skipped, are adequate then the current reaches zero and may remain zero for a brief period causing discontinuity in inductor current. Since in each switching cycle the current is continuous this mode may be classified under CCM and due to discontinuity forced in inductor current it can be treated as a converter under DCM. 3.3.1 Modelling Converter under Forced DCM Consider a converter controlled with PSM controller that applies pulses over duration of time and skips pulses over another duration alternately based on the result of a condition that involves the actual and desired output voltages. Let the duration of charging period equal pT where p is the number of cycles applied, and the duration of skipping period equal (q + r) T where q is the number of cycles over which the inductor current is non zero and r is the number of cycles over which the inductor current is zero. The inductor current waveform in Figure 3.8 includes charging cycles and skipping cycle long enough for the inductor to dry out so that there is current discontinuity. 86 I nd Current in A 0.5 IL(A) 0.4 0.3 0.2 0.1 0 Charging Skipping Pulse Amplitude (V) V 10 1 0.8 0.6 0.4 0.2 0 0.4951 0.49 52 0.4953 Time(S) Figure 3.8 Inductor current and applied pulses rT is a prolonged duration of time that is included to make inductor current zero for a brief period of time to bring in discontinuous conduction. It is to be noted that during the charging period the converter is under continuous conduction since the condition for discontinuous conduction is not satisfied. The state space equations, assuming discontinuous conduction with continuous conduction during charging period, are obtained as given below: During charging period, for p cycles x A1x y C1 x x A2 x y C2 x B1u B2u 0 t D1T D1T t T (3.41) (3.42) During skipping period, for q cycles with nonzero inductor current 87 x A2 x y C2 x B2u 0 t T (3.43) During skipping period, for r cycles with zero inductor current x A3 x y C3 x B3u 0 t T (3.44) where, 0 A1 A2 0 A3 x 0 A 1 C 1 L 1 RC 0 1 RC (3.45) (3.46) iL (3.47) vC u vin (3.48) y v0 (3.49) B1 1 L 0 B2 B3 0 C1 C2 C3 (3.50) (3.51) C 0 1 (3.52) 88 State space equations are averaged over switching period: From Equations (3.41) and (3.42) for p cycles x Ax y Cx D1 B1u (3.53) From Equation (3.43) for q cycles x Ax y Cx (3.54) From Equation (3.44) for r cycles x A3 x y Cx (3.55) This can be realised with hysteretic current limit along with PSM control. Number of pulses can be calculated from the rise time for inductor current to rise to peak value set for IL. Valley current is set to be zero making the average inductor current to equal load current. Typical inductor current waveform is shown in Figure 3.9. Here the upper current limit or threshold was set to be 2A but there is overshoot due to delay in circuit. Inductor Current 2.5 Current Limit 2 1.5 1 0.5 0 0.4015 0.402 0.4025 0.403 Time (s) Figure 3.9 Typical current waveform in FDCM PSM converter 89 The PSIM model for PSM buck converter under forced DCM is shown below in Figure 3.9. There are three sub circuits. Two sub circuits are to limit voltage and current respectively and the third one is the skip logic. The current limit circuit accepts inductor current as the input and produces output HIGH when the current crosses a preset value in a way almost similar to the one proposed by Dokania (2004) in which a device current sensor was employed to sense the peak current. This output resets an SR flip flop to give an output LOW to SKIP Logic which in turn would block pulses to the switch. This results in start of the skipping cycle. The second subcircuit accepts input from both the output voltage sensor and inductor current sensor. When inductor current reaches zero AND if voltage is below the reference value the circuit produces an out put HIGH that set the SR flip flop which in turn would make the SKIP Logic to release pulses resulting in start of the charging cycle. Thus in every cycle it is ensured that the inductor dries out resulting in discontinuous conduction. FDCM with Hysteretic current limit L1 A A C1 Resr RL T2 Q R Q T2 skip logic If iL>Ipeak S T2 If iL<Iv & v0<Vref Figure 3.10 Forced discontinuous conduction in PSM buck converter 90 Number of pulses applied till the inductor current reaches Ipeak equals p and the number of pulses skipped till the current reaches zero equals q and the pulses will be skipped till the voltage is less than Vref. 3.4 OBSERVATIONS WITH VARIATION IN INPUT VOLTAGE Following parameters are considered for simulation that is carried out with PSIM. Parameters correspond to continuous conduction mode. Table 3.2 Parameters considered for simulation of forced discontinuous conduction mode Parameter Value 12V to 20V 5V vin V0 L 156 H C 470 F 40KHz. 5 Ohms 0.6 f R (minimum) D1 Input Voltag e in V 20 18 16 14 12 10 Ou tput Voltage in V 5 .2 5.15 5 .1 5.05 5 4.95 4 .9 4.85 Ind Cu rrent i n A 2 .5 2 1 .5 1 0 .5 0 0 .403 2 0.4034 0.4036 0.4038 0 .4 04 0.4 042 0.4044 0 .4 046 Time (s) Figure 3.11 Waveforms of Vin, v0 and iL in PSM forced DCM discontinuous conduction with Ripple – 6% 91 Change in input voltage does not affect the ripple as observed and the output voltage is regulated over the input range. 3.5 BIFURCATION AND CHAOS IN PSM CONVERTER UNDER DCM When the converter operates under DCM the inductor current goes down to zero before the end of each switching cycle and the inductor is reset. The current rises from zero in each switching cycle and hence disturbances in the previous switching cycle do not have any effect on the next switching cycle (Middlebrook 1988 and Teuvo Suntio 2006). A simple buck converter having two independent storage elements is a second order system. Inductor current is zero at the start of each switching period when the converter operates in DCM. iL ( nT ) 0 n (3.56) where T is the switching period and n is an integer. Thus with the inductor current no longer a dynamic variable, the converter becomes a first-order system with the capacitor voltage serving as the only state variable. The dc-dc converter is operating in discontinuous conduction mode with operating frequency fixed and the switch and diode are assumed ideal, with fsw and T the switching frequency and time period, for a two-dimensional buck converter. The operating condition switches from S1 with switch ON to S2 with switch OFF and at the end to S3 after inductor is dried out once a clock cycle. Hence every cycle begins from S3 and the switch goes to ON state so that the operating condition switches to S1 or 92 remains in S3 depending on the constraint equation v(nT)>vref. It is also to be noted that the duty cycle is fixed and hence at the beginning of every cycle based on the constraint the next operating state is S1 or retaining the state as S3 the next pulse is skipped. The sampled data model of the converter with input constant operating in discontinuous conduction mode is a first-order iterative map given by: vn f vn , d n 1 (3.57) The discrete-time map for the converter is (Fang and Abed 1998) 2 vn d n Vin Vin vn vn 1 vn (3.58) where vn vc tn (3.59) T 1 CR 1 T 2 CR 2 (3.60) T2 2 LC (3.61) The constraint equation is dn 0 dn D1 if v nT if v nT (3.62) vref v ref (3.63) 93 The bifurcation diagram is as shown in Figures 3.12 and 3.13. Figure 3.12 Bifurcation diagram for PSM DC/DC buck converter under DCM Figure 3.13 Bifurcation diagram for PSM DC/DC buck converter under DCM-enlarged view 94 3.6 BIFURCATION AND CHAOS IN PSM DC-DC VMC –FDCM The input voltage is varied from 10V to 35V. There is bifurcation but the tendency to be chaotic is brought down every time the operating state becomes S3 with the state variable iL becomes zero. The system reduces to first order as the inductor is reset and hence the chaos does not set in as seen. In Figure 3.14 the number of charging pulses repeat making fa constant. In Figure 3.15 the waveforms of v0 and iL repeat in a 4-3 sequence as marked both indicating periodicity. Load Current in A Ind current in A Waveforms showing no chaos Input voltage is 12V and output voltage is 5V 2.5 2 1.5 1 0.5 0 Output Voltage in V 5.2 5.15 5.1 5.05 5 4.95 4.9 4.85 0.402 0.4025 0.403 0.4035 0.404 0.4045 Time (s) Figure 3.14 Inductor current and output voltage with Vin = 12V for PSM buck converter under forced DCM with Ripple – 6% Ind C urrent in A Loa d C urrent in A 3 2.5 2 1.5 1 0.5 0 Output Voltage in V W av efo rm s show ing no c haos Input Volatge is 35V a nd output voltage is 5V 5.4 5.3 5.2 5.1 5 4.9 0.40 1 0.40 2 0.403 0.404 Time (s) Figure 3.15 Inductor current and output voltage with Vin = 35V for PSM buck converter under forced DCM with Ripple – 6% 95 Phase plane trajectory between iL, the inductor current and vC the capacitor voltage is shown below in Figure 3.16 indicating no chaos at 12V. Ind Cu rre nt in A Phase Plane Trajectory PSM under Forced DCM iL Vs vC Vin = 12V 2 .5 2 1 .5 1 0 .5 iL becoming zero showing Discontinuous conduction 0 4.9 6 4.9 8 5 5 .0 2 5 .0 4 5 .06 5 .08 5 .1 vC Figure 3.16 Phase plane trajectory iL Vs vC showing discontinuous current and no Chaos at Vin = 12V for PSM converter under forced DCM Phase plane trajectory between iL, the inductor current and vC the capacitor voltage is shown below in Figure 3.17 indicating no chaos at 35V. vC Phase Plane trajectory for PSM under Forced DCM vC in V and iL in A 5.22 5.2 5.18 5.16 5.14 5.12 5.1 5.08 5.06 iL becoming zero showing discontinuous conduction 0 0.5 1 1.5 iL 2 2.5 3 Figure 3.17 Phase plane trajectory iL Vs vC showing discontinuous current and no Chaos at Vin = 35V for PSM converter under forced DCM 96 Ripple is at 6% due to high inductor current ripple with ESR not negligible. 3.7 CONCLUSION Since the inductor current becomes zero every cycle the order of the system reduces by one. In a typical CCM buck converter there are two poles and system may become unstable when feedback is applied whereas the DCM has one pole and the system is stable with feedback. A small inductor implies a larger ripple and perhaps a DCM operation. Device peak current is significantly higher. The system now reacts quicker since a smaller inductor offers less opposition to current changes. However, with change in load or supply voltage the ripple goes up or the converter fails to regulate if the duty cycle is inadequate. The ripple current being important, if high results in higher conduction losses due to resistive paths like RDS,on etc.: DCM operation brings larger conduction losses compared to CCM if operation is over a wide range. With a selection of a constant duty ratio, it is found that, the ripple in DCM PSM Buck converter can be maintained low at a particular load but would not regulate over the entire range and may result in regulation failure due to inadequate charge transfer per cycle. Adequate charge transfer is ensured in the case of forced DCM operation with hysteretic current control, but the output voltage ripple is slightly higher. Increased pulse width to ensure adequate charge transfer also results in poor ripple performance. This is due to the ESR of the capacitor considered being not negligible. Low ESR ceramic capacitors that are used for output filtering (John Betten and Dave Strasser 2002), result in lower ripple and offer a solution to minimisation of ripple in converters that are inherently stable.