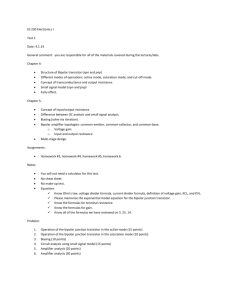

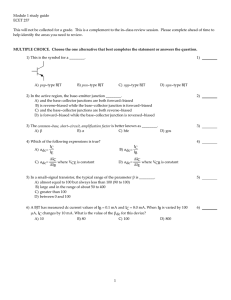

Bipolar Junction Transistor Models and Biasing

advertisement