Signal Flow Analysis of Feedback Circuits

advertisement

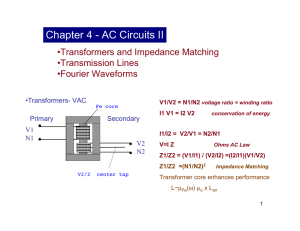

EE 536a Lecture Aid #5 Academic Year 2011--2012 Signal Flow Analysis Of Feedback Circuits Dr. John Choma, Professor Of Electrical Engineering Ming Hsieh Department of Electrical Engineering Powell Hall Of Engineering (PHE) Room #620 University of Southern California University Park; Mail Code: 0271 Los Angeles, California 90089-0271 (213) 740-4692 [Office] johnc@usc.edu [E-Mail] www.jcatsc.com [Course Notes] Overview Of Lecture Circuit Analysis Via Partitioning Null Parameter Forward Gain Return Ratio With Respect To Feedback Parameter Null Return Ratio With Respect To Feedback Parameter Gain Relationships Loop Gain And Null Loop Gain Open p And Closed Loop p Gain Generalized System Model Impedance Calculations Driving Point Input And Output Impedances Computational Efficiency And Insights Analytical Special Cases Controlling Feedback Variable Equal Eq al To Output O tp t Response Controlling Feedback Variable Equal To Branch Variable Controlling Feedback Variable Equal To Short Circuit Controlling C t lli F Feedback db k V Variable i bl E Equall T To C Capacitance it Example Calculations EE 536a Lecture Aid #5 Signal Flow 249 Circuit Partitioning PVk Zin Vc Linear Li Circuit Zs Vs Ic Vk By Superposition Zout Vo o os s oc c V A V Z I k By Substitution I PV c Zl V A V Z I k V A V Z PV k Vo Vs ks s kc k ks s I c Aks Z oc Aos 1 P Z kc Aos 1 PZ kc kc c PA V ks s 1 PZ kc Aos 0 Aos Comments Network Is Linear And Terminated In Known Source And Load Impedances Parameter P ((Here The Admittance Of A VCCS)) And The Branch In Which It Appears Are Partitioned From The Linear Circuit To Assess Its Impact On Circuit Performance Indices (Gain, I/O Impedances, etc.) Parameter P Is Termed Critical Feedback Parameter Of Circuit Under I Investigation ti ti Can Be Viewed As A Model Of Feedback From kth –To- cth Ports Other Critical Parameter Models Are Possible (e.g. CCCS, VCVS, etc.) EE 536a Lecture Aid #5 Signal Flow 250 Partitioning Parameter Definitions A P,Z ,Z v s A P,Z ,Z v s l l s kc 1 P Q Z ,Z r s l o A os V 1 P Q Z ,Z s s s l V Normalized Null Return Ratio Block Diagram Vo Ao 1 PQr Vs PQsVo s PQr Vo s r Signal Flow N ll Return Null R R Ratio i T P,Z ,Z PQs /Aos l Also K Al Known A As Loop Gain Stability Measure Aos Return Ratio T P,Z ,Z EE 536a Lecture Aid #5 Null Return Ratio & Return Ratio w/r To Parameter P Normalized Return Ratio Vs P,Z Z ,Z Z P Q Z ,Z Z Aks Z oc Aos 0 Tr P s l r s l A 1 P Z os kc A T P,Z ,Z P Q Z ,Z A V os os s s l s s l o V 1 PZ s l Transmission Zeros Measure Of Feedforward 251 Feedback Circuit Parameters Vs Vo A P,Z ,Z v s l Aol (s) f(s) v s A ( s ) A P,Z ,Z Open Loop Gain Feedback Factor A P,Z ,Z ol v s f ( s )A ( s ) PQ Z ,Z ol s s l l l Q 0 s ol A 1 P Q Z ,Z os r s l f(s) 1 P Q Z ,Z Z r s l o A os V 1 P Q Z ,Z s s s l A (s) A (s) ol l oll 1 f ( s )A ( s ) 1 T( s ) V PQ Z ,Z s s l A 1 PQ Q Z ,,Z os r s l T P,Z ,Z P Q Z ,Z r s l r s l Loop Gain T( s ) f ( s )Aol ( s ) PQs Z s ,Zl Ts P,Z s ,Zl Null Return Ratio Also Called Null Loop Gain Accounts For Feedback Subcircuit Loading At I/O Ports Accounts For I/O Feedforward Through Feedback Subcircuit Offers Clue For Stability Compensation With LHP Zeros EE 536a Lecture Aid #5 Signal Flow 252 Forward Gain Calculation PVk Zin Zs Vs Ic Vc Linear Circuit Null The Critical Parameter Zout Zino Vs Vo V Zl o A os V s Vk Output ResponseVo AosVs Z oc I c AosVs Zouto Linear Circuit Zs Vk Ic = 0 Vc Vo Zl 0 A Z Aos 1 P Z kc ks oc Aos Av P,Z s ,Zl 1 PZ kc Critical Parameter Set To Zero (Nulls Feedback From Controlling To Controlled 1 P Q Z ,Z Network Ports) V r s l A P,Z ,Z o A Gain Determined v s l os V 1 P Q Z ,Z s s s l E l i l B Exclusively By Aos A 0,Z ,Z v EE 536a Lecture Aid #5 s l Signal Flow A os 253 Normalized Return Ratio Zin Vc Vs Zout Zl Zs 0 Controlled Variable Replaced By Independent Source Vo V Linear Li Circuit Zl kc Vkc Controlling Variable Is Vk; Controlled Variable Is Ic = PVk Normalized Return V A V Z I Z I V k ks s kc c kc c kc A Z R ti Ratio Aos 1 P Z kc ks oc Aos 1 PZ kc Q Z ,Z EE 536a Lecture Aid #5 s l Zkc V Signal Flow k I c V 0 V kc I c V 0 Note s s Maintenance Of Controlled Variable Polarity Reversal Of Polarity Of Controlling Variable Parameter Null Independent Source (Voltage Becomes Short, Current Is Open) Av P,Z s ,Zl s Vk kc Q s I c V Vk Reverse Polarity Ic Vc Vo Linear Li Circuit Zs No Polarity Reversal Ic Null Source PVk 254 Normalized Null Return Ratio Zin Zs Vs Vc Ic Zout Vo Linear Circuit Zl Ic No P N Polarity l i Reversal Vc Untouched d Source PVk Vk Reverse Polarity y Vs Zs Controlled Variable Replaced By Independent Source Vo = 0 V Linear Circuit Zl V Vkc kc V A V Z I 0 V Z I A Source Constraint Controlling Variable Vk AksVs Z kc I c Aks Z oc I c Aos Z kc I c os s oc c s Vk Null Output o kc Q r I c oc c os Normalized Null Q Z ,Z Z A Z A V I V I r s l kc ks oc os k c V 0 kc c Return Ratio o Note: Source Signal g Is Not Set To Zero,, But Response Is Constrained Av P,Z s ,Zl To Zero With Source Signal Applied EE 536a Lecture Aid #5 Signal Flow Ak Z oc Aos 1 P Z kc ks Aos 1 PZ kc 255 Computational Summary PVk Zin Zs Vs Ic Vc Linear Circuit Vk Zout Av P,Z s ,Zl Vo Zl V 1 P Q Z ,Z A (s) r s l o ol Aos 1 P Q Z ,Z V 1 T( s ) s s s l Parameters Null Parameter Gain = Aos Normalized Return Ratio = Qs((•)) Normalized Null Return Ratio = Qr(•) Open Loop Gain = Aol (s) Loop Gain = T(s) Null Gain The Ratio Of Output -To- Input With Critical Parameter Null Normalized Return Ratio The Ratio Of The Negative Controlling Branch Variable -To- The Controlled Branch Variable With Input Null Normalized Null Return Ratio The Ratio Of The Negative Controlling Branch B hV Variable i bl -ToT The Th Controlled C t ll d Branch Variable With Output Null EE 536a Lecture Aid #5 Signal Flow 256 Shunt-Shunt (VCCS) Feedback Subcircuit Two o Port o t Feedback eedbac Subc Subcircuit cu t Model ode V y y y V y V Feedback Parameter Is P = y12 y P Feedforward Parameter Parameter Is y21 In Passive Subcircuits, y21 = y12 = P Even If y21 = y12, Zero Feedback Applies Only To Parameter y12 Parameter y21, Which May Numerically Equal P, Is Not Set To Zero c 11 12 k 21 c Vk 22 12 When Computing Aos And Other Null Parameter Performance Indices V Effectively Shunt-Shunt Feedback c Signal Flow Zout Vo Vs y21Vc Circcuit Zs Zl y22 EE 536a Lecture Aid #5 PVk Zin y11 Feedback Parameter Partitioning y11 Loads Controlled Feedback Port y22 Loads Controlled Feedback Port y21 Models Feedforward From cth To kth Network Port Null Feedback Parameter Performance Indices Are Resultantly Functions Of Feedback Subcircuit Model Parameters Lineear Vk 257 Series-Series (CCCS) Feedback Subcircuit Ic z z Feedback eedbac Subc Subcircuit cu t Model ode z I z I Feedback Parameter Is P = z12 V z P Feedforward Parameter Parameter Is z21 In Passive Subcircuits, z21 = z12 = P Even If z21 = z12, Zero Feedback Constraint Applies Only To z12 11 22 c 12 k 21 c 12 Ik Vk zc2 Zout Vo Zs z2 1Ic Circcuit Ic Zl z2 2 Signal Flow z11 EE 536a Lecture Aid #5 PIk Zin Lineear Effectively Series-Series Feedback Feedback Parameter Partitioning z11 Loads Controlled Feedback Port z22 And External Load zc2 Loads Controlled Feedback Port z21 Models Feedforward From cth To kth Network Port Null Feedback Parameter Performance Indices Are Resultantly Functions Of Feedback Subcircuit Model Parameters Parameter z21, Is Not Set To Zero When Computing Aos Same For Other Null Parameter Performance Indices Vs zc2 Ik 258 Series-Shunt (VCVS) Feedback Subcircuit Ic h Two-Port o o t Feedback eedbac Subc Subcircuit cu t Model ode V h V h I Feedback Parameter Is P = h12 h P Feedforward Parameter Parameter Is h21 In Passive Subcircuits, h21 = −h12 = −P Even If h21 = −h12, Zero Feedback Constraint Applies Only To h12 Ik 11 c 12 k 21 c 12 h22 Vk Parameter h21, Is Not Set To Zero When Computing Aos Same For Other Null Parameter Performance Indices Effectively Series-Shunt Feedback Feedback Parameter Partitioning h11 Loads Controlled Feedback Port h22 Loads Controlled Feedback Port h21 Models Feedforward From cth To kth Network Port Null Feedback Parameter Performance Indices Are Resultantly Functions Of Feedback Subcircuit Model Parameters Feedback Subcircuit Architecture Series Input Port Topology Shunt Output Port Topology Hence, “Series-Shunt” Nomenclature EE 536a Lecture Aid #5 Signal Flow 259 Shunt-Series (CCVS) Feedback Subcircuit Ic g Feedback eedbac Subc Subcircuit cu t Model ode g I g V Feedback Parameter Is P = g12 V g g P Feedforward Parameter Parameter Is g21 In Passive Subcircuits, g21 = −g12 = −P Even If g21 = −g12, Zero Feedback Constraint Applies Only To g12 22 c 11 12 k 21 c 12 Ik Vk zc2 Parameter g21, Is Not Set To Zero When Computing Aos Same For Other Null Parameter Performance Indices Effectively Series-Shunt Feedback Feedback Parameter Partitioning g11 Loads Controlled Feedback Port g22 And External Load Zc2 Loads Controlled Feedback Port g21 Models Feedforward From cth To kth Network Port Null Feedback Parameter Performance Indices Are Resultantly Functions Of Feedback Subcircuit Model Parameters Feedback Subcircuit Architecture Shunt Input Port Topology Series Output Port Topology Hence, “Shunt-Series” Nomenclature EE 536a Lecture Aid #5 Signal Flow 260 Input Impedance Computation PVk Zin Vx Ix Ic Vc Linear Circuit Vk 1 PQ ri Zin Zino 1 PQ Ix si V Q k si Ic Vx Vo Zl Ix 0 Z ino V I x x P 0 V k ri Ic Q Note: The Output Node Is Left Terminated In The Load Impedance And Is Never Open- Or Short-Circuited The Problem “Input” Input Is Applied Test Current Current, Ix “Output” Is Resultant Test Response Voltage, Vx Driving Point Input Impedance, Zin, Is Transfer Function, Vx /Ix, Whose Analytical Form Mirrors Gain Relationship Computations Zino Is Computed With Null Feedback Parameter (P = 0) Qsi Is Comp Computed ted With Null N ll “Inp “Input” t” (Ix = 0) Qri Is Computed With Null “Output” (Vx = 0) EE 536a Lecture Aid #5 Vx 0 Signal Flow 261 Input Impedance Parameters 0 Zino Vx Ix Ic = 0 Vc Z ino Zl Vx Ix = 0 Vkc EE 536a Lecture Aid #5 Qs Z s ,Zl 0 Vo Linear Circuit Ic Linear Circuit x 1 PQ ri Z Z in ino 1 P Q Ix si Vx Vc Zs x Ic Vk I Vo Linear Circuit Vc V V k kc I c Zl Vkc Vo Zl Qsi Signal Flow V kc Q ,Z s l I c Infinite Source Impedance Value Of Normalized Return Ratio 262 Input Impedance Parameters - Cont’d 0 Zino Vx Ix Ic = 0 Vc Z ino Zl 0 Ix Vkc EE 536a Lecture Aid #5 Qs Z s ,Z Zl 0 V Vo Linear Circuit Ic Linear Circuit x 1 PQ ri Z Z in ino 1 P Q Ix si Vx Vc Zs x Ic Vk I Vo Linear i ea Circuit Vc V kc I c Zl Vkc Vo Zl Qri Signal Flow V kc Q 0,Z s l I c Zero Source I Impedance d Value Of Normalized Return Ratio 263 Output Impedance Computation PVk Ic Vc Zs Linear Circuit Zout Vo Ix Vx 1 P Q Z ,0 0 s s x Z Z out outo I 1 P Q Z , x s s V Vk Computations Zouto Is Computed With Null Feedback Parameter (P = 0) Qs(Zs, ) Is Computed With Null “Input” (Ix = 0) Qs(Zs, 0) Is Computed With Null “Output” (Vx = 0) Comments Output p Impedance p Function Is Same Form As Input p Impedance p Both Input And Output Impedances Rely On Qs(•) EE 536a Lecture Aid #5 Signal Flow 264 Circuit Computational Summary PVk Zin Vc Vo Zl Zs EE 536a Lecture Aid #5 Vc Linear Circuit Vk Vo = AosVs Zino Ic = 0 1 P Q Z ,Z r s l Aos 1 P Q Z ,Z Vs s s l Vo 1 P Q 0, Z s l Zin P, Zl Zino 1 P Q , Z s l 1 P Q Z ,,0 s s Z P, Z Z out s outo 1 P Qs Z s , Vk 0 Vs Av P,Z s ,Zl Zout Linear Circuit Zs Vs Ic Ic Zouto Vc Zl Zs 0 Ic Linear Circuit Vkc Qs Ic Q Signal Flow Vc Vo Zl Zs Vs Linear Circuit Vo = 0 Zl Vkc Qr Ic Q 265 Controlling Variable = Output Response PVk = PVo Zin Zs Vc Vs Vo Zl r s l V Loop Gain T P,Z s ,Zl P Qs Z s ,Zl PAos Closed Loop Gain Ic V k Controlling = Output Variable Vk = Vo Normalized Null Return Ratio Is Zero o Ic Vo 0 0 Vo 0 v A P,Z P Z ,Z Z EE 536a Lecture Aid #5 1 P Qs Z s ,Zl Vs Aos Q Z ,Z Z Vo 1 P Q 0, Z s l Zin P, P Zl Zino 1 P Q , Z s l 1 P Q Z ,0 s s Z out P, P Z s Z outo 1 P Q Z , s s Vk Vo Av P P,Z Z s ,Z Zl Zout Linear Circuit Ic s Signal Flow l V o V s A os 1 T P,Z ,Z s l 266 Global Shunt-Shunt Feedback IInputt Signal Si l Source S Is Transformed To A Norton Equivalent Circuit Because Of Low Input Is I Impedance d Low Input Impedance Is Manifested By Addition Of Feedback F db k Current C t Source At Input Port Zin Zout Vo PVo Zs Linear Circuit Zl Ic Feedback Nature Global Because A Fraction Of The Output Response, Vo, Is Applied Directly Across The Input Port, Where Signal Is Is Incident Shunt-Shunt Shunt Shunt Global Feedback Feedback Is A Current In Shunt With Input Signal Current Source Feedback Is Proportional To Output Voltage Negative Feedback:Feedback Current Is Anti-Phase With Signal Current EE 536a Lecture Aid #5 Signal Flow 267 Global Feedback Null Analysis Zin Zout Z m P,Z s ,Zl Vo Is PVo Zs Linear Ci i Circuit Zl Ic Zs Vo=Z Zmo Is 0 Ic=0 Is EE 536a Lecture Aid #5 Linear Circuit 1 P Q 0, Z s l Zin P, Zl Zino 1 P Q , Z s l 1 P Q Z ,0 0 s s Z out P, Z s Z outo 1 P Q Z , s s Zino 1 P Q Z ,Z r s l Z mo 1 P Q Z ,Z I s s s l Vo Zouto Zl With Critical Parameter P Constrained To Zero, The P = 0, or “Null,” Values Of The Input Impedance (Zino ), The Output Impedance (Zouto ), And The Transimpedance (Zmo ) Are Computed Signal Flow 268 Zino Zs 0 Zl 0 Zs Ic Zl Return Ratio Analysis Null A l i Analysis Linear Circuit Vo Ic=0 Is Linear Circuit Zouto Vkc= =QsIc Vo=Z Zmo Is Global Feedback Return Ratio Procedure Source Signal Current Set To Zero; Output Node Left Untouched Controlled Generator Replaced By Independent Current, Ic Calculate Vkc /Ic = Vo /Ic Note Ic = PVo Polarity Is Reversed From Is Note Vkc Polarity Is Reversed From Vo (The Controlling Variable) Result V V Ic EE 536a Lecture Aid #5 s kc Q Z ,,Z Is 0 s l o Ic Signal Flow Z mo Z s ,,Zl Z mo Is 0 269 Global Null Return Ratio Ic Zl Is Zs Ic Linear Circuit Vo = 0 Zl Return Ratio A l i Analysis Vkc=Qr Ic Zs Vkc=QsIc 0 Linear Circuit Vo Null Return Ratio A l i Analysis Procedure Source Signal Left Untouched; Output Response Is Null Controlled Generator Replaced By Independent Current, Ic Calculate Vkc /Ic = Vo /Ic Note Ic = PVo Polarity Is Reversed From Is Note Vkc Polarity Is Reversed From Vo (The Controlling Variable) Result Vkc Ic EE 536a Lecture Aid #5 Qr Z s ,Z Zl V 0 o Signal Flow Vo Ic 0 V 0 o 270 Comments On Global Feedback Z Return etu Ratios at os Q Z ,Z Z Z ,Z Null Return Ratio Is Zero s s l mo s l Normalized Return Ratio Is P = 0 Value Of Transimpedance Gain Resultant Closed Loop Transfer Relationship m P,Z s ,Zl 1 P Q Z ,Z r s l Z mo Is 1 P Qs Z s ,Zl Vo Note: Z mo 0,Zl Z mo Z s ,0 0 Zs = 0 Short Circuits Input Port Zl = 0 Short Circuits Output Port Resultant Impedances Z P Z P, in l EE 536a Lecture Aid #5 Z s ,Zl 1 P Qs Z s ,Zl Z mo Z s ,Zl 1 P Z mo Z s ,Zl Z mo Very Low I/O Impedances 1 P Q 0, Z Z s l ino Z ino 1 P Q , Z 1 PZ , Z s l mo l 1 P Q Z ,0 s s Z P Z Z P, out s outo 1 PQ Z , s s Z 1 PZ Signal Flow outo mo Zs , Z 1 PZ ino mo Z s , Zl Z 1 PZ outo mo Z s , Zl 271 Critical Parameter = Branch Admittance Zin Zs Yc Vc YcVc Ic Linear Li Circuit Zout Zin Vo Zl Zs Vs Vc Ic Linear Li Circuit Zout Vo Zl Vs Branch Admittance Controlled Current Variable Is Ic Controlling Voltage Variable Is Voltage Vc Across Admittance Yc Branch B h Ad Admittance itt Yc Is I Equivalent E i l tT To Controlled C t ll d C Currentt S Source, Ic = YcVc Critical Parameter Branch B h Ad Admittance i Yc Null Gain Computed With Branch Open Circuited (Yc = 0) EE 536a Lecture Aid #5 Signal Flow 272 0 Zino Zs Vc Ic = 0 Vo = AosVs Branch Admittance Parameters ZT Zouto Linear Li Circuit Vkc Zl Vs Null Gain Vo Linear Li Circuit Zs Zl Vs Ic Aos Vo Vs I 0 c Vo Vs Y 0 c Qs Z s ,Zl V kc ZT Z s ,Zl Return Ic Vs 0 Ratios ZT Is Conventional Thévenin V ZTO Z s ,Zl Qr Z s ,Zl kc Impedance p Seen By y Yc ((Vs = 0)) Ic Vo 0 ZTO Is “Null Thévenin Impedance” Impedance Seen By Yc With Vo = 0 EE 536a Lecture Aid #5 Signal Flow 273 Branch Admittance Partitioning ZT (Vs = 0) Zin ZTO (Vo = 0) Zout Yc Vc Vo Linear Circuit Zs Zl Vs Voltage Gain c A Y ,Z ,Z v s l 1 Y Z 0,Z c T l Zino 1 Y Z ,Z c T l Input Impedance Zin Yc ,Zl O t t Impedance Output I d 1 Y Z Z ,0 c T s Z Y ,Z Z Z out c s outo 1 Y Z Z , c T s EE 536a Lecture Aid #5 Signal Flow 1 Y Z Z ,Z Z c TO s l A os Vs 1 Yc ZT Z s ,Zl Vo 274 Branch Short Circuit ZT (Vs = 0) Zin Zs Ic Vc ZTO (Vo = 0) Zout ZT (Vs = 0) Zin Zl Input Impedance O t t Impedance Output I d EE 536a Lecture Aid #5 Vo Zl Vs Voltage Gain Linear inea Circuit Zs Vs Vc Vo Linear inea Circuit ZTO (Vo = 0) Zout Yc = Z Z ,Z TO s l A ,Z ,Z o A v s l os V Z Z ,Z Compute A , Z , & s T s l os ino Zouto With Ic = 0, Z 0,Z Which Is Tantamount l Z ,Z Z Z T in l ino To Open Circuiting Z ,Z l T The Critical ShortCircuited Branch Z Z ,0 Z out ,Z Z s Z outo T s Z Z , T s V Signal Flow 275 Branch Capacitance Branch a c Admittance d tta ce Yc = sC Normalized Return Ratios Are Thévenin Impedances p Seen By y Capacitance Null Performance Requires Open Circuited Capacitance p (Zero Frequency Conditions) C I c ZT ((Vs = 0)) Zin Vc ZTO ((Vo = 0)) Zout Vo Linear Circuit Zs Zl Vs Performance Memoryless System 1 sCZ CZ Z ,Z Z Vo TO s l A sC,Z ,Z A Linear Network, Source v s l os Vs 1 sCZ Z ,Z T s l Impedance, Load Impedance Contains No L L’s s Or C C’s s 1 sCZ CZT 00,Z Zl Zin sC ,Zl Zino Time Constant Of Pole ,Z l 1 sCZ Z ,0 0 Time Ti Constant C t t Of Zero Z T s Z sC ,Z Z s outo z CZTO Z s ,Zl CRTO Rs ,Rl out 1 sCZT Z s , p CZT Z s ,Zl CRT Rs ,Rl EE 536a Lecture Aid #5 Signal Flow 1 sCZ T 276 Critical Parameter: CCVS Critical C iti l Parameter P t Transimpedance Of A Current Controlled Voltage Source (CCVS) Parameter P t P In I Ohms Oh Zin Performance Characteristics Equations Always Of Same Form Relationships: A P,Z ,Z v s Zin P, Zl l 1 P Q Z ,Z r s l o A os V 1 P Qs Z s ,Z Zl s V 1 P Q 0, Z s l Zino 1 P Q , Z s l Zs PIk Ic Vc Linear Circuit Zout Vo Zl V s Ik 1 P Q Z ,0 s s Z out P, Z s Z outo 1 P Q Z , s s EE 536a Lecture Aid #5 Signal Flow 277 Procedure Replace CCVS By Voltage Of Zero Value (Short Circuit) Leave Signal g Source,, Vs, Source Impedance, Zs, And Load Impedance, Zl, Untouched Compute p Transfer Function (Gain), Aos Input Impedance, Zino Output Impedance, Zouto EE 536a Lecture Aid #5 Signal Flow Zino Zs Vs 0 Ic Vc Linear Circuit Vo = Aos Vs CCVS: Null Parameters Zouto Zl Ik 278 CCVS: Return Ratio Vc Ic Vc Zs 0 Vc Ic Vc Vo Linear Li Circuit Zl Zs Vs Ikc = Qs Vc Return Ratio Signal Source Is Null Output Node Untouched Ikc = Qr Vc Q Z ,Z r s l Qs Z s ,Zl I kc Vc I kc Null Return Ratio Output Response Is Null Signal Source Left Untouched NOTE: Ikc Polarity Reversed From That Of Original Ik Signal Flow Zl Ikc EE 536a Lecture Aid #5 0 Linear Li Circuit Ikc Vs 0 V c V 0 o 279 Critical Parameter: CCCS PIk Critical C iti l Parameter P t Current Gain Of A Current Controlled Current Source (CCCS) Parameter P t P Is I Dimensionless Di i l Performance Characteristics Equations Always Of Same Form Relationships: A P,Z ,Z v Z in s P, Zl l 1 P Q Z ,Z V r s l o A os V 1 P Q Z ,Z Z s s s l 1 P Q 0, Z s l Z ino 1 P Q , Z s l Zin Zs Vs Vc Ic Linear Circuit Zout Vo Zl Ik 1 P Q Z ,0 s s Z P, Z Z out s outo 1 PQ Z , s s EE 536a Lecture Aid #5 Signal Flow 280 CCCS: Null Parameters PIk Procedure ocedu e Replace CCCS By Current Of Zero Value (Open Circuit) Leave Vs, Zs, And Zl, Untouched 0 Zino Zs Vs Vc Ic Vo = Aos Vs Zin Zs Zouto Vs Vc Ic Linear Circuit Zout Vo Zl Ik Linear Circuit Zl Ik Compute Transfer Function (Gain), Aos Input Impedance Impedance, Zino Output Impedance, Zouto EE 536a Lecture Aid #5 Signal Flow 281 CCCS: Return Ratios Ic Vc Zs 0 Ic Ic Vc Vo Linear Li Circuit Zl Zs Return Ratio Signal Source Is Null Output Node Untouched Qr Z s ,Zl Qs Z s ,Zl I kc I c V 0 s I kc I c V 0 o Null Return Ratio Output Response Is Null Signal Source Left Untouched NOTE: Ikc Polarity Reversed From That Of Original Ik Signal Flow Zl Ikc = Qr Ic EE 536a Lecture Aid #5 0 Ikc Vs Ikc = Qs Ic Linear Li Circuit Ikc Ic 282 Example: CMOS Feedback Amplifier MP Vbias Vo Rg MN Vs Rout Rf Rs Rf Rs Rin Rout Rin Vs Vdd V Vos Rg gmnV ron rop Rl Rl Low Frequency L F Small Signal Model Vgg Schematic Vss Diagram Voltages Vgg, Vss, And Vdd Can Be Replaced By Short Circuit To Ground Feedback Feedback Element Is Resistance Rf Or Equivalently, Conductance Gf Choose C C Critical Parameter P To Be Gf = 1/R 1/ f Note P = 0 Corresponds To Removal Of Feedback Resistance Focus Low Signal Frequencies Biasing Is In Saturation (Linear) Regimes For MN & MP EE 536a Lecture Aid #5 Signal Flow 283 CMOS Feedback Null Parameters Rino Routo Rs Vs V Vos gmnV Rg ron rop Rl R R g g Null Gain V g V Vos g mn ron rop Rl r R mn o l R R s R R s g s s g R Vos g g mn ro Rl Aos R R Vs ro ron rop s g I/O Null Resistances Rino Rg Routo ron rop ro EE 536a Lecture Aid #5 Signal Flow 284 CMOS Feedback Amplifier Return Ratio GfVc Set Signal Source To Zero Vc Ic Rs 0 Replace Feedback Conductance By Independent Current Source V ro Vos V Rg kck gmnV ron Analysis V I R R I g R R I r R c kc c g s mn g s c o l Return Ratio With Respect To Conductance Gf Thévenin Resistance “Seen” By Gf Result V Qs Z s ,Zl EE 536a Lecture Aid #5 kc Ic Vs 0 rop Rl ro Rl 1 g mn ro Rl Rg Rs Signal Flow 285 CMOS Feedback Amplifier Null Return Ratio GfVc Signal Source Untouched Replace Feedback Conductance By Independent Current Source Vc Vs Vos = 0 V Rg kc V ro Ic Rs gmnV ron rop Rl Vkc V Vos V I c g mnV Analysis Null Return Ratio With Respect To Conductance Gf Null Thévenin Resistance “Seen” By Gf Result V 1 Qr Z s ,Zl EE 536a Lecture Aid #5 Constrain Response To Zero kc Ic Vos 0 Signal Flow g mn 286 CMOS Feedback Amplifier Results General Ge e a Voltage o tage Gain Ga S Specific ifi Voltage V lt Gain G i Result R lt A R ,R ,R v f s l Av P,Z s ,Zl 1 P Q Z ,Z r s l Aos 1 P Q Z ,Z Vs s s l Vo 1 1 R g R g mn f r R g mn o l R R g r R 1 g r R R R s o l mn o l g s 1 Rf Approximate Voltage Gain Result Typically, Typically gmn(ro||Rl) Is Large (Requires Large Rl) Assume gmnRf >> 1 (States That Rf Cannot Be Too Large) Av R f ,R , s ,R , l EE 536a Lecture Aid #5 Vos Vs Rf Rs Signal Flow 287 CMOS Feedback Amplifier Results - Cont’d Generalized Ge e a ed Input put Impedance peda ce Pertinent Return Ratio Results Zin P, Zl s s l ro Rl 1 gmn ro Rl Rg Q 0,Z r R s l o l Q ,Z r R 1 g r R R s l o l mn o l g Q Z ,Z Specific Input Impedance Results For Large Rg Rin R f , Rl EE 536a Lecture Aid #5 in R f ro Rl R , R f 1 g mn ro Rl l R s R 1 P Q 0, Z s l Zino 1 P Q , Z s l r R o l 1 R f R g r R 1 g r R R mn o l g 1 o l R f R f Rl 1 g mn Rl Signal Flow 288 CMOS Feedback Amplifier Results - Cont’d 1 P Q Z ,0 s s Z out P, Z s Z outo Pertinent Return Ratio Results 1 P Q Z , s s Q Z ,Z r R 1 g r R R R s s l o l mn o l g s Q Z ,0 R R s s g s Generalized Ge e a ed Output Impedance peda ce Q Z , r 1 g r R R s s o mn o g s R R g s 1 R f For Large ro R R ,R r out f s o r 1 g r R R mn o g s 1 o R f R R R R f Rs f g s Rout R f , Rs 1 g R 1 g mn Rg Rs mn s Specific Output Impedance Results EE 536a Lecture Aid #5 Signal Flow 289 Match Terminated Gain I/O /O Resistances es sta ces R f ro Rl R f Rl Rin Assume ro >> Rl & Rg >> Rs 1 g mn Rl 1 g mn ro Rl Let Rs = Rl R Then Rin = Rout R f Rg Rs R R f s Design For Rin = Rout = R R out Requires Rf = gmnR2 1 g mn Rs 1 g mn Rg Rs Match Terminated Design Achieves A hi I/O Port P t Matching, M t hi Which Whi h Is I Useful U f l At RF Wh Where Si Signall P Power Is Scarce Facilitates High Power Gain Via Cascade Of Stages Resultant Gain (High gmn) 1 1 R g R g mn f Av g mn ro Rl R R r R 1 g r R R R s g o l mn o l g s 1 R f A v EE 536a Lecture Aid #5 g mn R1 2 Signal Flow 290 Match Terminated Schematic Diagram Gain A v V os V s g mn Vbias R1 R R 2 gmnR 2 Vo R Resistance R i t Rg Can C B Be S Supplanted l t d By Current Sink Vs Match Terminated Resistances Facilitate Network Cascades With Vgg Negligible Interstage Loading (See Next Slide) EE 536a Lecture Aid #5 Vdd MP Signal Flow Rg Rg >> R R << ro MN R V Vss 291 Match Terminated Cascade Concept R Vs R Gain: Av = Vos/Vs Vo Match Terminated Amplifier R Gain: Vos/Vs = Av3 R R Match Terminated Amplifier Vs R Match Terminated Amplifier R R Vo Match Terminated Amplifier R R R R Terminations Single Stage: Rs = Rin = Rout = Rl R Cascade: For All Three Stages, Rs = Rin = Rout = Rl R Comments Loading Effects On Each Stage Effectively Eliminated Reminiscent Of Transmission Line Terminated In Its Characteristic Impedance Results In Maximum Power Transfer At All I/O Ports EE 536a Lecture Aid #5 Signal Flow 292 CMOS Feedback Alternative Analysis Amplifier p e Schematic Diagram +Vdd Signal Schematic Diagram MP MP Vbias I1 Rs Rout Rf Vo I2 I1s Vi Rl Rg Vgg Rl Vs Feedback Branch Model f I G1 V V I 2s f Vos V is G V 2s MN Rs Rg 1s 1s Vos Vis MN II I2s Rin Vs Rf 1 G V V Vos G f Vis Vos is f is os R R EE 536a Lecture Aid #5 f os is f os V is Vis I1s Rf Signal Flow Vis I1s Rf I2s Vos Gf Vos Gf Vis I2s Vos Rf 293 Alternative Signal Schematic Diagram Si Signal l Schematic S h ti Observations Feedback Branch R l Replaced dB By T Two Port Equivalent Circuit I Reveals Global MP s Feedback Branch Rin Vis I1s I2s MN Rs Vos Rg Rf Gf Vos Rout Gf Vis Rf Rl Feedback As GfVos = Vos /Rf Reveals Feedforward As GfVis = Vis /Rf Reveals Input And Output Port Feedback Network Loading By Resistance Rf Signal Source Supplanted By Norton Equivalent Circuit Replacement Not Necessary But Done To Synergize With Feedback Feedback, Which Also Appears At Input Port As A (Dependent) Current Source Signal Current Given By Is = Vs /Rs Above Signal g Schematic Is Electrically y Identical To Signal g Schematic Shown On Previous Slide EE 536a Lecture Aid #5 Signal Flow 294 Analytical Strategy Rin S a Small Signal Model Rout Vis Is Rs Rg Vos Gf Vos (gmnGf )Vis Rf ro Rf Rl Parameters gmnVis And GfVis Combined Into A Single Voltage Controlled Current Source ro = ron||rop Is Net Channel Resistance At Output Port Only Low Signal Frequencies Are Addressed Analysis Procedure Determine Closed Loop Transimpedance Function Function, Zm (Gf, Rs, Rl ) Z m G f ,R ,R s l 1 G Q G , R , R f r f s l os Z os G ,R ,R mo f s l I V R 1 G f Qs G f , Rs , Rl s s s V V Determine Closed Loop Voltage Gain, Av (Gf, Rs, Rl ); I/O Impedances Z G ,R ,R A G ,R ,R v EE 536a Lecture Aid #5 f s l V os V s Signal Flow m f s l R s 295 Calculate Zmo(.), Rino, And Routo Set O Only y Feedback eedbac Parameter, a a ete , Gf , In GfVos To o Zero eo Rino Routo Vis Is Rs Rg Vos 0 (gmnGf )Vis Rf ro Rf Rl Zero Feedback Parameter Transimpedance Value Z mo G ,R ,R f s l V os I g s G V 0 mn G r R R R R R f o f l s g f f os Automatically Accounts Feedforward Effects Qr Is Zero Because Feedforward Already Accounted For Automatically Zero Feedback Parameter Value Of I/O Resistances R ino R outo EE 536a Lecture Aid #5 Signal Flow R g R r R o f f 296 Calculate Return Ratio Metrics Critical C t ca Parameter a a ete Is s Gf In GfVos Ge Generator e ato Vis Rs 0 Rg Rf (gmnGf )Vis Ic ro Analytical V Q G , R , R oskk g G Result s f s l mn f I c I 0 Result Is s Identical Z G To mo f Negative Of Open Loop Transimpedance Function Loop Gain (Return Ratio) T G ,R ,R s EE 536a Lecture Aid #5 f s l Z mo G R f ,R ,R s l f Signal Flow Rf Vosk Rl ro R f Rl Rs Rg R f ,R ,R s l r R o l R R R g G s g f mn f R f ro Rl 297 Calculate Normalized Null Return Ratio Same Calculation As Qs(.), But Response Is Null Vis Rs Is Rg Rf Ic (gmnGf )Vis ro Rf Vosk 0 Rl Analytical Result Q G , R , R Vosk 0 r f s l I Zero Result For c V 0 os Normalized Null Return Ratio Is Always True When Controlled Source Representing Feedback Is Proportional To Output Response Null Return Ratio T G , R , R r f s l EE 536a Lecture Aid #5 Signal Flow Q G ,R ,R r f R s l 0 f 298 Closed Loop Gain Performance I/O Transimpedance Z m G f ,R ,R s l os I s V os V s R I/O Voltage Gain A G ,R ,R v V f s l V os V s Z mo Z 1G Z G 1G Z s G mo f mo f ,R ,R s f mo G l f R s ,R ,R s l ,R ,R f s l G ,R ,R f s l R R f f R s A Approximations i ti Reflect R fl t Large L Loop L Gain G i Assumption A ti Requirement G Z G ,R ,R f mo f s l Z mo G f R ,R ,R s l 1 f Requirement Is Dubious For Single Stage Realization In Deep gy Submicron Technology EE 536a Lecture Aid #5 Signal Flow 299 Closed Loop I/O Resistances Input Resistance 1 T G ,0, R s f l R R iin ino i 1 Ts G f , , Rl O t t Resistance Output R i t 1 g g R f r R o l R R G mn f g f R f ro Rl 1 g 1 T G , R ,0 s f s R R out outo 1 Ts G f , Rs , R r R o f r o R R R G mn f r R s g f o f R R f 1 g l R mn l R R f 1 g s R mn s Approximations Invoked Large Channel Resistance, ro Large Shunt Input Port Resistance, Rg EE 536a Lecture Aid #5 Signal Flow 300 Comments On CMOS Feedback Analysis Analytical Strategy Traditional (Conductance Branch Feedback Element) Strategy Is Arguably Straightforward Alternative Two Port Strategy Is Arguably More Insightful Clearly Highlights Feedback Signal Clearly Highlights Feedforward Phenomenon Both Techniques q Give Essentially y The Same Results Design Match Terminated Design Is Certainly Possible Three Stage Realization Is More Practicable From The Perspective Of Achieving A Large Loop Gain Resistance Rg Can Be Implemented As Current Sink Renders Large g Rg A Reasonable Approximation pp Noise And Power Dissipation May Be Issues Large Channel Resistance, ro Desirable Approximation Questionable In Deep Submicron Devices EE 536a Lecture Aid #5 Signal Flow 301 Wilson Current Amplifier Vdd Circuit C cu t Sc Schematic e at c Diagram ag a Current Excitation IQ Is Applied Quiescent Input Current Is Is Applied Input Signal Current Current (IQ+Is) Commonly Supplied By PMOS Common Source Amplifier Since Signal Current, Ios, At Output Port Is Amplified Version Of Is, Wilson Unit Acts As A Cascode With Current Gain Rl Rout Rin Is + IQ Rs M1 V1 I1 M3 Io I2 V2 M2 Allows Resistance Rl To Be Reduced Diminishes Output p Port Capacitive p Time Constant Enhances Achievable 3-dB Bandwidth All Transistors Presumed To Operate In Saturation M2 Is Automatically Saturated I1 I Q I s Gate G Aspect Ratios Of M1 1 And M2 2 Are η-Times Io I 2 η That Of M3 Approximate Low Frequency Analysis I os A Current C tG Gain i IIs Essentially E ti ll R Ratio ti Of G Gate t Aspect A t is Is Ratios Very Predictable and Reproducible Current Gain EE 536a Lecture Aid #5 Signal Flow IQ I s η Is Is η 302 Wilson Current Amplifier − Specifics Circuit C cu t Sc Schematic e at c Diagram ag a Evaluate Amplifier Performance Via Signal Flow Current Gain, Gain Aisi = Ios /Is Input Resistance, Rin Output Resistance, Rout Assess Network Performance Vdd Rl Rout Rin Is + IQ Operational Assumptions All Transistors Are Biased In Saturation Regime Gate Aspect W1 L1 = W2 L2 I I Ratios W L 2 2 η = 2Q = oQ Transistor M2 W L I1Q I1Q 3 3 Connected As Diode Channel Resistance In M2 Can Be Ignored g Bulk Phenomenon In Transistor M1 Is Ignored Resultant Small Signal Parameters EE 536a Lecture Aid #5 Signal Flow Analysis Addendum Rs M1 V1 I1 M3 Io I2 V2 M2 g m r o 2K W L I n V V λ dsQ I dQ V dsatQ dQ g m1 g m2 ηg m3 ro1 ro2 ro3 η 303 Wilson Feedback Subcircuit M3-M2 3 Subcircuit Subc cu t Circuit Analysis g V I1s 1s m3 I 2s r g m2 o3 I g 1 V2s 2s ; m3 g m2 g m2 η V1s I1s V1s V2s I1s I2s gm3V2s ro3 1 gm2 I2s M3 M2 V1s V I I1s 1s 2s r η I1s I2s gm3I2s gm2 o3 V2s ro3 1 gm2 Feedback Current-Controlled I I V Current Feedback (Parameter P = 1/η) I 1 r Mirroring Presumes Drain Drain-Source Source Biasing g Voltages Of M2 And M3 Are Nominally The Same To Offset Channel Length Modulation Phenomena Between These Two Transistors Note gm2 /gm3 ≈ η = 1/P g 2K W L I 1s 2s 1s 2s V2s V2s o3 3 m2 m EE 536a Lecture Aid #5 Signal Flow n dQ 304 Wilson Small Signal Model Model ode Low Frequencies No Threshold Modulation Channel Length Modulation Ignored In Transistor M2 Vdd Rl Rout Rin M1 V1s I1s Is I2s V2s I2s Rs 1 gm2 ro33 Original Topology Ios Vdd Rout Rl Rout Is + IQ Rin EE 536a Lecture Aid #5 Rs M1 V1 I1 M3 V2 M2 Io Rin gm1Va ro1 Rl Va I2 I1s Is Rs Signal Flow Ios ro3 1 gm2 I2s Ios Ios 305 Feedback In The Wilson Amplifier Small S a S Signal g a Model ode Feedback Consists Of M2-M3 Subcircuit Feedback Is Global Assumes Form Of Rout Rin gm1Va ro1 Rl Va I1s Ios Current-Controlled ro3 Is Rs Current Feedback, Ios /η Feedback Factor Is Approximately 1/η (Within Previously Stated Assumptions) Feedback Loading 1 gm2 I2s Ios Ios Slight Load At Amplifier Input port In Amount Of Channel Resistance go3 Load At Amplifier Source Port In Amount Of Conductance gm2 Comments Low Input Impedance Is Likely Because Of Input Port Loading By Ios /η High Output Impedance Likely Because Feedback Is Activated By Output Port Source Degeneration Closed Loop Gain Of Roughly Ios /Is = n If Loop Gain Is Large EE 536a Lecture Aid #5 Signal Flow Analysis Addendum 306 Null Metrics For Wilson Amplifier Routo Circuit C cu t Model ode Recall g m1 g m2 ηg m3 ro1 ro2 ro3 η 1 P Null Rino ro3 ηro1 η Input Resistance, Rino I Null Current Gain, Aio No N Ph Phase IInversion i gm1 = gm2 I ro1 = ro2 Aio os Is Rino s 1/ η 0 gm1Va Rl Va I1s Rs 0 1 gm2 ro3 Ios g m1ro1 Rs ro3 Rl 1 g m1 r g m2 o1 Comments Large Null Input And Output Resistances 1 Potentially Large Null R r 1 g r m1 o1 outo o1 Current Gain g m2 EE 536a Lecture Aid #5 ro1 Signal Flow Analysis Addendum Ios g m1 Rs ro3 2 g m1 Rs ηro1 2 ro1 ro2 2r 2 o1 307 Normalized Loop And Null Loop Gains Routo Models Normalized Loop Gain I Qs Rs ,Rl osc Aio Ic Normalized Null Loop I Gain I Qr Rs ,Rl osc 0 I c I 0 s Rino gm1Va Closed Loop Gain I os Aio Is 1 Ts η,Rs ,Rl I1s Rs 0 1 gm2 ro3 Ios Ios Null Gain Calculation Rino gm1Va Routo ro1 Rl Va Aio 1 Qs Rs ,Rl η 0 Aio η 1 Aio η EE 536a Lecture Aid #5 Rl Va os ro1 I1s Rs Signal Flow Analysis Addendum Ic ro3 1 gm2 Iosc Iosc Loop Gain Calculation 308 Loop Gain Characteristics Loop oop Gain Ga Expression p ess o g m1ro1 Rs ηro1 η g m1ro1 Rs ηro1 Qs Rs ,Rl Aio Ts η,Rs ,Rl η η g η Rl 2r o1 Rl 1 m1 r o1 g m2 Loop Gain Dependence On Signal Source Resistance Ts η,0,Rl 0 2 g m1r g m1ro1ro3 η o1 Ts η, ,Rl g m1 g m2 ηg m3 Rl 2r 2 g o1 Rl 1 m1 r g m2 o1 ro1 ro2 ro3 η Loop Gain Dependence On Terminating Load Resistance Ts η, η,Rs , 0 g m1ro1 Ts η,Rs ,0 EE 536a Lecture Aid #5 g m1ro1 Rs ro3 η 1 Signal Flow Analysis Addendum g m1 ro1 g m2 g m1 Rs ηro1 2η 309 Closed Loop Wilson Metrics I Aio Aio g Ai os η m1 Is 1 Ts η,Rs ,Rl 1 Aio η g m3 1 Ts η,0,Rl ro3 2η Rin Rino g m1r 1 T η, ,R R g m1 s l o1 1 2 C osed Loop Closed oop I/O /O Current Gain, Ai Closed Loop Input Resistance, Rin Closed Loop Output Resistance, Resistance Rout g m1 Rs ηro1 1 Ts η,Rs ,0 Rout Routo 2ro1 1 2η 1 Ts η,Rs , Rs ηro1 g m1ro1 η Comments Moderately Small, But Very Predictable, Closed Loop Current Gain Small Closed Loop Input Resistance Large g Closed Loop p Output p Resistance Avoid Large η So As Not To Compromise I/O Resistances And Bandwidth EE 536a Lecture Aid #5 Signal Flow Analysis Addendum 310 Common Source-Wilson Cascode Circuit C cu t Sc Schematic e at c Diagram ag a Indicated Currents Assumes Saturation Region Biasing For All Transistors Ignores Channel Resistances Output Signal Response Vos Rl ηg m4Vs Vos ηg m4 Rl Vs I/O Resistances 2η Rin g m1 +Vdd (IQ gm4Vs ) Rl Rs Riw M4 IQ gm4Vs Vs Vo Rowc M1 IQ gm44Vs M3 Vgg M22 (IQ gm4Vs ) (IQ gm4Vs ) g r Rout m1 o1 ro4 ηro1 η Effecti el A Common Source-Common Effectively So rce Common Gate Cascode With C Current rrent Gain And With No Phase Inversion EE 536a Lecture Aid #5 Signal Flow Analysis Addendum 311 +Vdd Circuit C cu t Sc Schematic e at c Diagram ag a Wilson Stage Provides Predictable Current Gain R Acts As A Common Gate Stage That Boasts Current Gain Mitigates Impact Of M4 Gate-Drain V Capacitance M4 Drain Sees Small Effective V s s (IQ gm4Vs ) Rl Riw M4 IQ gm4Vs Vo Rowc M1 IQ gm4Vs M3 gg Load Resistance, Rin. Cannot Design For Large Current G i Because Gain B Larger L G Gains i Lead To Larger Rin M2 (IQ gm4Vs ) Co ommon So ource-Wilso on Cascod de Wilson Cascode Comments (IQ gm4Vs ) Capacitances Of M3 And M2 Are Likely Inconsequential One Exception May Be Bulk-Drain Capacitances Of M3 And M4 M2 Is Connected As Diode, And Therefore Projects Small Terminal Resistance Load Resistance Rl Can Be Reduced By Factor Of η, Thereby Improving Bandwidth While Maintaining Overall Voltage Gain EE 536a Lecture Aid #5 Signal Flow 312 Regulated Common Gate Cell +Vdd Basic as c Sc Schematic e at c Diagram ag a Architecture And Operation Current IQ + Is Generally Supplied By Drain Of Common Source Amplifier IQ Is Quiescent Component Of Applied Current Is Is Signal Component Of Applied Current Rs Is Signal Source Resistance (Large If Current Is R Rl Rout Vo IoQQ+Ios M1 Vr M2 Vi S Supplied By Common C S Source)) Active Feedback Manifested By Transistor M2 Lowers Input Resistance, Rin Raises Output Resistance Resistance, Rout Consider Voltage Vi Increasing Rin IQ+Is Rs Voltage Vr Resultantly Diminishes Because Of Phase Inversion In Transistor M2 Results In A Decrease In Voltage Vi, Which Ensures Negative Feedback Produces An Increase In Voltage Vo Because Of Phase Inversion In Transistor M1 Decrease In Vi Begets Decreased Input Resistance Increase In Vo Foretells Increased Output Resistance Performance Metrics Can Be Deduced Via Signal Flow EE 536a Lecture Aid #5 Signal Flow 313 Regulated Cell Small Signal Model Small S ll Signal Si l Model M d l All Transistors In Saturation Ignore Bulk-Induced Threshold V lt Voltage Modulation M d l ti Do Not Ignore Channel Length Modulation Rout Vos gm1Vb EE 536a Lecture Aid #5 gm2Va Rin ro2||R Is Va Rs Ios Routo Vos gm1Vb 0 0 ro1 R1 Iosogm1Vb Vb Ioso ro2||R Is Signal Flow R1 Vb Feedback Parameter Choose P = gm2 Null Parameter Small Signal Model: P = gm2 = 0 Evaluate Null Parameter Current Gain, Aio = Ioso /Is Null Parameter Input Resistance, Rino Null Parameter Output Resistance, Routo ro1 Va Rino Rs Ioso IosoIs 314 Null Parameter Model Calculations Vos Null Parameter Gain I Rs Rs Aio oso r Rl 1 Is Rs Rs o1 g m1 1 g m1ro1 Null Input/Output Resistances V r Rl 1 Rino x o1 Ix 1 g m1ro1 g m1 Vy Routo Iy ro1 1 g m1ro1 Rs 1 g m1Rs ro1 gm1Vb 0 0 R1 Iosogm1Vb Vb Ioso ro2||R Rino Va Is Rs Routo ro1 gm1Vb R1 Ix Vx gm1Vb Vy ro1 Iy Iygm1Vb Iy Rino Vb Ioso IosoIs Ixgm1Vb Ix ro1 Vb Rs Observations Ob ti I I I Rino Is Relatively Small Routo Can Be Very Large Rs Rs Rs A Obvious Ob i Alternative Alt ti G Gain i io ro1 Rl 1 Rs Rin R R Expression s s g m1 1 g m1ro1 EE 536a Lecture Aid #5 Signal Flow x y y 315 Calculation Of Loop Gain Model ode For o Normalized o a ed Loop oop Gain Ga Normalized Loop Gain, Qs(Rs, Rl) V Qs Rs ,Rl ac Ic g m1ro1 ro2 R Rs ro1 gm1Vb Ic Ic R1 Vac /Rsgm1Vb Vb Vac /Rs ro2||R 0 Vac Rs Vac /Rs Vac /Rs roo1 Rl 1 g m1 m ro1 o Rs Loop Gain, T(gm2, Rs, Rl), Of Regulated Common Gate Cell gm1ro1 gm2 ro2 R Rs T g m2 ,Rs ,Rl g m2Qs Rs ,Rl ro1 Rl 1 g m1ro1 Rs g m1Rs g m2 ro2 R g m2 R 1 g m1Rs Approximation Requires: ro2 >> R gm1Rs >> 1 Loop Gain Collapses To Gain Magnitude Of M2−R Subcircuit EE 536a Lecture Aid #5 Signal Flow 316 Calculation Of Null Loop Gain Pertinent e t e t Model ode Output Current Response Is Set To Zero Applied pp Input p Current Is Not Null gm1Vb Ic Ic R1 gm1Vb Vb IsVac /Rs = 0 ro2||R Is Normalized Null Loop Gain V Qr Rs ,Rl ac I c I 0 ro1 Vac Rs Vac /Rs 0 os g m1ro1 ro2 R 1 g r m1 1 o1 1 Null Loop Gain, Tr(gm2, Rs, Rl) g r Tr g m2 ,,Rs ,,Rl g m2Qr Rs ,,Rl g m2 ro2 R m1 o1 g m2 R 1 g m1ro1 Note Loop Gain And Null Loop Gain Are Approximately Equal Implication Is That The Closed Loop Gain Approximately Equals The N ll P Null Parameter C Current G Gain i (Feedback (F db k Has H Almost Al No N Effect Eff O On Gain) EE 536a Lecture Aid #5 Signal Flow 317 Closed Loop Regulated Cell Performance 1 Tr g m2 ,,Rs ,R , l C Closed osed Loop oop Current Cu e t Rs Ai Aio A io Gain 1 T g ,R ,R Rs Rin m2 s l 1 Closed Loop Input Resistance 1 T g m2 ,0,Rl ro1 Rl 1 Rin Rino 1 T g m2 , ,Rl 1 g m1ro1 1 g r R g m1ro1 m2 o2 1 g r m1 o1 Rino Rino 1 g m1 1 g m2 R 1 g m2 R 1 T g m2 ,R Rs ,R Rl Closed Loop Output Resistance g m1ro1 g m2 ro2 R Rs 1 T g m2 ,Rs ,0 Rout Routo 1 g m11Rs ro11 1 ro1 1 g m1ro1 Rs 1 T g m2 ,Rs , 1 g m1Rs ro1 1 g m2 R Routo 1 g m2 R Routo 1 T g m2 ,Rs ,Rl EE 536a Lecture Aid #5 Signal Flow 318 Comments On Regulated Common Gate Aio 1; 1 Rin 1 ; Rout 1 g m1Rs ro1 1 g m2 R g m1 1 g m2 R Current Gain Current Gain Essentially Unaffected By Feedback Unity Because Source Current Of M1 Is Nearly The M1 Drain Current; M2 Gate Draws No Current At Low Frequencies I/O Impedances I d Input Impedance Is Dramatically Reduced By Approximately The Return Difference, Reduction Factor Is Return Difference (1+gm2R) Output O t t Impedance I d Is I Dramatically D ti ll Increased I d By B Approximately A i t l Th The Return Difference , Factor Of Increase Is Return Difference (1+gm2R) Amount Of I/O Impedance Modulation Controllable Through CurrentDependent Transconductance Of Transistor M2 Very Low Input And Very High Output Impedances Beget Excellent Current Amplifier Regulated R l t d Cascode C d Allows All For F A “Super” “S ”C Common S SourceRegulated Common Gate Cascode EE 536a Lecture Aid #5 Signal Flow 319 “Super” Cascode +Vdd Ci Circuit it S Schematic h ti Di Diagram Commentary Excellent Transconductor High Input Resistance Seen By Vs Very High Output Resistance Seen By Rl Transconductance Gain: Ios gmd Source Degeneration Vs 1 g md Rss May Not Be Necessary Increases Circuit Noise Diminishes Performance Sensitivityy To Driver Transconductance gmd Small Indicated Resistance Rin Mitigates Miller Multiplication Of Gate-Drain Capacitance C it Of Driver Di T Transistor i t Md Helps To Establish Dominant Pole At Output Port Of Amplifier R Rl Rout Vo IoQ+Ios Vr Rs M1 M2 Vi Rin Md Vs Rss Vgg Differential Version Of Cascode Structure Can Certainly Be Promulgated EE 536a Lecture Aid #5 Signal Flow 320 Simple Common Source At High Frequencies +Vdd Schematic Sc e at c Diagram ag a And d Model ode Model Parameters V R Resistance Rll Includes Channel Rll Rl ro Resistance ro V C C Capacitance Ci Includes Signal Source Capacitance Cs And Net Z V Gate-Source Gate Source Capacitance Cgs, Inclusive Of Gate-Source Overlap Capacitance Cf Is Net Gate-Drain Z C Capacitance p Cgd ((With Overlap) p) R V V Capacitance Co Includes Load gV R C C V Capacitance Cl And Bulk-Drain Z Capacitance Cbd There Is No Threshold Modulation P sC f Ci Cs C gs Signal Flow Problem Find Voltage Gain C f C gd Find I/O Impedances Co Cl Cbd Choose Admittance sCf As Critical Feedback Parameter Rl Zout o s s s l in gg out f s os i s m ll o in EE 536a Lecture Aid #5 Signal Flow 321 Null Parameter Common Source Metrics Null u Voltage o tage Gain Ga Obtainable By Inspection Obvious Two-Pole Function V V V Avo oso oso Vs V Vs Zouto Rs V Voso Ci Vs gmV Rll Co Zino Av (0) g m Rll 1 sRRll Co 1 sRRsCi 1 sRRll Co 1 sRRsCi Zino 1 sCi Null Input And Output Impedances Z outo Rll Rl Also Obtainable Via Inspection p Nature Of Null Impedances Input Impedance Is Capacitive (Gate-Source Capacitance) Output Impedance Is Resistive (Net Load Resistance) Avo(0) = −gmRll Is Zero Frequency Voltage Gain Of Amplifier Return Ratios Normalized Return Ratio Is Impedance p Seen By y sCf With Vs = 0 Normalized Null Return Ratio With Respect to Admittance Cf Is Analogous Impedance, But With Vos = 0 EE 536a Lecture Aid #5 Signal Flow 322 Common Source Return Ratios Normalized o a ed Return etu Ratio, at o, Qs V Qs x I x V 0 Ix Rs s V Ci 0 g m Rll 1 1 sR C ll o Normalized Null Return Ratio, Ratio Qr V 1 Qr x I x V 0 gm V os Null Return Ratio, Tr Tr sC f Qr sC f g m Vos Vx gmV Rll Co s Ix Rll Rs 1 sRll Co 1 sRsCi Rs V 0 Vx Ci gmV Rll Co Normalized Return Rll 1 g m Rll Rs sRll Rs Co Ci Vx Qs Ratio, Qs I x V 0 1 sRll Co 1 sRsCi s Return Ratio, Ts, With Respect To Capacitive Admittance sCf sC f Rll 1 g m Rll Rs s 2 Rll RsC f Co Ci Ts sC f Qs 1 sRll Co 1 sRsCi EE 536a Lecture Aid #5 Signal Flow 323 Common Source Closed Loop Gain Gain Expression Ga p ess o 1 Tr Vos Av Avo Vs 1 Ts sC f g m Rll 1 gm Avo ((0)) g m Rll 1 s Rll Co C f Rs Ci 1 g m Rll C f s Rll RsCoCi 1 C f 2 1 1 C C o i Comments Right Half Plane Zero Established At s = gm /Cf Two Circuit Poles Three Capacitors Present In Model Order (Number Of Poles) Established By the Number Of Initial Conditions That Can Be Independently Assigned To Energy Storage El Elements t In I Circuit Ci it In This Case Only Two Independent Capacitor Voltages Can Be Set Return Ratio Low Frequency Phase Shift Is 90° Very High Frequency Phase Shift Is 0° Low Frequency Magnitude Is Zero EE 536a Lecture Aid #5 Signal Flow 324 Common Source Input Impedance 1 Ts 1 sRll Co C f 1 Rs 0 Zin (s) Zino 1 Ts sC sRll C f Ci Co ieff Rs 1 sRll Co 1 Cieff Approximation Cieff Ci 1 g m Rll C f Ci 1 Avo ( 0 ) C f Small Cf Likely In A (0) g R Input p Impedance Self-Aligning Process Cf << Co (Likely For Capacitive Loads) Large Zero Frequency Gain Magnitude (|Avo(0)| >> 1) vo m ll 1 Resultant Input Impedance sCieff Obviously A Capacitive Input Impedance Ciieff Effective Input Capacitance Is Cieff ff Ci Cm Includes A Miller Effect Cm 1 g m Rll C f 1 Avo (0) C f Capacitance, Cm Zin (s) Miller Capacitance Cm, And Thus Cieff, Exacerbated By Increased Magnitude Of Zero Frequency Gain, Gain |Avo(0)| Effective Input Capacitance Rises With Increasing Frequency EE 536a Lecture Aid #5 Signal Flow 325 Common Source Output Impedance sRsC f Output Impedance 1 1 Ts 1 sR C C s i o Rll Z out (s) Z outo C 1 Ts R 1 ll 1 g R f sR C Co 0 m ll ll f Rs C Approximation i For Large gmRll: 1 sR C C s i f 1 Z (s) R ll out Conclusion g 1 m 1 sR C 1 s R C Is That High Zero ll i s i g m Frequency Input Impedance Gain Remains Capacitive At High Signal Frequencies Capacitance Load, Co Co = ∞ Is Equivalent q To Short Circuit Load Impedance p Co = 0 Is Equivalent To Open Circuit Load Impedance Note Relationships For Performance Metrics Are “Sloppy,” But Are Rendered Understandable Via Signal Flow Analytical Methods EE 536a Lecture Aid #5 Signal Flow 326 Back To Common Source Gain Ga Gain Expression 1 cs Vos Av (s) Avo (0) 2 Vs 1 as bs Gain V i bl Variables Avo (0) g m Rll a Avo (0) 1 cs s s 1 Qωn ωn 2 1 Rll Co C f Rs Ci 1 g m Rll C f Qωn 1 1 c C f gm b Rll RsCoCi 1 C f 2 C C ωn o i Variable “ω ωn” Is Undamped Natural Frequency Of Network; Also Known As Self-Resonant Frequency Of Amplifier Variable “Q” Is Quality Factor Of Network 1 Typical Design Targets Small “c” (Zero In Far Right Half Frequency Plane) Large ωn (Self-Resonant Frequency Is Outside Passband Satisfaction S ti f ti Si Simplifies lifi Estimation E ti ti Of 3 3-dB dB Bandwidth B d idth EE 536a Lecture Aid #5 Signal Flow 327 Satisfaction Of Typical Design CS Targets Approximate pp o ate Dominant o a t Pole oe Gain Expression Av (s) Approximate Bandwidth, B B Qωn 1 a Avo (0) 1 cs s s 1 Qωn ωn Q 2 Avo (0) s 1 Qωn Variable “a” Can Be Computed Exactly Directly From Circuit As Sum Of Open Circuit Time Constants (Other Capacitances Are Open Circuited When Evaluating A Particular Time Constant) With Input Signal Source Set To Zero Value---More About The Theory Underlying This Computation Later Variable “c” c Can Be Computed Exactly Directly From Circuit As Sum Of Open Circuit Time Constants (Other Capacitances Are Open Circuited When Evaluating A Particular Time Constant) With Output Response p Set To Zero --- More About This Theory y Later Dominant Pole Approximation Frequency Of Other Pole And Of Zero Lie At Very High Frequencies Approximation Is Tantamount To A First Order Network Model Broadband Problems Amount To Identifying Largest Time Constant Contribution To “a” Mitigate (Reduce) Largest Time Constant Value EE 536a Lecture Aid #5 Signal Flow 328 Model Implication Of Typical Design Targets Approximate pp o ate Gain Ga g m Rll ecs Approximation Av (s) 1 s R C C R C 1 g R C ll o f s i m ll f cs 1 cs e c C f gm c is Effectively The Envelope, Or Steady State, Delay Of Amplifier Approximate Small Signal M d l Model Net Input Port Capacitance V Cieff Ci 1 g m Rll C f Zout Rs V Cieff s Vos cs gme V Rll Co + Cf Zin Forward Transconductance 1 Has Phase Angle Of ωc a RsCieff Rll Co C f Tantamount To Envelope (Steady Qωn State) Delay Of c B Qωn 1 a Valid Only For Small c Zero In Far Right Half Plane Large gm And/Or Small Cf Closed Cl dL Loop St Stability bilit Not N t Compromised C i d Sum Of Open Circuit Time Constants Is Identically “a” EE 536a Lecture Aid #5 Signal Flow 329