A Fully Integrated 24 GHz 4-Channel Phased

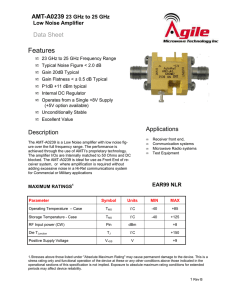

advertisement

A Fully Integrated 24 GHz 4-Channel Phased-Array Transceiver in 0.13μm CMOS Based on a Variable-Phase Ring Oscillator and PLL Architecture Harish Krishnaswamy and Hossein Hashemi University of Southern California Los Angeles, CA Presentation Summary • Introduction • Variable Phase Ring Oscillator-PLL Phased Array • A 4-Channel 24 GHz CMOS Phased Array Transceiver • Array Measurement Results Introduction to Phased Arrays τ .. . τ Controlling the time delay between the N channels “steers” the EM beam electronically. Introduction to Phased Arrays NΔτ .. . θtr Controlling the time delay between the N channels “steers” the EM beam electronically. θtr=sin-1(ωΔτ/π) Δτ Phased Array Benefits • Spatial interference cancellation • 10log(N) improvement in RX SNR (for active arrays) • 20log(N) improvement in TX EIRP 24 GHz Frequency Allocations Frequency (Hz) 22 G 24 G 24.25 G 29 G Industrial, Scientific, Medical Applications - High Speed Point to Point Wireless Communication - 250 MHz → 1 Gbps with 16-QAM (assuming 4 b/s/Hz) UWB Vehicular Radar Applications - Parking Aid, Collision Avoidance, Blind Spot Detection - 7 GHz BW → 2 cm range resolution Presentation Summary • Introduction • Variable Phase Ring Oscillator-PLL Phased Array • A 4-Channel 24 GHz CMOS Phased Array Transceiver • Array Measurement Results Conventional Phased Array Topologies + Mixer dynamic range eased due to interference cancellation. - Compact, low-loss, linear RF phase shifters are a challenge on silicon. + Phase shifters out of the signal path and hence do not affect system performance. - Mixer dynamic range must allow for interferers. + Versatility - Mixer and ADC dynamic range must allow for interferers. - ADCs and DSP are power-hungry. Variable Phase Ring Oscillator (VPRO) Node Voltages (V) 1.5 0 Time (ps) 500 1000 0o -1.5 Tunable boundary phase shifter allows for controllable phase progression for beam steering. Variable Phase Ring Oscillator (VPRO) Node Voltages (V) 1.5 0 Δφ Time (ps) 500 1000 -NΔφ -1.5 Tunable boundary phase shifter allows for controllable phase progression for beam steering. Transmit Operation RLC Phase Shift (deg) 100 50 Frequency (GHz) ωosc 0 21 24 27 -50 -100 0o • Each node is routed to a separate antenna signal path. • PLL ensures 24 GHz operation for all steering angles. 30 Transmit Operation RLC Phase Shift (deg) 100 ωosc 50 Frequency (GHz) 0 21 24 27 -50 -100 -NΔφ • Each node is routed to a separate antenna signal path. • PLL ensures 24 GHz operation for all steering angles. 30 Transmit Operation RLC Phase Shift (deg) 100 ωosc 50 Frequency (GHz) 0 21 24 27 -50 -100 -NΔφ • Each node is routed to a separate antenna signal path. • PLL ensures 24 GHz operation for all steering angles. 30 Transmitter Architecture • Mixers, power splitters, and phase shifters are eliminated. • VCO pulling is not a concern as VPRO is modulated. VPRO Injection Locking Properties Δθ 10 Δφ =30o 8 Locking Range (MHz) 6 4 2 30o 100 -200 -100 200 Injection Phase Progression Δθ (deg) Δωlock Iinj N sin (Δθ-Δφ) ωoscR(1+tan Δφ) 2 Phased = A(2Q+tanΔφ) Nsin (Δθ-Δφ) Array Factor 2 2 Injection Locking Range of a free-running VPRO shows phased array spatial selectivity. VPRO-PLL Response to Injection 100 80 60 RLC Phase Shift (deg) ωosc Frequency (GHz) 40 20 0 -20 21 24 27 -40 -60 -80 ωinj-ωPLL At vctrl, the PLL down-converts the injected signals. 30 Receive Operation Spatial Selectivity Frequency Selectivity Down-converted Signal at Vctrl (mV) Down-converted Signal at Vctrl (mV) Theory Simulation Simulation Theory -200 -100 0 100 200 Injection Phase Progression (deg) v ctrl = -200 -100 0 100 Frequency Offset (MHz) Δωlock K dK VCOF(s) x K vco sNdiv +K dK VCOF(s) Kvco : VPRO Gain, Kd : PFD Gain, Ndiv : Division ratio, F(s) : Loop Filter 200 Receiver Demodulation Capability N sin (Δθ-Δφ) v ctrl ωoscR(1+tan Δφ) K dK VCOF(s) 2 ∝ x x (Δθ-Δφ) sNdiv +K dK VCOF(s) Pinj A(2Q+tanΔφ)K VCO Nsin 2 2 LNA + + - - + + - - + + - - vctrl + + - - Ref Div. by 128 Tri-state PFD Loop Filter Charge Pump o Baseband Output System suitable for a variety of amplitude, phase and frequency modulation schemes such as QAM, OFDM, etc. Noise Processes in the VPRO-PLL RX Input Noise • Noise injected into VPRO results in phase noise. • PLL dynamics translate phase noise to baseband at vctrl. Noise Figure of the VPRO-PLL RX Scheme 4-element 1GHz VPRO and PLL Noise Figure (dB) 3.2 NF (theory) NF (Theory) NF (Sim) NF (Sim.) 3.1 3 2.9 2.8 2.7 2.6 0 1 NF= π 2π 2 sin ∫ θIn (Acosθ)dθ+kT/50 0 kT/50 5 10 15 Bias Current (mA) sin θ : Impulse Sensitivity Function1 In : Noise Modulation Function • Reference, divider, and PFD noise are neglected. • NF improves with decreasing VPRO bias current. 1 A. Hajimiri et al., “A general theory of phase noise in electrical oscillators,” JSSC, vol. 32, no. 2, Feb. 1998, pp. 179-194. Linearity of the VPRO-PLL RX Oscillator Bias Level Itotal β Iinj Ifund Phase Shift β Kvco Linearity Must lie in linear region Oscillation Frequency Frequency P-1dB Ibias ⇒ I inj = 4π Vctrl Linear Output Operating Range • Increase in VPRO element current improves linearity. • Increase in Kvco linear tuning range improves linearity. System Design Trade-offs Gain ∝ 1 ωoscR(1+tan Δφ) π NF= A(2Q+tanΔφ)K VCO 2 2π 2 sin ∫ θIn (Acosθ)dθ+ 0 kT 50 kT 50 P-1dB Ibias ⇒ I inj = 4π DC Gain NF Linearity Ibias ↑ ↓ ↑ ↑ Q↑ ↓ _____ ↑ ↓ sensitive to supply noise highly linear for high P-1dB Kvco ↑ These trade-offs are critical for system optimization. Presentation Summary • Introduction • Variable Phase Ring Oscillator-PLL Phased Array • A 4-Channel 24 GHz CMOS Phased Array Transceiver • Array Measurement Results 24 GHz 0.13μm CMOS Phased Array TX+RX 2.15mm 2.35mm Mixers, power splitters/combiners, and phase shifters are eliminated. On-chip High Frequency Routing W=10 μm S=13 μm 10 μm 3 μm 5 μm Substrate-shielded Coplanar Stripline1 5 μm • Floating metal strips reduce substrate loss. • Attenuation constant = 0.28 dB/mm at 24 GHz. 2 T.S.D. Cheung et al., “On-chip interconnect for mm-wave applications using an all-copper technology and wavelength reduction,” in ISSCC Dig. Tech. papers, Feb. 2003, pp. 396-501. On-chip High Frequency Routing Frequency (GHz) W=10 μm S=13 μm 10 μm 3 μm 5 μm Substrate-shielded Coplanar Stripline1 5 μm 0 0 -0.05 -0.10 -0.15 -0.20 -0.25 -0.30 -0.35 -0.40 S21 (dB) 3 6 9 12 15 18 • Floating metal strips reduce substrate loss. • Attenuation constant = 0.28 dB/mm at 24 GHz. 2 T.S.D. Cheung et al., “On-chip interconnect for mm-wave applications using an all-copper technology and wavelength reduction,” in ISSCC Dig. Tech. papers, Feb. 2003, pp. 396-501. 24 GHz VPRO -NΔφ Phase shifter implemented using 4 more identical tuned stages for symmetry. 24 GHz VPRO Ibias per stage 7.5 mA L 110 pH QL 29 -NΔφ Phase shifter implemented using 4 more identical tuned stages for symmetry. Low Noise Input Buffer and Output PA Driver ... ... Low Noise Input Buffer Ibias per stage 2.5 mA NF 6.7 dB S11 <-10 dB Output PA Driver Low Noise Input Buffer Output PA Driver Ibias per stage 13 mA Pout 1.75 dBm S11 <-10 dB The VPRO is designed to account for the loading effect of the input buffer and PA driver. Measured VPRO Performance Frequency (GHz) Frequency Offset (Hz) Phase Noise (dBc/Hz) 1k 10k 100k 1M 10M 100M -40 -60 -97 to -105 dBc/Hz @ 1MHz -80 -100 -120 -140 Steer Extreme Right Broadside Steer Extreme Left Vctrl (V) phase control (V) Frequency dependence is symmetric with respect to control voltage and phase control. 24 GHz CMOS Power Amplifier Ibias=78 mA • PA is biased for Class AB operation. • Matching is achieved through spiral inductors and MIMs. Frequency (GHz) Output Power (dBm) Gain (dB), Efficiency (%) Gain (dB) Reflection Coeff. (dB) Measured 24 GHz CMOS PA Performance Input Power (dBm) • Saturated output power is 12.9 dBm. • Peak drain efficiency is 19%. 24 GHz CMOS Low Noise Amplifier • Two stage inductor-degenerated design (Ibias=25 mA). • Input designed for optimal noise performance given power matching requirements. 24 GHz CMOS LNA Measurement Results Gain (dB) NF (dB) 10 15 9 10 8 S22 (dB) -5 S11 (dB) 0 -10 -5 55 7 0 6 5 -5 4 -10 19 21 23 Frequency (GHz) 25 -15 -10 -20 -25 -15 Frequency (GHz) Minimum NF < 6 dB is achieved at 23 GHz. Measured Spectrum (dBm) 24 GHz Integer-N Synthesizer v ctrl Zoomed In 0 -10 -20 -30 30 dB -40 -50 -60 -70 -80 -90 -100 23.7 23.8 23.9 24 24.1 24.2 Frequency (GHz) Δωlock K dK VCOF(s) = x K VCO sNdiv +K dK VCOF(s) Synthesizer is designed for a loop BW of 10 MHz, which governs RX frequency selectivity. Receiver Gain (dB) Single Channel Receiver Transfer Function Offset Frequency (MHz) • High selectivity is a function of PLL design parameters. • Inferred array gain is 42 dB. Presentation Summary • Introduction • Variable Phase Ring Oscillator-PLL Phased Array • A 4-Channel 24 GHz CMOS Phased Array Transceiver • Array Measurement Results 4-path Array Pattern Measurement Setup TX1 TX4 TX2 TX3 Variable delay elements emulate wave propagation in space. 4-path Array Pattern Measurements 4-path TX patterns 2-path RX patterns Patterns are not calibrated and include packaging mismatches. Performance Summary Technology Process 0.13 μm CMOS Chip Area 2.15 x 2.35 mm2 Transmitter Performance Maximum PA Output Power* >12.9 dBm 4-element EIRP >24.9 dBm Peak PA Drain Efficiency >19 % Receiver Performance Receiver Gain 30 dB Total Array Gain 42 dB LNA Noise Figure 6 dB SNR Improvement (Ideal) 6 dB LO Path Performance Synthesizer Loop BW VPRO Free-running Phase Noise @ 1MHz *limited by measurement equipment. 10 MHz -97 to -105 dBc/Hz Comparison with Prior Works ISSCC’041 ISSCC’052 This work Frequency 24 GHz 24 GHz 24 GHz Functionality RX TX TX+RX No. of Channels 8 4 4 Technology 0.18 μm SiGe 0.18 μm SiGe 0.13 μm CMOS EIRP N/A 26 dBm >24.9 dBm PA Peak PAE N/A 6.5 % >12.3 % Front End NF 5 dB (sim.) N/A 6 dB Power Consumption 0.91 W 1.97 W RX: 0.52 W TX: 0.98 W Area 11.6 mm2 14.28 mm2 5.1 mm2 1 H. Hashemi et al., “A fully integrated 24GHz 8-path phased array receiver in silicon,” in ISSCC Dig. Tech. papers, Feb. 2004, pp. 390-534. 2 A. Natarajan et al., “A 24GHz phased-array transmitter in 0.18μm CMOS,” in ISSCC Dig. Tech. papers, Feb. 2005, pp. 212-594. Conclusion • A VPRO-PLL phased array transceiver architecture is demonstrated that achieves full phased array functionality while eliminating key building blocks such as mixers, phase-shifters and power splitters and combiners. • Rigorous analysis of this new architecture reveals the capability to handle various phase, frequency, and amplitude modulation schemes (QAM, OFDM). • A 24 GHz CMOS implementation validates the theoretical claims. Acknowledgements This work was partially supported by • Charles Lee Powell Foundation • USC Viterbi School of Engineering Our thanks to • Arun Natarajan from Caltech • Mahmood Bagheri and Andrew Stapleton from USC • Ta-shun Chu, Ankush Goel and the rest of our research group at USC for support and assistance