A 3.8 GHz programmable gain amplifier with a 0.1 dB gain step

advertisement

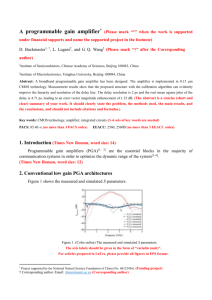

Vol. 35, No. 3 Journal of Semiconductors March 2014 A 3.8 GHz programmable gain amplifier with a 0.1 dB gain step Lin Nan(林楠)1; , Fang Fei(方飞)1; 2 , Hong Zhiliang(洪志良)1 , and Fang Hao(方昊)3 1 State Key Laboratory of ASIC and Systems, Fudan University, Shanghai 201203, China Semiconductor Co, Ltd, Shanghai 201203, China LSI Corporation, 1320 Ridder Park Drive, San Jose, CA 95131, USA 2 Telink 3 Abstract: A broadband programmable gain amplifier (PGA) with a small gain step and low gain error has been designed in 0.13 m CMOS technology. The PGA was implemented with open-loop architecture to provide wide bandwidth. A two-stage gain control method, which consists of a resistor ladder attenuator and an active fine gain control stage, provides the small gain step. A look-up table based gain control method is introduced in the fine gain control stage to lower the gain error. The proposed PGA shows a decibel-linear variable gain from 4 to 20 dB with a gain step of 0.1 dB and a gain error less than ˙0.05 dB. The 3-dB bandwidth and maximum IIP3 are 3.8 GHz and 17 dBm, respectively. Key words: variable gain amplifier; programmable gain amplifier; decibel-linear gain; CMOS integrated circuits; hard disk drives DOI: 10.1088/1674-4926/35/3/035004 EEACC: 2220 1. Introduction Programmable gain amplifiers (PGA) are the essential blocks in the majority of communication systems in order to optimize the dynamic range of the system. In hard disk drives (HDD), broadband PGA is implemented to process the appropriate signal level in the read/write channel. In the analog front end of HDD read channel, the gain of the PGA is digitally controlled by the automatic gain control (AGC) loop to equalize the input signal amplitude. Decibellinear gain variation of the PGA is required to achieve a constant settling time of the AGC loop. A gain step of 0.1 dB is necessary to improve the sensitivity of a HDD read channel, which requires a gain error of less than 0.1 dB. A bandwidth larger than 3 GHz is needed to transmit a high speed signal in modern HDD read channels. In this paper an open-loop PGA with two-stage gain control is presented, providing both wide bandwidth and high gain accuracy. The gain of the open loop PGAs shown in Fig. 1(c) is controlled by the ratio between load and input transconductancesŒ3 5 . However, the bandwidths of these PGAs are limited to around 1 GHz and vary with different gain settings because the variable load transconductances change the pole frequency. Furthermore, the minimum available gain error of this type of PGA is more than 0.5 dB with various pseudoexponential functions introduced. An open loop PGA with only the input transconductance variableŒ6 is depicted in Fig. 1(d). The pole at the output node is constant with an invariable load resistor, resulting in a constant bandwidth across the gain variable range. But without broadband circuit design, the bandwidth of the PGA is less than 1.5 GHz. 2. Conventional low gain error PGA architectures The gain of the closed loop PGAŒ1 illustrated in Fig. 1(a) is determined by the ratio between the variable resistor and the feedback resistor, which can provide precise gain unrelated to process and temperature variation. However, a large number of resistors, which consume a large area, are needed in the variable resistor network to achieve a small gain step and large gain variable range. Also, the bandwidth is limited to several dozen megahertz due to the closed loop architecture. The PGA with a closed loop fine gain control stageŒ2 shown in Fig. 1(b) achieves a small gain step within an acceptable area. The bandwidth is extended to several hundred megahertz by using a compensation network, which is still insufficient for data transmission of high speed HDDs. Fig. 1. Proposed PGA with (a) resistor network, (b) closed-loop gain control stage, (c) variable input and load transconductance and (d) variable input transconductance. † Corresponding author. Email: linnan@fudan.edu.cn Received 31 July 2013, revised manuscript received 12 October 2013 035004-1 © 2014 Chinese Institute of Electronics J. Semicond. 2014, 35(3) Lin Nan et al. Fig. 2. Architecture of a HDD read channel. 3. Architecture of the proposed PGA Since closed loop PGA and open loop PGA without broadband circuit design cannot provide sufficient bandwidth, a PGA design based on open loop broadband circuit topology is needed. Also, a gain control method other than the pseudoexponential gain control is required for a small gain step and low gain error. The architecture of the proposed open-loop PGA is illustrated in Fig. 2, which consists of a passive attenuator (ATT), a fine gain control stage (FGC), a fixed gain amplifier (FGA) and an output buffer. Since the signal picked up from the hard disk drive is first amplified by a low noise pre-amplifier, noise is not a main concern in the proposed PGA. As a result, an attenuator is placed at the front-end to increase the input signal dynamic range of the PGA. The Cherry–Hooper based FGC is placed as the second stage, and the fixed gain amplifier at the back-end provides both large output swing and sufficient total gain to the PGA. The gain range of the PGA is sub-divided into successive segments by the attenuator. The FGC then control the voltage gain precisely within the gain range of each segment. Finally, the signal is amplified to the required level by the FGA. The resistor ladder attenuator can provide attenuation of 4 dB per step in a 24 dB range, and the FGC can provide gain from 6 to 10 dB with a 0.1 dB gain step. The fixed gain amplifier can provide a gain of 10 dB, therefore the PGA can provide gain from 4 to 20 dB with a gain step of 0.1 dB. 4. Schematic design of the proposed PGA 4.1. Attenuator circuit design An attenuator is introduced as the first stage to increase the input signal dynamic range of the PGA. The main disadvantage of the resistor ladder attenuator is that the number of resistors increases with the number of attenuation states. Thus it occupies a large area for a small attenuation step or a large attenuation range. However, the attenuation step is as large as 4 dB since a 0.1 dB gain step is achieved in the FGC stage; besides, the attenuation range is limited to 24 dB by the variable range of the PGA. A resistor ladder attenuator is therefore suitable as the first stage of the proposed PGA. Fig. 3. Schematic of the resistor ladder attenuator. The resistor ladder attenuator is depicted in Fig. 3. The ratio between R1 , R2 and R3 is determined by R3 =2 D m; R1 C R3 =2 (1) R2 =2 .R1 C R3 =2/ R3 D ; R2 =2 C R1 C R3 =2 2 (2) Vout D m0 a0 C m1 a1 C C m6 a6 ; Vin (3) where m is the ratio between the signal amplitude after and before attenuation of one step, which is 0.63 in this case. Only one pair of switches is switched on so that the attenuation of the input signal is several times of one attenuation step in decibel. The attenuation step is determined by the ratio between resistors, which is insensitive to process and temperature variation. An extra 2 dB step (which is not shown in Fig. 2) is implemented for gain calibration over process and temperature variations. 4.2. Fine gain control stage circuit design Cherry–Hooper amplifier is one of the most common circuit designs for broadband applications. It consumes a smaller area than the amplifier with a load inductor and consumes less power than the fT doublerŒ7 . A distributed amplifier provides a larger bandwidth, but the gain fluctuates within the cut-off frequency, which is undesirable for PGAs in HDD read channels. 035004-2 J. Semicond. 2014, 35(3) Lin Nan et al. Fig. 4. Topology of Cherry-Hooper amplifier. The proposed topology of the Cherry–Hooper FGC is illustrated in Fig. 4, where C1 and C2 are the total capacitance at the nodes. The transfer function of the FGC is given as Vout AV0 !n2 D 2 ; Vin s C 2!n s C !n2 (4) where gm1 gm2 D ; Rf 1 1 1C C C gm2 R1 R2 gm2 R2 gm2 R1 gm1 Rf AV0 D s C1 R1 C C2 R2 C C2 R1 R2 C1 R1 R2 C Rf Rf ; R2 gm2 R1 R2 R1 C C 2 C1 C2 R1 R2 1 C Rf Rf Rf !n2 D 1C R1 R2 gm2 R1 R2 C C Rf Rf Rf : C1 C2 R1 R2 (5) (6) (7) The bandwidth of the amplifier determined by Eq. (7) can be extended by increasing gm2 , while the DC gain determined by Eq. (5) is insignificantly affected. Since the gain of FGC is controlled by only varying gm1 , !n in Eq. (4) is invariable at different gains, which maintains a constant bandwidth within the variable gain range. The circuit design of the FGC is shown in Fig. 5. A binary switchedŒ5 variable transconductance array is in parallel with the first stage of the Cherry–Hooper amplifier to provide precise gain control. Each unit cell of the array consists of a switchable tail current source and a differential input pair. Since the operational points of the unit cell are constant with different gain settings, the current density of the input pairs remains constant at different gains to improve the linearity of the amplifierŒ8 . A variable transconductance array with seven control bits is sufficient to provide a gain step of 0.1 dB and a gain error of less than 0.05 dB by simulation. The transconductance gm1 is therefore given by p (8) gm1 D 2ˇ1 I1 20 b0 C 21 b1 C C 26 b6 C k ; where bi (0 6 i 6 6) is the control bit and k the constant. The gain of the variable gain stage is controlled by referring to a look-up table, in which the control bits are arranged to provide decibel-linear gain variation. The variable range of the FGC is 2 dB larger than the attenuation step to calibrate gain change caused by process corner and temperature variations. At start-up, if the gain of the fixed gain stages is smaller than desired, the gain of the PGA with zero attenuation is compared to 20 dB and 16 dB (which can be generated by an operational amplifier with a feedback network), by which the maximum value and minimum value of the look-up table is determined, respectively. If the gain of the fixed gain stages is larger than desired, the gain of the PGA with 2 dB attenuation is compared to 20 dB and 16 dB to set the maximum and minimum value of the look-up table. Hence the gain of the open-loop PGA and the variable range of FGC are constant at different corners and temperatures. A conventional dB-linear PGA employs pseudo exponential functionsŒ3 5 . The gain error, which is more than 0.5 dB, is limited by the intrinsic error of these functions. In the proposed PGA, the variable gain range of the FGC is limited by the step size of the attenuator to reduce the number of unit transconductance cells needed. Then the voltage gain is controlled by referring to a look-up table, which controls the gain to directly approximate the dB-linear function. The approximation is done by comparing Eq. (5) and the dB-linear gain function on the computer, which generates the control bits in the look-up table. Thus the systematic error brought by pseudo exponential functions is eliminated. The transconductance of the unit cell of the variable transconductance array determines the maximum error between the gain control function and the ideal dBlinear function. Hence, the gain error is limited to 0.05 dB with a proper unit cell design. The device dimension of the variable transconductance array is determined by the statistical error analysis of binaryweighted arrayŒ9 , which achieves a yield of 99.7% with proper device dimensions. Furthermore, the layout of the variable transconductance array is centro symmetrically distributed to lower the gain error brought by process gradient over the chip. Simulation results shows that the gain error variation is less than 5% across corner and temperature variations, which is sufficient in this application. Since the maximum gain of the PGA is only 20 dB, the DC offset cancellation circuit is not implemented. Simulation results show that the gain variation caused by an input offset voltage up to 20 mV can be tolerated by the excess gain variable range of FGA. 4.3. Fixed gain amplifier circuit design Although Cherry–Hooper is suitable for high speed applications, the bandwidth advantages begin to degrade with large signal amplitudes. Hence, the Cherry–Hooper amplifier is no longer useful for the last few stages. A single stage open-loop amplifier consumes more area, but it provides a high speed characteristic for both small and large signal amplitudes. Also, its power consumption is smaller than fT doubler and distributed amplifier. As a result, a single stage amplifier with a load inductor is placed at the output stage of the PGA as a fixed gain amplifier to provide sufficient total gain. Figure 6 depicts the schematic of the FGA. A symmetric inductor is implemented as part of the load of the amplifier to create peaking and improve the bandwidth. Negative Miller ca- 035004-3 J. Semicond. 2014, 35(3) Lin Nan et al. Fig. 5. Schematic of the FGC. Fig. 7. Micrograph of the proposed PGA. Fig. 6. Schematic of the FGA. pacitorsŒ10 are added to cancel the parasitic capacitance of the input transistors. A common-mode feedback (CMFB) circuit is implemented to stabilize the DC level of the signal. 5. Measurement results The micrograph of the chip is depicted in Fig. 7. The proposed PGA, occupying an active area of 0.22 mm2 , is fabricated in 0.13 m CMOS technology. An Agilent E5071B network analyzer was used for gain measurements by measuring the S21 parameter of the PGA. Figure 8 shows that the PGA provides a variable gain range of 24 dB from 4 to 20 dB with a gain error of less than ˙0.05 dB. Since the variable gain range of the PGA is divided by the attenuator with 4 dB per step, the deviation from ideal dB-linear gain function is repeated in every 4 dB gain variable range of the FGC. The measured 3-dB bandwidth is constant at 3.8 GHz, as depicted in Fig. 9. The input-referred third-order intercept points (IIP3) are 5 dBm and 17 dBm at the maximum and minimum gain of the PGA, respectively, as illustrated in Fig. 10. The noise figure (NF) of the PGA is measured at maximum gain with the Agilent E4440A spectrum analyzer. Table 1 shows the overall performance and a comparison with other recently published VGA and PGA with wide bandwidth and high gain accuracy. The Cherry–Hooper VGA proposed in Ref. [11] exhibits low power consumption and small area but it suffers from poor linearity and insufficient bandwidth. The VGA proposed in Ref. [14] shows a larger bandwidth, but it is realized by non-CMOS technology and the power consumption is much higher. The proposed PGA shows the best performance in bandwidth and gain accuracy with moderate linearity, area 035004-4 J. Semicond. 2014, 35(3) Reference Process Lin Nan et al. IIP3 (dBm) Ref. [2] 0.13 m CMOS 600 0–24 0.1 0:03 to 0.08 0.84–22.8 NF @ max gain (dB) Area (mm2 ) Supply voltage (V) Power (mW) — 0.3 1.2 16 Bandwidth (MHz) Gain (dB) Gain step (dB) Gain error (dB) Table 1. Performance summary and comparison to state-of-art. Ref. [11] Ref. [12] Ref. [13] Ref. [14] 90 nm 90 nm 0.18 m 0.13 m CMOS CMOS CMOS SiGe BiCMOS 2200 1000 900 7500 10 to 50 0.1–19.6 39 to 55 10 to 30 — 0.9 — — — 0.7 ˙3 — IP-1dB D to 13 17 0.01 1 2.5 55 < 5.6 IP-1dB D to 11 6.8 0.42 1.8 20.5 — 0.16 1 10.8 59 — This work 0.13 m CMOS 3800 4 to 20 0.1 0:05 to 0.04 5 to 17 — 0.14 1.2 50 10 0.22 1.2 20.4 Fig. 8. Measured voltage gain and gain error versus gain setting. Fig. 9. Measured frequency response at different gains. and power consumption. Fig. 10. Measured IIP3 at different gain. (a) gain D 20 dB. (b) gain D 4 dB. 6. Conclusion A linear-in-decibel open-loop PGA with low gain error and wide bandwidth is introduced in this paper and implemented in 0.13 m CMOS technology. The two-stage gain control topology and open-loop circuit design provide a small gain step and a large bandwidth. The special gain control scheme and layout design guarantee a low gain error. The variable voltage gain range of the PGA is from 4 to 20 dB with a gain step of 0.1 dB and a gain error of less than ˙0.05 dB. The mea- 035004-5 J. Semicond. 2014, 35(3) Lin Nan et al. sured bandwidth is constant at 3.8 GHz and the IIP3 is from 5 to 17 dBm. References [1] Yoo S J, Ravindran A, Ismail M. A low voltage CMOS transresistance-based variable gain amplifier. IEEE International Symposium on Circuits and Systems, 2004: 809 [2] Lin N, Fang F, Hong Z L, et al. A CMOS broadband precise programmable gain amplifier with bandwidth extension technique. IEEE Asian Solid-State Circuits Conference, 2011: 225 [3] Duong Q H, Le Q, Kim C W, et al. A 95-dB linear low-power variable gain amplifier. IEEE Trans Circuits Syst I, Regular Papers, 2006, 47(8): 1648 [4] Nguyen H H, Duong Q H, Lee S G. 84 dB 5.2 mA digitallycontrolled variable gain amplifier. Electron Lett, 2008, 44(5): 344 [5] Nguyen H H, Nguyen H N, Lee J S, et al. A binary-weighted switching and reconfiguration-based programmable gain amplifier. IEEE Trans Circuits Syst II, Express Briefs, 2009, 56(9): 699 [6] Calvo B, Celma S, Aznar F, et al. Low-voltage CMOS programmable gain amplifier for UHF applications. Electron Lett, 2007, 43(20): 1087 [7] Lazavi B. Design of integrated circuits for optical communications. Boston: McGraw-Hill, 2003 [8] Iwon K, Lee K. An accurate behavioral model for RF MOSFET linearity analysis. IEEE Microw Wireless Compon Lett, 2007, 17(12): 897 [9] Bastos J, Steyaert M, Sansen W. A high yield 12-bit 250-MS/s CMOS D/A converter. IEEE Custom Integrated Circuits Conference, 1996: 431 [10] Haines G W, Mataya J A, Marshall S B. IF amplifier using Cc compensated transistors. ISSCC Dig Tech Papers, 1968: 120 [11] Wang Y, Afshar B, Cheng T Y, et al. A 2.5 mW inductorless wideband VGA with dual feedback DC-offset correction in 90 nm CMOS technology. IEEE RFIC Symp Dig, 2008: 91 [12] D’Amico S, Spagnolo A, Donno A, et al. A 9.5 mW analog baseband RX section for 60 GHz communications in 90 nm CMOS. IEEE RFIC Symp Dig, 2011: 1 [13] Lee H D, Lee K A, Hong S. A wideband CMOS variable gain amplifier with an exponential gain control. IEEE Trans Microwave Theory Tech, 2007, 55(6): 1363 [14] Liu Chang, Yan Yuepeng, Goh Wangling, et al. A 10-Gb/s inductor-less variable gain amplifier with a linear-in-dB characteristic and DC-offset cancellation. Journal of Semiconductors, 2012, 33(8): 085003 035004-6