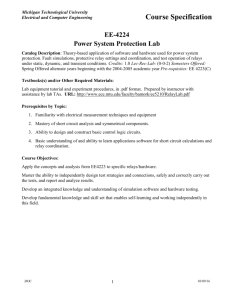

Relay Scheme Design Using Microprocessor Relays

advertisement