Isolated Zeta Converter: Principle of Operation and Design

advertisement

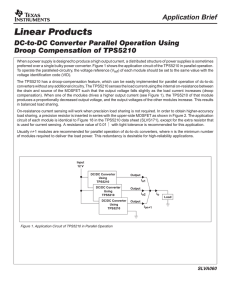

WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn Isolated Zeta Converter: Principle of Operation and Design in Continuous Conduction Mode PIJIT KOCHCHA, SARAWUT SUJITJORN* School of Electrical Engineering, Institute of Engineering Suranaree University of Technology 111 University Avenue, Muang District, Nakhon Ratchasima, 30000 THAILAND pijit_sut@hotmail.com * corresponding author: sarawut@sut.ac.th Abstract: - The principle of operation of the zeta converter is explained in the article. Small-signal and steady-state models of the converter are presented. The design formulas for the continuous conduction mode (CCM) are given together with some design examples and simulation results. The power factor and harmonic issues are also addressed. Key-Words: - zeta converter, continuous conduction mode (CCM), harmonic, power factor. Section 3 presents an overview of the state-space averaging technique, while the transfer function model can be found in Section 4. Section 5 presents the steady-state time-domain model in CCM. Section 6 provides design examples, simulation results with discussions. The harmonic, and power factor issues are also discussed. Conclusion follows in Section 7. 1 Introduction Vast majority of power converters used nowadays employ front-end diode bridge rectifiers. Such rectifiers draw pulsating currents which leave behind a great amount of harmonics, and considerably low power factor. For a single converter of this type used with a single-phase load such as in a consumer electronic equipment, the problems may not seem serious. However, a great number of those equipments in parallel connection at a point of common coupling (PCC) to draw power simultaneously introduce some serious effects concerning reactive power and harmonic. The situations are quite common in offices and industries. Several types of AC-DC converters have been introduced to achieve the demanded power conversion, and the less problems on harmonic and power factor [1]. To name a few, these include the Cuk converter [2], the Sepic converter [3]-[6], the combined boost with double winding flyback converter [7], and the zeta converter [8]-[13]. Among those, the zeta converter, which is originally the buck-boost type, can be regarded as a flyback type when an isolated transformer is incorporated. An isolated zeta converter has some advantages including safety at the output side, and flexibility for output adjustment [14]-[16]. This article describes the operation principle of the isolated zeta converter in the CCM in Section 2. ISSN: 1109-2734 2 Principle of Operation Fig.1(a) depicts the circuit diagrams of the isolated zeta converter such that its operation principle in the CCM could be readily explained. Fig.1(b) represents the 1st region of operation in which the switch S is “on”, and the diode D is “off”. This region takes the time from 0 to d1Ts seconds. The inductor Lm stores the energy received from the rectifier. The capacitor C1 supplies energy to the load (R) via the inductor Lo, and the capacitor Co. the currents through the inductors Lm and Lo increase linearly, while no current flows through the diode. Fig.1(c) represents the 2nd operation region in which the switch S is “off”, and the diode D is “on”. This region begins at the time d1Ts seconds, and ends by d2Ts seconds. The diode D is forward biased due to the voltage across the inductor Lm has reversed polarity, while the currents iLm and iLo decrease linearly. The stored energy in the inductor Lm is transferred to the capacitor C1. The load R 483 Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn ig + + is Lo +vLo − Co −vC1 + vLm Lm vs C1 1: n − vg + + vCo R Vo − − S − (a) an isolated zeta converter ip ig is vs + iC1 1: n iLo ig io + iLm iD iCo R + is vs 1: n iC1 iLo io + iLm Vo − vg ip iD iCo − vg − − (b) region 1 of operation (c) region 2 of operation Fig.1 Circuit diagrams of the isolated zeta converter. S S ON OFF Vg iLm ∆iLm − Lm ON t OFF t t iLo nvg + vC1 − vo ∆iLo Lo t vg vLm vC1 nLm v − o Lo vLo vC1 n nvg + vC1 − vo t t iC1 − − nvg + vC1 − vo vC1 n 2 Lm Lo ig vg Lm + n ( nvg + vC1 − vo ) t v v − 2C1 − o n Lm Lo iD v − o Lo nvg + vC1 − vo Lo d1Ts vo Lo t iCo Ts t t d1Ts d 2Ts Ts d 2Ts Fig.2 Current and voltage waveforms. ISSN: 1109-2734 484 R Vo Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn X = − Aav −1 BavU receives energy from the inductor Lo. Hence, the current iD=iC1+iLo. Fig.2 illustrates the steady-state current and voltage waveforms in one switching cycle. These curves will be referred to for the development of the design formulas. 3 Overview of The Averaging Technique Under small-signal assumption, taking the Laplace transform to Eq. (3) results in State-Space xɺ ( s ) = [ sI − Aav ] Bav vɶg ( s ) −1 + ( A1 − A2 ) X + ( B1 − B2 )Vg dɶ1 ( s ) Considering the operation of the converter during the on- and off-time intervals denoted as ton or d1Ts , and toff or (1 − d1 ) TS , respectively, the equations in one switching cycle can be written as Finally, one can obtain the following transfer functions: for nvɶg = 0 yɶ ( s ) −1 = Cav [ sI − Aav ] ( A1 − A2 ) X + ( B1 − B2 )Vg ɶ d1 ( s ) (1) y = Cs x (5). yɶ ( s ) = Cav xɶ ( s ) + ( C1 − C2 ) X dɶ ( s ) state xɺ = As x + Bs u (4) Y = −C av Aav −1 Bav . U (6) + ( C1 − C2 ) X , where , and for dɶ1 = 0 As = [ A1d1 + A2 (1 − d1 )], Bs = [ B1d1 + B2 (1 − d1 )], Cs = C1d1 + C2 (1 − d1 ) . yɶ ( s ) −1 = Cav [ sI − Aav ] Bav ɶvg ( s ) Linearization can be made to the above equations by considering small-signal perturbations such that x = X + xɶ , y = Y + yɶ , d1 = D1 + dɶ1 , u = U + uɶ where X >> xɶ , Y >> yɶ , U >> uɶ and D >> dɶ be 1 4 Transfer Function Models Referring to the circuit in Fig. 1(a), the parameters transferred from the secondary onto the primary side are 1 substituted into Eq. (1). Under the steady-state condition of the state variables, one may write the following equations X = Aav X + BavU = 0 Y = Cav X vo′ = vo n , Lo′ = Lo n 2 , C1′ = n 2 C1 , Co′ = n 2Co , R′ = R n 2 . (2) According to the operation in one switching cycle, the circuit equations can be written as , and xɺ = Aav xɶɺ + ( A1 + A2 ) X + ( B1 + B2 )U dɶ + Bav uɶ yɶ = Cav xɶ + ( C1 − C2 ) X dɶ v diLm ( t ) Vg = ( d1 ) − C1′ (1 − d1 ) dt Lm Lm (3) diLo′ ( t ) dt dvC1′ ( t ) , where Aav = A1 D1 + A2 (1 − D1 ) , Bav = B1 D1 + B2 (1 − D1 ) , dt dvCo′ ( t ) Cav = C1 D1 + C2 (1 − D1 ) . dt = n 2Vg Lo =− = ( d1 ) + n 2 vC1′ Lo ( d1 ) − n 2 vCo′ Lo iLo′ i ( d1 ) + 2Lm (1 − d1 ) 2 n C1 n C1 v iLo′ − Co′ 2 n Co RCo vo′ = vCo′ . From Eq. (2), Eq. (4) below are obvious. ISSN: 1109-2734 (7). 485 Issue 7, Volume 9, July 2010 (8) WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn Let the state, input and output vectors be represented by x = iLm′ 0 iɺɶ Lm 0 iɺɶLo′ ɺ = vɶC1′ (1 − D1 ) vɺɶ′ n 2C1 o 0 T iLo′ vo′ , u = vg , y = vo′ , vC1′ the coefficient matrices of the state-variable models can be obtained as 0 0 Aav = (1 − D1 ) n 2C1 0 D Bav = 1 Lm − 0 (1 − D1 ) Lm 2 n D1 Lo 0 − D1 n 2 C1 0 1 n Co 0 2 0 0 n 2 D1 Lo 2 n − Lo 0 1 − RCo (9) (10) (11). By substituting Eqs. (9)-(11) into Eq. (4), the following steady-state relations can be obtained n D1 2 R (1 − D1 ) I Lm n 2 D 1 I Lo′ = R (1 − D1 ) V g VC1′ D1 Vo′ (1 − D1 ) D1 (1 − D ) 1 2 2 Lm n D1 Lo 0 − D1 n 2C1 0 1 n Co 0 2 0 0 − dɶ1 n 2C1 0 n 2 iɶLm − Lo iɶLo′ vɶ C1′ 0 vɶo′ 1 − RCo dɶ − 1 0 Lm I 2 ɶ Lm n d1 0 I Lo′ Lo V C1′ 0 0 Vo′ 0 0 0 Vg Lm n 2V g + dɶ1 Lo 0 0 (13) iɶLm ɶ i ɺ vɶo′ = [ 0 0 0 1] Lo′ vɶC1′ vɶo′ (14). The transfer function models of the isolated zeta converter can be derived from the above Eqs. (13)(14), and obtained as (12). Vo′ D1 = Vg (1 − D1 ) Gvd ( s ) = vɶo′ ( s ) dɶ1 ( s ) = 1 Gvv ( s ) = The small-signal models as shown in Eqs. (13)-(14) can be obtained from substituting Eqs. (9)-(11) into Eq. (5). ISSN: 1109-2734 (1 − D1 ) 2 D1 0 L m n 2 D1 0 + vɶg + Lo ɶ 0 d1 n 2C1 0 0 0 T Cav = [ 0 0 0 1] − 0 2 (15) avv s 2 + bvv as 4 + bs 3 + cs 2 + ds + e (16) vɶo′ ( s ) vɶg ( s ) = 486 (1 − D1 ) avd s 2 + bvd s + cvd as 4 + bs 3 + cs 2 + ds + e 1 (1 − D1 ) 2 Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn , where avd = n 2 RLm C1Vg (1 − D1 ) , bvd = −n 2 D12 LmVg , cvd = RVg (1 − D1 ) iCo ∆Q 2 avv = n 2 D1 RLmC1 , bvv = D1 (1 − D1 ) R Ts 2 Ts a = n RLm Lo C1Co , b = n Lm Lo C1 2 ∆iCo ∆iCo t 2 2 c = RLo Co (1 − D1 ) + n 2 D12 RLmCo + n 2 RLm C1 2 Fig. 3 The current iCo waveform. d = Lo (1 − D1 ) + n 2 D1 Lm , e = R (1 − D1 ) . 2 2 The voltage ripple ∆VC1 can be expressed as 5 Steady-State Models ∆VC1 = Referring to the waveforms in Fig. 2 and the analysis principle presented in [17], the steady-state models of the isolated zeta converter in CCM can be developed as follows. The turn-on and turn-off times (ton and toff) can be expressed as L ∆i L ∆i ton = d1Ts = m Lm = o Lo Vg nVg toff From Eq. (23) and i = C1 = (17) nL ∆i L ∆i = (1 − d1 ) Ts = m Lm = o Lo VC1 Vo Co = (19) M n+M (20). 1 = ton + toff , and from fs Eqs. (17)-(19), one may derive the current ripple terms obtained as ∆iLo = VgVC1 f s Lm (VC1 + nVg ) nVgVo f s Lo (Vo + nVg ) ISSN: 1109-2734 = = Vg d1 f s Lm nVg d1 f s Lo (24). Vo (1 − d1 ) 8 f s 2 Lo ∆VCo (25). Designing the isolated zeta converter in the CCM requires the knowledge of critical inductances denoted as Lmc and Loc . Based on the assumptions of lossless and the average load current being equal to the average current in Lo , the terms Loc and Lmc can be found as follows: Due to the fact that Ts = ∆iLm = Vo d1 f s R∆VC1 6 Design Examples , and the duty cycle d1 = Vo , one can obtain R (2)-(3), and the fact that ∆VCo = ∆Q Co , one may derive (18). can obtain the voltage gain Vo nd1 = Vg (1 − d1 ) (23). Referring to the waveforms of iCo and iLo in Figs. Since the voltage VC1 = nVg d1 (1 − d1 ) = Vo , one M= i dT 1 d1Ts 1 d1Ts iC1dt = ∫ io dt = o 1 s ∫ 0 0 C1 C1 C1 (21) Loc = (1 − d1 ) R 2 fs (26) Lmc = (1 − d1 ) 2 R 2 n 2 f s d1 (27) The design criteria are that Lo ≥ Loc , Lm ≥ Lmc , (22). C1 ≥ 487 V (1 − d1 ) Vo d1 , and Co ≥ o 2 to achieve f s R∆VC1 8 f s Lo ∆VCo Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn %γ ≤ 1% and ∆VC1 = ∆VCo = 2 3γ Vo . The formulas dignify the smallest components possible. In practice, the output qualities must be considered for a proper component sizing. Let us consider the requirement that the converter produces the average output voltage of 105 Vdc, and the current of 2.1 Adc from the ac input of 311 Vpk, 50 Hz. The first step is to calculate the gain M = Vo Vg = 105 311 = 0.3376 , the duty cycle Table 1 Design results (converter with an R load). d1=0.6280, and the turns ratio n. Then select the switching frequency fs. The expressions (26) and (27) are used next to obtain the inductances Lo and Parameters Values peak input voltage (Vg) 311 V 50 Hz avg. output voltage (Vo) 105 V avg. output current (Io) 2.1 A switching frequency (fs) 50 kHz Lm , Lo 3 mH, 200 uH C1 , Co 20 uF, 1.41 mF turns ratio Lm as follows: 0.2 of hf transformer (n) Lo ≥ (1 − d1 ) R (1 − 0.6280)(50) = 2 fs 2(50 × 103 ) = 186 µ H duty cycle (d1) 0.6280 M 0.3376 (1 − 0.6280 ) ( 50 ) (1 − d1 ) 2 R Lm ≥ = 2 2 2 n f s d1 2 ( 0.2 ) ( 50 × 103 ) ( 0.6280 ) 2 = 2.75mH . Thus, the chosen inductances are Lo = 200 µ H , and Lm = 3mH . The capacitances Co and C1 are calculated according to Eqs. (24) and (25), and obtained as Co ≥ Vo (1 − d1 ) 8 f s Lo ∆VCo 2 = (105 )(1 − 0.6280 ) 8 ( 50 × 103 ) ( 200 × 10−6 ) (1.82 ) 2 (a) source voltage and current waveforms = 5.36 µ F C1 ≥ (105)( 0.6280 ) Vo d1 = f s R∆VC1 ( 50 × 103 ) ( 50 )(1.82 ) = 14.49µ F The design results are summarized by Table 1. (b) output voltage and current waveforms Fig. 4 Simulation results (R load, without LC filter). ISSN: 1109-2734 488 Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn 5(b)-(c) show the simulation results indicating that the output transient peaks are well suppressed, and the outputs become steady in a short time. The average outputs of 105.35 Vdc , and 2.11 Adc are obtained. At PCC, the current harmonic distortion is reduced to 30.81 % THDi, and the power factor is as high as 0.9096 (lagging). Let’s consider another design example where the load of the converter is a series RL. This can be a good representation of a motor load in steady-state operation. The zeta converter has 220V (311 peak voltage), 50Hz supply. Its load is assumed to be 23.7 mH series with an R, 800W, 11A rated. Firstly, the equivalent load resistance, and the average output voltage can be calculated as Po I o 2 = 800/112 = 6.6116 Ω, and Po I o = 800/11 = 72.73 Vdc, respectively. The voltage gain and the duty cycle are M = Vo Vg = 72.73 311 = 0.2339 , and d1 = 0.5391, The simulation results using PSIM are illustrated in Fig. 4. Very large transient voltage can be observed, and later suppressed by an LC filter. The average output voltage and current are 105.48 Vdc , and 2.11 Adc, respectively. A high current harmonic of 123.53 % THDi, and a low power factor of 0.6270 (lagging) are observed at the PCC. 1: n Lo + Lf vs C1 Lm Co R Vo − Cf (a) zeta converter with the LC-filter respectively. The expressions (26) and (27) are used next to obtain the inductances Lo and Lm as follows: Lo ≥ (1 − d1 ) R (1 − 0.5391)(6.6116) = 2 fs 2(50 × 103 ) = 30.47 µ H (1 − 0.5391) ( 6.6116 ) (1 − d1 ) 2 R = 2 2 2 n f s d1 2 ( 0.2 ) ( 50 × 103 ) ( 0.5391) 2 Lm ≥ = 651.31µ H . (b) source voltage and current waveforms Thus, the chosen inductances are Lo = 40 µ H , and Lm = 700 µ H . The capacitances Co and C1 are calculated according to Eqs. (24) and (25), and obtained as Co ≥ Vo (1 − d1 ) 8 f s Lo ∆VCo 2 = ( 72.73)(1 − 0.5391) 2 8 ( 50 × 103 ) ( 40 × 10−6 ) (1.26 ) = 43.66 µ F C1 ≥ (c) output voltage and current waveforms = 94.14 µ F Fig. 5 Simulation results (R load, with LC filter). An LC filter designed by a conventional method (Lf = 100 mH, Cf = 137 nF) is incorporated into the converter as shown by the diagram in Fig. 5(a). Figs ISSN: 1109-2734 ( 72.73)( 0.5391) Vo d1 = f s R∆VC1 ( 50 × 103 ) ( 6.6116 )(1.26 ) Table 2 summarizes the case. 489 Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn The voltage and current waveforms obtained from PSIM are illustrated in Fig. 7. With the assumed RL load, the average output voltage and current of the converter are 72.83 Vdc, and 10.93 Adc, respectively, according to the expectation. Without a filter, the current harmonic is as high as 143%, and the power factor is 0.5844 (lagging). An LC filter having Lf = 50 mH and C f = 137 nF is added to the input frontend. The duty cycle is also increased to 0.5861 to compensate for the associated voltage drop. The simulation results indicate that the average output voltage is 72.34 Vdc, the average output current is 10.86 Adc, with 28.83 %THDi and power factor of 0.8842 (lagging). It is observed that the LC filter significantly decreases the pulsation of the source current, in turn drastically reduces the harmonic distortion, and increases the power factor of the circuit. Table 2 Design results (converter with an RL load). Parameters Values peak input voltage (Vg) 311 V 50 Hz avg. output voltage (Vo) 72.73 V avg. output current (Io) 11 A switching frequency (fs) 50 kHz Lm , Lo 700 uH, 40 uH C1 , Co 100 uF, 4.4 mF turns ratio 0.2 of hf transformer (n) duty cycle (d1) 0.5391 M 0.2339 (a) source voltage and current waveforms (a) source voltage and current waveforms (b) output voltage and current waveforms (b) output voltage and current waveforms Fig. 8 Simulation results (RL load, with LC filter). Fig. 7 Simulation results (RL load, without LC filter). ISSN: 1109-2734 490 Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS Pijit Kochcha, Sarawut Sujitjorn 7 Conclusion This paper has explained the principle of operation of the zeta converter with the design formulas for the continuous current mode (CCM) of operation. It also presents the development of the state-variable, and the transfer function models of the isolated zeta converter. Two design examples are given for the cases of R, and series RL loads. Detailed simulation results are presented, and the following conclusions are drawn: (i) the output voltage and current contain a considerable amount of ripples which have to be limited in practice, (ii) the converter without an input filter produces a great deal of current harmonic, and possesses a low power factor, and (iii) a simple LC input-filter can be used at first sight to reduce the harmonic, and to increase the power factor. The issues concerning the discontinuous current mode (DCM), the control of the output power, the power factor correction, and the harmonic reduction are under investigations. [7] [8] [9] [10] [11] Acknowledgements The authors are thankful to the Mechatronics Program-SUT for financial supports of the project. The first author’s thank is due to SUT for the doctoral scholarship. [12] [13] References [1] B. Singh, B.N. Singh, A. Chandra, K. AlHaddad, A. Pandey, and D.P. Kothari, “A review of single-phase improved power quality AC-DC converters,” IEEE Trans. Industrial Electronics, vol.50, pp.962-981, 2003. [2] C. Wu, “Evaluation and implementation of the optimum magnetics design of the Cuk converter in comparison to the conventional buck-boost converter,” IEEE Trans. Magnetics, vol.18, pp.1728-1730, 1982. [3] J.J. Jozwik, and M.K. Kazimierczuk, “Dual sepic PWM switching-mode DC/DC power converter,” IEEE Trans. Industrial Electronics, vol.36, pp.64-70, 1986. [4] D.C. Martins, and A.H. de Oliveira, “Isolated three-phase rectifier using a Sepic DC-DC converter in continuous conduction mode for power factor correction,” WSEAS Trans. Circuits, vol. 2, no. 1, pp. 13-19, 2003. [5] E. Niculescu, D-M. Purcaru, and M.C. Niculescu, “A steady-state analysis of PWM Sepic converter,” 10th WSEAS International Conference on Circuits, pp. 217-222, 2006. [6] E. Niculescu, M.C. Niculescu, and D-M. Purcaru, “Modelling the PWM Sepic converter in discontinuous conduction mode,” 11th ISSN: 1109-2734 [14] [15] [16] [17] WSEAS International Conference on Circuits, pp. 98-103, 2007. D. Cismasiu, V. Popescu, and D. Lascu, “Single-stage PFC power supply with universal input and automatic voltage clamping,” 11th WSEAS International Conference on Circuits, pp. 109-114, 2007. D.C. Martins, and G.N. de Abreu, “Application of the Zeta converter in switch-mode power supplies,” Conference and Exposition, Applied Power Electronics, APEC., pp.214-220, 1993. A. Peres, D.C. Martins, and I. Barbi, “Zeta converter applied in power factor correction,” Power Electronics Specialists Conference, PESC., vol.2, pp.1152-1157, 1994. D.C. Martins, “Zeta converter operating in continuous conduction mode using the unity power factor technique,” Sixth International Conference, Power Electronics and Variable Speed Drives, pp.7-11, 1996. D. Cruz Martins, F. de Souza Campos, and I. Barbi, “Zeta converter with high power factor operating in continuous conduction mode,” IEEE IECON 22nd International Conference, Industrial Electronics, Control, and Instrumentation, vol.3, pp.1802-1807, 1996. C. Sudhakarababu, and M. Veerachary, “Zeta converter for power factor correction and voltage regulation,” IEEE Region 10 Conference ,TENCON., vol.4, pp.61-64, 2004. E. Vuthchhay, C. Bunlaksananusorn, and H. Hirata, “Dynamic modeling and control of a zeta converter,” International Symposium, Communications and Information Technologies, ISCIT. pp.498-503, 2008. S. Ang, and A. Oliva, Power-Switching Converter (2nd ed.). United States of America: CRC Press, pp.129-130, 2005. T. Suntio, Dynamic Profile of Switched-Mode Converter. WILEY-VCH Verlag GmbH & Co., 2009. J-L. Lin, S-P. Yang, and P-W. Lin, “Smallsignal analysis and controller design for an isolated zeta converter with high power factor correction,” Electric Power Systems Research, vol.76, pp.67-76, 2005. M.H. Rashid, Power Electronics: Circuits, Devices and Applications (3rd ed.). PearsonPrentice Hall, pp.186-203, 2004. LIST OF SYMBOLS d1 d2 fs iC1 iCo iD 491 = = = = = = “on” duty cycle of switch S “off” duty cycle of switch S switching frequency (Hz) current of capacitor C1 (A) current of capacitor Co (A) current of diode D (A) Issue 7, Volume 9, July 2010 WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS ig iLm iLo io ip is n = = = = = = = M = THDi Ts iLm iLo VC1 VCo γ = = = = = = = output current of rectifier (A) current of inductance Lm (A) current of inductance Lo (A) output current (A) primary current of transformer (A) input current (A) turns ratio of high frequency transformer voltage of capacitor C1 (V) output voltage of rectifier (time domain), peak value (V) voltage of inductance Lm (V) voltage of inductance Lo (V) output voltage (time domain), average value (V) sinusoidal source voltage (V) transfer function of duty cycle to output voltage transfer function of input to output voltages voltage gain of peak input to output voltages total harmonic current distortion switching period (s) current ripple of inductor Lm (A) current ripple of inductor Lo (A) voltage ripple of capacitor C1 (V) voltage ripple of capacitor Co (V) output ripple factor = small-signal perturbation = transferred circuit parameters from secondary to primary vC1 = vg, Vg = vLm = vLo = vo, Vo = vs = Gvd(s) = Gvv(s) = ISSN: 1109-2734 Pijit Kochcha, Sarawut Sujitjorn 492 Issue 7, Volume 9, July 2010