Analysis of Radiation Emission from Ground Plane Structure

advertisement

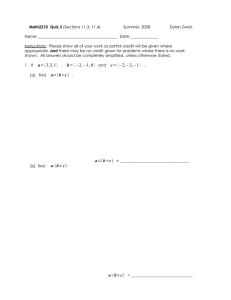

International Journal of Emerging Trends & Technology in Computer Science (IJETTCS) Web Site: www.ijettcs.org Email: editor@ijettcs.org, editorijettcs@gmail.com Volume 2, Issue 4, July – August 2013 ISSN 2278-6856 Analysis of Radiation Emission from Ground Plane Structure S.Kannadhasan1 N.SivaKumar2 V.B Bhapith3 R.Ragavendra4 1,2,3,4 Assistant Professor, Raja College of Engineering and Technology, Madurai, TamilNadu, India ABSTRACT----High-Speed multilayer printed circuit boards have been used to the ground plane structure modified to improve electrical performance and reduce size of a micro strip circuit. The signal current through the ground plane, which causes undesired effects such as signal distortion, crosstalk and radiation. The digital circuit’s printed circuit board (PCB) layout design plays a crucial role in emission mitigation technique. The Ground plane structure through a slot line are consider the propagation of transmitted and reflected waveforms will changed .The micro strip line or the strip line with a plane structures can greatly suppressed the radiation emission. In order to reduce the radiated emission from high speed board implement the various structures in HFSS and ADS Software for simulation. Analyze the simulation results by the slotted plane, solid plane, and split reference plane have compared the various Conventional structures with proposed method numerically and experimentally investigated the effects of the power/ground partitioning on the radiated emission. Keywords: Split plane, Ground Plane, Solid Plane, Slotted Plane 2. RELATED WORK Partitioning of the power/ground plane breaks the current return path of the signal current .Radiated noises decrease obviously circuit improvement. Effective & Efficient I/O minimize the effect of non ideal current return path-High-speed digital signal as Micro strip line. Micro strip line with a split reference plane should be avoided- greater influence on EMI Covered by Completed Ground Plane. 3. RADIATION FROM SIGNAL TRACES It is well known that the currents on micro strip transmission line on PCB can be separated into two parts electrically. The first part is the current flowing into the horizontal direction and the other one is the current flowing down to the vertical direction. The FR4 dielectric substrate is used, of which the dielectric constant is about 4.5. The characteristic impedance of the signal trace is designed to be 50 ohms, in order to match the signal impedance to the port impedance 3.1 Solid Plane In solid waveguide, ground planes are completely flat with micro-strip line structure. 1. INTRODUCTION Many mitigation techniques are available directly to the Power devices must be addressed for a design to pass FCC/CISPR emissions. EMI mitigation technique to implement PCB in a grounded chassis with filter elements limiting noise escaping on cable shields. Signal Integrity is“Timing” is everything in a high-speed system. Signal timing depends on the delay caused by the physical length that the signal must propagate. The goal of signal integrity analysis is to ensure reliable high-speed data transmission. The following techniques are effective in reducing EMI radiation and on-board noise: Input-to-output ground plane stitching capacitance Power control Edge guarding Interplane capacitive bypass The complexity of digital system increases with the improvement of system clock frequency and the development of various electronic devices generate unintentional electromagnetic interference and electromagnetic emission between the components, device, and PCB transmission lines. The reason of radiation phenomena from asymmetric and narrow ground planes is due to the common-mode current. In power systems, ground is commonly tied to earth and digital electronics ground is normally a reference potential. In a system with multiple return paths each ground may be at a slightly different potential. The potential different between grounds can cause many problems, some being noise, and others can prevent the system from operating normally. Different ground configurations can be used depending on the systems which perform better than others in terms of reducing noise. Volume 2, Issue 4 July – August 2013 Figure 1: Solid Plane Structure 3.2 Slotted Ground Plane In a slot waveguide, two ends of the slot are shorted in the slotted ground plane and the slot wave propagates along the slot with the major electric field component oriented across the slot in the plane of metallization on the dielectric substrate. The mode of propagation is non- transelectromagnetic (TEM) and almost transverse electric in nature. . Figure 2: Slotted Ground Plane Structure 3.3 Split Ground Plane In a Split Reference plane method two ends of the slot are opened in the split ground plane. For fast and comprehensive simulation of signal propagation, power/ground noise, and radiated emissions by combining the physics-based model. Page 219 International Journal of Emerging Trends & Technology in Computer Science (IJETTCS) Web Site: www.ijettcs.org Email: editor@ijettcs.org, editorijettcs@gmail.com Volume 2, Issue 4, July – August 2013 ISSN 2278-6856 Figure 3: Split Ground Plane Structure Figure 7: Split Reference Plane Pattern Figure 4: Novel patterns on the ground planes. Reduction of the radiated emission from the signal traces Table 1: Comparison of Various Structures Figure 8: Ground Plane Structure 5. CONCLUSION 4. RESULTS AND DISCUSSION By the simulation of conventional structures and proposed structure the Split reference plane structure reduce radiation rapidly. Solid Plane pattern reduce the radiation -39 dB in the solid structure shown in the figure 5. Slotted Plane pattern reduce the radiation -35 dB in the slotted structure shown in the figure 6. Split Reference pattern reduce the radiation -20 dB in the strip structure shown in the figure 7. Ground Plane reduce the radiation -15 dB in the strip structure shown in the figure 8. Power/ground partitioning - supply multi voltage levels to the PCB. Isolate power/ground noise between different parts of the high-speed multilayer PCB. Slot plane generates large amounts of the reflection and the radiated emission. In multilayer structures with many reference planes, the effects of ground slot vary greatly. Ground Pattern Structure is used to reduce the Radiated Emission. Proposed method can be extended to approximately 40–50 GHz. This competence allows replication of configurations with high complexity. The Ground plane structures have 15db lesser amount of radiation compared to the existing method. 6. REFERENCES Figure 5 : Solid Plane Pattern [1] Y. Ko, K. Ito, J. Kudo, and T. Sudo, “Electromagnetic radiation properties of a printed circuit board with a slot in the ground plane,” in Proc. IEEE Int. Symp. Electromagnetic Compatibility, 1999, pp. 576–579. [2] J. Fan, Y. Ren, and J. Chen et al., “RF isolation using power islands in DC power bus design,” in Proc. IEEE Int. Symp. Electromagnetic Compatibility, vol. 2, 1999, pp.ethod. 838–843. [3] J. R. Miller, “The impact of split power planes on package performance,” in Proc. IEEE Electronic Components Technology Conf., 2001. [4] H.-J. Liaw and H. Merkelo, “Signal integrity issues at split ground and power planes,” in IEEE Electronic Components and Technology Conf., 1996, pp. 752– 755. [5] K. C. Gupta, R. Garg, I. Bahl, and P. Bhartia, Microstrip Lines and Slotlines,2nd ed. Norwood, MA: Artech, 1996, ch. 5. Figure 6: Slotted plane Pattern Volume 2, Issue 4 July – August 2013 Page 220 International Journal of Emerging Trends & Technology in Computer Science (IJETTCS) Web Site: www.ijettcs.org Email: editor@ijettcs.org, editorijettcs@gmail.com Volume 2, Issue 4, July – August 2013 ISSN 2278-6856 [6] Hwang-Ywn Shim, Jiseong Kim, Jang-Gwan Yook "Modeling of ESD and EM1 problems in split multilayn power distribution network:' 2003 IEEE Inlernotiond Symporium on Eieclmmognelic compiibiiiIy, Vol. I, pp 48 - 51, Aug 2003. [7] T.-L.Wu, Y.-H. Lin, T.-K.Wang, C.-C.Wang, and S.T. Chen, “Electromagnetic bandgap power/ground planes for wideband suppression of ground bounce noise and radiated emission in high-speed circuits,”IEEE Trans. Microw. Theory Tech., vol. 53, no. 9, pp. 2935–2941, Sep. 2005. [8] J. Kim, H. Kim, W. Ryu, and J. Kim, “Effects of onchip and off-chip decoupling capacitors on electromagnetic radiated emission,” in Proc. Electron. Comp. Technol. Conf., Seattle, WA, May 25–28, 1998, pp. 610–616. [9] L. van Wershoven, “Characterization of an EMC test-chip,” in Proc. IEEE Int. Symp. Electromagn. Compat.,Washington, DC, Aug. 21–25, 2000, pp. 117–121. [10] K.-B. Wu, F.-S. Chang, and R.-B. Wu, “Design of shorting vias in alternative PCB planes for suppressing ground- bounce induced electromagnetic emission,” in Proc. IEEE 18th Topical Meeting Elect. Perform. Electro. Packag., Tigard, OR, Oct. 19–21, 2009, pp. 247–250. [11] E. X. Liu, E. P. Li, Z. Z. Oo, X. C. Wei, Y. J. Zhang, and R. Vahldieck,“Novel methods for modelling of multiple vias in multilayered parallelplatestructures,” IEEE Trans. Microw. Theory Tech., vol. 57, no. 7,pp. 1724–1733, Jul. 2009. [12] R. Ito, R.W. Jackson, and T. Hongsmatip, “Modelling of interconnectionsand isolation within a multilayered ball grid array package,” IEEE Trans. Microw. Theory Tech., vol. 47, no. 9, pp. 1819– 1825, Sep. 1999. [13] G. T. Lei, R. W. Techentin, P. R. Hayes, D. J. Schwab, and B. K. Gilbert,“Wave model solution to the ground/power plane noise problem,” IEEETrans. Instrum. Meas., vol. 44, no. 2, pp. 300–303, Apr. 1995. Volume 2, Issue 4 July – August 2013 Page 221