Analog and Mixed-Signal Products Analog Applications Journal

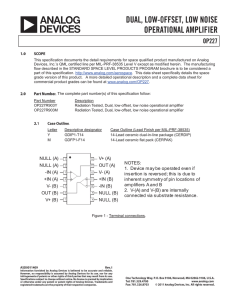

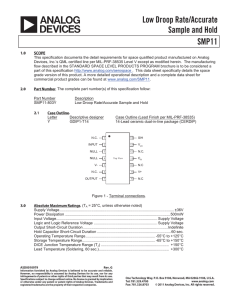

advertisement