exploration and design of sar logic for low power high speed sar adc

advertisement

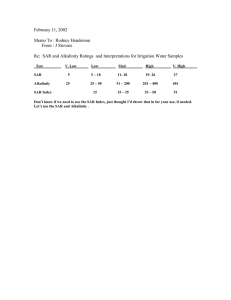

International Journal of VLSI Design, 2(2), 2011, pp. 121-128 EXPLORATION AND DESIGN OF SAR LOGIC FOR LOW POWER HIGH SPEED SAR ADC A.R. Kasetwar1, & V.G. Nasre2 Electronics Department Bapurao Deshmukh college of engineering, Wardha M. S.India (1E-mail: abhay_4674@rediffmail.com, 2vrushnasre@gmail.com) Abstract: Analog-to-digital converters (ADCs) are key design blocks in modern microelectronic digital communication systems. An analog?to?digital converter (ADC) acts as a bridge between the analog and digital worlds. It is a necessary component whenever data from the analog domain, through sensors or transducers, should be digitally processed or when transmitting data between chips through either long-range wireless radio links or high-speed transmission between chips on the same printed circuit board. With the continued proliferation of mixed analog and digital VLSI systems supporting diverse chip functionalities, the need for small sized, low-power and high-speed analog-to-digital converters using conventional CMOS process has increased. Moreover, nowadays power dissipation has become a key performance to be considered in analog designs, especially in those developed for portable devices. Various examples of ADC applications can be found in data acquisition systems, measurement systems and digital communication systems also imaging, instrumentation systems. Hence, we have considered all the parameters and improved the associated performance significantly reduce the industrial cost of an ADC manufacturing process and design specially power consumption. There is a wide variety of different ADC architectures available depending on the requirements of the application. They can range from high-speed, low resolution flash converters to the high-resolution, low-speed oversampled noise-shaping sigma-delta converters. Among various ADC architectures, we chose to implement a Successive Approximation Register (SAR) ADC that is one of the best suited for low power. We target a resolution of 4-bit and a power consumption of few milli watts. The SAR ADC is implemented in 0.18um CMOS technology with a power supply of 1v. Keywords: SAR, ADC, CMOS Technology, Low power, high speed. 1. INTRODUCTION As IC fabrication technology has advanced, more analog signal processing functions have been replaced by digital blocks, analog-to-digital converters (ADCs) retain an important role in most modern electronic systems because most signals of interest are analog in nature and must to be converted to digital signals for further signal processing in the digital domain. Analog to Digital Converters (ADCs) are currently adopted in many application fields to improve digital systems, which achieve superior performances with respect to analog solutions. There is a wide variety of different ADC architectures available depending on the requirements of the application. Successive approximation and algorithmic ADCs are one of the best example. Successive-approximation analog-to- digital converters (SAR-ADCs) have recently become very attractive in energy efficient moderateresolution/moderate-speed applications due to their minimal active analog circuit requirements. In a SAR-ADC, a digital-to-analog converter (sub-DAC) tries to estimate the value of each sample of the input analog signal through successive approximations and comparisons. Based on the ADC resolution, after a particular number of cycles, the digital word stored in the successiveapproximation register (SAR) corresponds to the analog sample with a particular quantization error. It typically generates one bit per clock cycle, the benefits are the low area needed for the implementation. ADCs of this type have good resolutions and quite wide ranges Successive-approximation-register (SAR) analog-to-digital converters (ADCs) represent the 122 majority of the ADC market for medium-to highresolution ADCs. SAR ADCs provide up to 5Msps sampling rates with resolutions from 8 to 18 bits. The SAR architecture allows for high-performance, low-power ADCs to be packaged in small form factors for today’s demanding applications. With ADS and Microwind we have designed 4 bit low power SAR ADC with 0.18µm technology. 2. SAR ADC The block diagram of a successive approximation ADC is shown in Figure. It consists of a comparator, a DAC and a successive approximation register (SAR). The successive approximation ADC uses a binary search algorithm to find the closest digital code for an input signal. When an input signal is applied to the converter, the comparator simply determines whether the input signal is larger or smaller than the DAC output and produces one digital bit at a time starting from the MSB. The SAR stores the produced digital bit and uses the information to change the DAC output for the next comparison. This operation is repeated until all the bits in the DAC are decided. In order to achieve N-bit resolutions, a successive approximation ADC requires N clock cycles. Because the performance is limited by DAC linearity, the calibration of the DAC is needed to achieve high resolution. International Journal of VLSI Design The successive approximation Analog to digital Converter circuit typically consists of four chief sub circuits: 1. A sample and hold circuit to acquire the input voltage(Vin). 2. An analog voltage comparator that compares Vin to the output of the internal DAC and outputs the result of the comparison to the successive approximation register (SAR). 3. A successive approximation register sub circuit designed to supply an approximate digital code of Vin to the internal DAC. 4. An internal reference DAC that supplies the comparator with an analog voltage equivalent of the digital code output of the SAR for comparison with Vin. The successive approximation register is initialized so that the most significant bit (MSB) is equal to a digital 1. This code is fed into the DAC, which then supplies the analog equivalent of this digital code (Vref/2) into the comparator circuit for comparison with the sampled input voltage. If this analog voltage exceeds Vin the comparator causes the SAR to reset this bit; otherwise, the bit is left a 1. Then the next bit is set to 1 and the same test is done, continuing this binary search until every bit in the SAR has been tested. The resulting code is the digital approximation of the sampled input voltage and is finally output by the DAC at the end of the conversion (EOC). Using ADS, we have designed SAR components and analyzed their simulation results to design SAR architecture. A. Design Of Shift Register Using DETDFF Because the difference between input signal and reference successively gets smaller, circuit noise will limit the achievable resolution. A faulty comparator decision means that further iterations will not provide additional information of the input signal. Conventional single-edge-triggered flip-flops (SET-FF’s) changes states at the time when the clock signal goes from 0 to 1 or at the time when the clock goes from 1 to 0. The former are called positive-edge-triggered flip-flops (PET-FF’s) or rising edge-triggered flip-flops (RET-FF) and the latter are called negative-edge-triggered flip-flops (NET-FF’s) or trailing-edge triggered flip-flops (TET-FF’s). Successive Approximation Register ADC represents the majority of the ADC market for medium to high resolution. This topology requires just one comparator; an N-bit SAR ADC will require N comparison periods and will not be ready for the next conversion until the current one is complete. The advantage of edge triggering is that the setup time for data input is independent of the clock pulse width. This makes system design simpler. It is also less sensitive to noises. However, these flip-flops respond only once per clock pulse cycle. Energy and time are wasted. Figure 1: SAR ADC Exploration and Design of SAR Logic for Low Power High Speed SAR ADC T he s e d ouble -e d ge- trigge re d f lip- f lop s (DET-FFs) have two major advantages. First, power dissipation is reduced. With the conventional SET-FF’s, one of the two clock transitions accomplishes nothing. However, this transition may cause changes in the output of some logic elements internal to the FF’s. In addition, extra energy is wasted to charge or discharge the capacitive load of the global clock line in a system using SET-FF’s. This is particularly true in CMOS where static power dissipation is small and the dynamic power dissipation is the main contributor of energy dissipation. Second, the speed of the system is accelerated. With both edges able to cause state transition, some redundant logic can be eliminated. Moreover, the clock period will be shortened because there is no need to wait for the clock signal to toggle up and down. The main disadvantage of DET-FF’s has been the substantial increase in the number of components required to build such FF’s. In most cases, more than double the logic counts is expected. This paper proposes a novel design in CMOS which will implement static DET-FF’s with relatively little increase in components. Figure 3: Transient Response of DETDFF This example hints that a 4 bit shift register can also be designed by just replacing traditional Single Edge Triggered D Flip-flop with Double Edge Triggered D Flip-flop. Figure 4(b) shows the waveforms of 4 bit shift register. Dynamic DET flip-flops have also been investigated based on the fact that the DET flip-flops can be connected in series to form a shift register. Figure 2(a) shows two DET flip-flops connected in series, which form a 4-bit shift register. Figure 4: (a) 4 Bit Shift Register using DETDFF Figure 2: (a) Positive and Negative Level Sensitive Latch (b) SET Flip-Flop (c) DET Flip-flop 123 Figure 4: (b) Transient Analysis of 4 Bit Shift Register 124 International Journal of VLSI Design B. Comparator Transient Response In order to precisely slice the input data, a reference voltage may be transmitted, on a different signal path, along with the data. Alternatively, the data may be transmitted differentially (an input and its compliment). In either case a differential amplifier is needed as shown in below Fig. 5. Differential amplifier input buffer amplifies the difference between the two inputs. In the simple case one input to the input buffer is DC voltage, say 0.5 V (Vinm in fig). When the other input (Vinp) goes above 0.5 V, the output of the buffer changes states (goes from low to high or vice versa). A very small increase in Vinp above Vinm is required to make the output of the buffer switch states. Looking at Fig, we can see the input falls below VTHN (= 250mV here), then the circuit won’t work very quickly (the MOSFETs moves into the sub threshold region). So we would expect the propagation delays to increase. Vinp > Vinm → out = ‘1’ Vinp < Vinm → out = ‘0’ Figure 5: An (n-Flavor) Input Buffer for High-Speed Digital Design Ideally the delay of the buffer is independent of power supply voltage, temperature, or input signal amplitudes (or pulse shape). To get better performance for lower input level signals, we might use the PMOS version of the buffer as shown in Fig 6. The delays are considerably better, however, there is an offset that appears rather large (because the output changes at the same time as Vinp going past Vinm, indicating that an offset is present). To avoid this offset, we might use the NMOS buffer in Fig. 5 with the PMOS buffer in Fig. 6 to form a buffer that operates well with input signals approaching ground or VDD. The result seen in Fig. 7. By using the buffers in parallel, the complementary nature results in buffer that is robust and works over a wide range of operating voltage. Fig. 8 (a, b,) shows the CMOS test circuit and transient analysis of comparator . This circuit is self biased because no external references are used to set the current in the circuit (the gate of M6 is tied up with M3). When Vinp is greater than Vinm, the current in M2 is larger than current in M1 (VGS2 > VGS1). The current in M1 flows through M3 and is mirrored by M4 (and so M4’s current is less than M2's current). This causes the diff-amp’s output, Vom, to go towards ground (until the current in M2 equals the current in M4) and the output of the inverter, Out, to go high. Figure 7: Rail to Rail Input Buffer Figure 6: A PMOS Input Buffer for High-Speed Digital Design Figure 8: (a) Test Circuit of Comparator Exploration and Design of SAR Logic for Low Power High Speed SAR ADC 125 Figure 8: (b) Transient Response of Comparator C. DAC Resistor ladder networks provide a simple, inexpensive way to perform digital to analog conversion (DAC). The most popular networks are the binary weighted ladder and the R/2R ladder. Both devices will convert digital voltage information to analog, but the R/2R ladder has become the most popular due to the network’s inherent accuracy superiority and ease of manufacture. Figure 9(a) is a diagram of the basic R/2R ladder network with N bits. The “ladder” portrayal comes from the ladder-like topology of the network. Note that the network consists of only two resistor values; R and 2R (twice the value of R) no matter how many bits make up the ladder. The particular value of R is not critical to the function of the R/2R ladder Figure 9: (a) Ladder Network Let’s take a look at how an R/2R ladder works. Term. is the termination resistor and is connected to ground. Digital information is presented to the ladder as individual bits of a digital word switched between a reference voltage (Vr) and ground. Depending on the number and location of the bits switched to Vr or ground, Vout will vary between 0 volts and Vr. If all inputs are connected to ground, 0 volts is produced at the output, if all inputs are connected to Vr, the output voltage approaches Vr, and if some inputs are connected to ground and some to Vr then an output voltage between 0 volts and Vr occurs. These inputs (also called bits in the digital lingo) range from the Most Significant Bit to the Least Significant Bit. As the names indicate, the MSB, when activated, causes the greatest change in the output voltage and the LSB, when activated, will cause the smallest change in the output voltage. If 126 International Journal of VLSI Design we label the bits (or inputs) bit 1 to bit N the output voltage caused by connecting a particular bit to Vr with all other bits grounded is: Vout = Vr/2N where N is the bit number. For bit 1, Vout =Vr/2, for bit 2, Vout = Vr/4 etc. The expected output voltage is calculated by summing the effect of all bits connected to Vr. For example, if bits 1 and 3 are connected to Vr with all other inputs grounded, the output voltage is calculated by: Figure 9: (b) Design of R-2R DAC Figure 9: (c) Simulation Results of of DAC Vout = (Vr/2) + (Vr/8) which reduces to Vout = 5Vr/8. The R/2R ladder is a binary circuit. The effect of each successive bit approaching the LSB is 1/2 of the previous bit. The full-scale output is less than Vr for all practical R/2R ladders, and for low pin count devices the full-scale output voltage can be significantly below the value of Vr. Equation can be used to calculate the full-scale output of an R/2R ladder of N bits. Exploration and Design of SAR Logic for Low Power High Speed SAR ADC 3. SAR ARCHITECTURE Figure 10: (a) Design of SAR ADC Figure 10: (b) Simulation Results of SAR ADC 127 128 International Journal of VLSI Design Dual-Edge-Triggered Flip-Flops”, IEEE J. VLSI Systems, 10 No. 6, pp. 913-919, Dec 2002. 4. CONCLUSION In this paper, low power and high speed SAR ADC is proposed and designed in 0.18µm CMOS technology. We presented high speed and low power design of DETDFF and by using the same we designed shift register whose speed of operation is nearly doubled than that of shift register made up of SETDFF with low power consumption. of SETDFF with low power consumption. Also we presented CMOS comparator circuit which is a combination of n-flavored and p-flavored buffers and remove the disadvantages of both. An area efficient DAC architecture strictly based on the R-2R ladder topology is designed. We implemented SAR ADC by using these components. This SAR ADC is designed in 0.18uM CMOS Technology with 4 bit resolution. It consumes 71.18uW of power. Its rate of conversion is 25Ms/s. REFERENCES [1] Modeling Segmented-Ladder DACs David Marche and Yvon Savaria, Fellow, IEEE. [2] W.Chang, T. Lo and Manoj Sachdev, “A Comparative Analysis of Low-Power Low-Voltage [3] A MOST-Only R-2R Ladder-Based Architecture for High Linearity DACs Dimitris Karadimas, Michail Papamichail and Kostas Efstathiou Dept. of Electrical Engineering & Computer Technology, University of Patras, Greece karadimas@apel.ee. upatras.gr. [4] G. E. Tellez, A. Farrah and M. Sarrafzadeh, “ActivityDriven Clock Design for Low Power Circuits”, in Proc. ZEEE ICCAD, San Jose, pp.62-65, NOV. 1995. [5] S. H. Unger, “Double-Edge-Triggered Flip-Flops”, IEEE Trans. Computers, 30, No. 6, pp. 447-451, June 1981. [6] On The Study of a Digitally Calibrated R-2R Ladder Architecture D. S. Karadimas, K. A. Efstathiou Dept. of Electrical Engineering & Computer Technology, University of Patras, Greece karadms@apeI. ee. upatras .gr [7] M. Afghahi and J. Yuan, “Double Edge-Triggered D-Flip-Flops for High Speed Circuits”, IEEE J. SolidState Circuits, 26, No. 8, pp.1168-1170, Aug. 1991. [8] A New Design of Double Edge Triggered Flip-flops by Massoud Pedram,Quing Wu and Xunwei 0-7803-4425-1/98 IEEE