Mismatch sensitivity of a simultaneously latched CMOS sense

advertisement

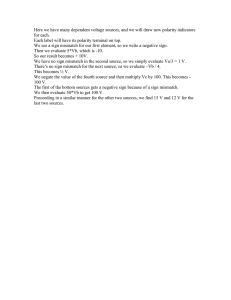

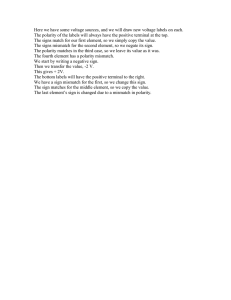

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 10, OCTOBER 1991 1413 Mismatch Sensitivity of a Simultaneously Latched CMOS Sense Amplifier Rahul Sarpeshkar, John L. Wyatt, Jr., Member, IEEE, Nicky C. Lu, Fellow, IEEE, and Porter D. Gerber Abstract -This paper derives a new formula for the sensitivity of a vertically matched CMOS sense amplifier, of the type used in DRAM’s, to threshold voltage mismatch, parasitic capacitance mismatch, transconductance mismatch, and bit-line load capacitance mismatch. The formula yields insight into DRAM sensing operation. The perturbation approach used here is novel and rigorous and yields an explicit closed-form solution. The formula agrees well with simulations. It is inherently slightly conservative and thus appropriate for use in design. I. INTRODUCTION M OST sense amplifiers used in DRAM’s consist of a cross-coupled latch activated during sensing by a pull-down latching waveform (NMOS latches) or a pull-up latching waveform (PMOS latches) to amplify and restore a differential voltage signal from the bit lines of the memory array. Parametric mismatch in the transconductance, parasitic capacitance, threshold voltage of the FET’s, or in the bit-line load capacitance causes an imbalance in the sense amplifier that can amplify the input signal in the wrong direction. Sensitivity of the sense amplifier is defined as the magnitude of the minimum differential input signal that can be correctly sensed. It is a function of the latching waveform and the parametric mismatches. It is important for the designer to be able to quantify this, since sensing should be done as fast as possible, subject to the sensitivity constraints imposed by Manuscript received August 17, 1990; revised June 14, 1991. This work was supported in part by the National Science Foundation and the Defense Advanced Research Projects Agency under Contract MIP-8814612 under the auspices of the M.I.T. VI-A Electrical Engineering Internship Program at the IBM T. J. Watson Research Center and the Undergraduate Research Opportunities Project at M.I.T. R. Sarpeshkar was with the Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139. He is now with the Department of Computation and Neural Systems, California Institute of Technology, Pasadena, CA 91 125. J. L. Wyatt, Jr. is with the Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139. N. C. Lu was with the IBM Research Division, Thomas J. Watson Research Center, Yorktown Heights, NY 10598. He is now with Etron Technology Inc., Hsinchu Science-based Industrial Park, Taiwan, Republic of China. P. D. Gerber is with the Mathematical Sciences Department, IBM Research Division, Thomas J. Watson Research Center, Yorktown Heights, NY 10598. IEEE Log Number 9102466. the parameter mismatches inherent in the fabrication process. Lynch and Boll [l] derived the optimal latching waveform for an NMOS latch. Ieda et al. [2] postulated an empirical formula for the sensitivity of an NMOS latch. Wang [3] derived formulas for sensitivity for optimal control latching waveforms, and Natori [4] for latching waveforms that maintain a constant overdrive for an NMOS latch. Currently most sense amplifiers in DRAM’s are CMOS with NMOS and PMOS latches and use linear latching waveforms as shown in Figs. 1 and 2. Kraus and Hoffman [5]pointed out that fast sensing can be achieved if the NMOS and PMOS latches are activated simultaneously. This paper derives a sensitivity formula for this sensing scheme, using perturbation theory. The perturbation approach is rigorous: it avoids most approximations and ad-hoc assumptions, and it introduces no free constants to be determined from simulations. It yields an explicit formula for the sensitivity in the case that the W / L ratios of the n and p latches are sized for equal pull-up and pull-down capability. Although the body of this paper addresses only this vertically matched case, the perturbation method works in general. The Appendix contains an approximate formula for the unmatched case, where certain integrals cannot be evaluated in closed form. For reasons of space, several mathematical details involved in the derivation are omitted from the paper. Readers interested in these details should consult [8] and [9]. 11. OVERVIEW AND RESULTS Fig. 1 shows the cross-coupled CMOS sense amplifier. Fig. 2 shows the waveforms at the latching nodes P and S and bit-line nodes 1 and 2 for a typical case of senseamplifier operation with linear latching and simultaneous activation. VPRis the common precharge voltage to which the latch and bit-line nodes have been precharged before the start of sensing (except for the small differential voltage present at the bit-line nodes). The figure illustrates the case of unsuccessful sensing where, even though u J 0 ) is initially higher than ~’~(01, the parametric mismatches drive u2 in the decreasing direction. The latching rate slopes m p and m, are the gradual slopes of u,(t> OOl8-920O/91/ 1000-1413$01.00 01991 IEEE IEEE J( IURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 10, OCTOBER 1991 1414 I CL T T I JT Fig. 1. Sense-amplifier circuit. The sense amplifier is said to be perfectly balanced o r symmetric when all parameters on the left-hand side (denoted with subscript = 1) are equal to parameters on the right-hand side (denoted with subscript = 2). It is said to be Lwtically mutched when the W / L ' s of the N F E T s and PFET's have been ratioed so that the sense amplifier has equal pull-up and pull-down capability. The novel element in this paper is the use of dynamic perturbation theory 161, [7] to set up a linear time-varying differential equation for the first-order perturbation in differential voltage about the unstable, perfectly symmetric solution obtained when all parameters are matched and the differential voltage is zero. The sensitivity is found by calculating the minimum initial differential voltage, 6~',,(0)= 6u,(O)- 6u,(O), that is required to keep the final value of the differential voltage at t = +E at the same polarity as the initial differential signal, despite opposition from the parametric imbalances that attempt to drive it in the opposite direction. For the vertically matched case where the pull-up and pull-down are sized to have equal drive capability, all resulting integrals are evaluated in closed form and an explicit formula is given for the sensitivity. A. Notation and Conventions Fig. 1 shows the cross-coupled sense-amplifier circuit with transistors M N , , MN,, MP,, and MP, and their parasitic gate-source capacitances. Each FET contributes three parameters to the circuit: its gate-source capacitance C,, threshold voltage VT,and transconductance K. The bit-line capacitance C , adds two more parameters for each side of the sense amplifier, making the circuit sensitive to 14 parameters in all. Parameter mismatch is represented by a 6 in front of the parameter and is equal to half the magnitude of the difference between the right and left sides of the sense amplifier, e.g., SV,, = IvTNI - VTN21/2. Our sign convention assumes that all parameters are positive. Thus, we explicitly take care of the negative sign of the PFET threshold voltages in the equations. The PFET and pull-up parameters have subscript p . The NFET and pull-down parameters have subscript n. Additional subscripts 1 or 2 are added onto these depending on whether the parameter refers to the left side or the right side of the sense amplifier, respectively. Parameters without subscripts 1 or 2 refer to the common symmetric I I I I I I I 1 1-5.0 0.0 5.0 10.0 15.0 20.0 25.0 M.0 35.0 value about which the actual parameters deviate. If a Time (NS) parameter on one side is incremented above the common Fig. 2. Voltage waveforms in a case of unsuccessful sensing. Although symmetric value, the equivalent parameter on the other cZ(O)> c,(O), the mismatches drive 1s2 to G N D and to VDD,At t = 0 the perfectly balanced sense amplifier with zero differential voltage side is decremented below the symmetric value in perfect would just start conducting. The linear latching waveforms u,(t) and antisymmetric fashion so that the combination of parameu,(t) have slopes m, and - m s ,respectively. The PFET and N F E T ters in the circuit yields a worst-case scenario for computthreshold voltage mismatch was 200 mV and a differential signal of 195 ing the sensitivity. mV was applied. Assuming 6c2,(0) = v2(0)- u,(O) > 0 initially, without loss of generality, the worst possible scenario that would and u J t ) present just after conduction has begun in the cause amplification in the wrong direction would be one having strong pull-down characteristics on the node 2 side period of slow sensing.' and strong pull-up characteristics on the node 1 side to offset the initial voltage imbalance. All parameters are consequently chosen so that the sense amplifier pulls in 'Sense amplifiers usually have a period of slow sensing followed by a period of fast sensing where the waveform slopes are increased. The the wrong direction; i.e., the left side PFET and right side period of fast sensing occurs when a considerable differential signal has developed. The latter has little effect on sensitivity, and is not consid- NFET have higher K 's, lower threshold voltages, and smaller parasitic capacitors than their counterparts on the ered in this paper. I 1415 SARPESHKAR et al.: MISMATCH SENSITIVITY OF LATCHED CMOS SENSE AMPLIFIER other side. The choice for load capacitors will be explained in Section III-D. The following auxiliary parameters are defined: SKE' = SKN 2(m, + ms) \ "GEFF = SKEiF = SC,, m p + 6C,, mp + m , m, SKgiF= (A &KFP= - lim,,+(;+ (7) + -m -), j 2( mp + m,) SKN[ S K , m i + S K , mf 2m:um I 0.2m, +0.8ms ( 12) +6KN)mZap 'mi, (13) SKF' = The three parameters below are used frequently in the derivation of the formula, though they do not appear in the final result: SKp 2(m, + m.7) a==: SK, (9) fisum G O T 2(m, + ms) g = amiet h = mcap. B. Sensiticity Formula (Main Result) (14) (15) ( 16) The criterion for successful sensing derived in this paper is Su,,(O) > the sum of all terms below: Dominant terms + 2 SVT EFF Secondary terms 0.38- miet msum Mismatch type +0.62msum t Threshold + Parasitic TOT t Transcond. + Transcond. +- Load (17) 1416 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 10, OCTOBER 1991 where all constants have been evaluated. The four terms2 represent the effects of mismatches in the transistor thresholds, parasitic gate-to-source capacitances, transconductances, and the load capacitances, respectively. Simulation results in Figs. 3-6 show the formula to be slightly conservative in the sense that the minimum differential voltage for successful sensing, 6 u,,(O), is slightly less than the formula predicts. The conservative nature of the formula comes from the simplifying assumption that the parameter mismatches affect the solution to infinite time instead of up to a finite point in time, such as up to the end of the slow sensing period. The formula is derived for the case where K , = K N . secondary terms added less than a 3% correction to the dominant terms in the worst case. Thus, they are not discussed further in the body of this paper except for the case of load capacitance mismatch. Further interpretations of the meanings of the secondary terms for each kind of mismatch may be found in [SI and [9]. 111. SIMULATION RESULTS AND EXPLANATION Simulations were performed for typical circuit values to evaluate the validity of the formula. The threshold voltage simulations were performed with HPSPICE and all others with ASTAP. The simplest MOSFET models with no modeling of second-order effects, such as the back-gate or body effect, drain-induced barrier lowering, channellength modulation, overlap capacitance, etc., were used. C. Discussion The ASTAP library functions were supplemented with The latching rate mfet is an effective FET latch rate at Fortran code to create a simple MOSFET model whose which the nodes 1 and 2 would move in the perfectly parameters could be easily varied for ease in simulation. balanced symmetric solution if all capacitors were absent The most basic SPICE MOSFET models were used for and only the FET’s were present. The latching rate mcap the threshold voltage simulations. is an effective parasitic capacitance latch rate at which the Parameters were varied between simulations for some nodes 1 and 2 would move in the perfectly balanced variety as seen in Table 11, but always so that the simultasymmetric solution if no FET’s were present and only neous latching condition was satisfied ( m p / m s = capacitors were present. The voltage V,,, characterizes V,, / V,,). All four gate-to-source capacitances were set the speed-sensitivity trade-off in the sense amplifier. It to zero when the corresponding FET was off and turned appears in calculations of parasitic, transconductance, on abruptly when the corresponding vGs rose above zero. and load sensitivity and is analogous to the voltage V,, = In all simulations LtS(t)and c,(t) were saturated at 0 and k T / q that characterizes bipolar differential amplifier 5 V and VPR= 2.5 V as shown in Fig. 2, and C,, = 5 fF, mismatches. The mismatches SVTEFF 6CGEFF,SKF&, C , = 200 fF,and K = 5 x lo-’ mA/V2 in all cases. and SKF:F are weighted combinations of PFET and Figs. 3-6 show that the formula is slightly conservative NFET mismatches and quantify the relative importance in all cases but not by very much. The agreement with of the PFET’s or NFET’s in contributing to the sensitiv- theory is best for threshold voltage mismatch (within 1%) ity. As can be seen from ( 5 ) to (7), higher pull-up latching and worst for load capacitance mismatch (within 30%). rates m p cause PFET mismatches to be more heavily weighted in determining the sensitivity and vice-versa. A. Threshold Voltage Mismatch The formula of (17) has the following general structure: The criterion for successful sensing with threshold voltapart from load capacitance, each kind of mismatch contributes two kinds of terms to the sensitivity formula. age mismatch is listed in the first row of (17) with SV,,,, These terms are called the dominant and secondary terms. being defined in (5). Note that if SV,, = SV,, = SV, the The dominant term for each kind of mismatch is a combi- criterion reduces to the well-known result Su,,(O) > 2 SV,, nation of the NFET and PFET mismatches, as evidenced which says that the initial differential voltage should be in SVTEFF, SCGEFF, and SKEiF7 and is usually much greater than the net threshold voltage mismatch 2 SV, to greater than the secondary term. The secondary terms prevent one side of the amplifier from turning on before may be neglected to first order in design. Note, however, the other. However, if they are not equal, the dominant that for load capacitance mismatch the only contributor term defines an effective threshold voltage mismatch 6VTEFF,which is the weighted average of the PFET and to sensitivity is a secondary term. The secondary terms for each kind of mismatch are NFET threshold voltage mismatches with the weights proportional to products of difference terms involving being the pull-up and pull-down latching rates m p and PFET and NFET mismatches and difference terms in- m,, respectively. This term behaves like the original volving pull-up and pull-down rates. Thus, for typical threshold voltage mismatch. The threshold voltage mismatch curve (Fig. 3) plots the cases of operation where the differences between pull-up and pull-down rates and/or the differences between sensitivity versus NFET threshold voltage mismatch asPFET and NFET mismatches are not very big, these suming that the PFET mismatch is zero. The threshold terms add small corrections to the dominant term sensitiv- voltage sensitivity is then predicted to be very close to , weighted average of the NFET and PFET ity. For the simulation parameters of this paper, the 2 S V T E F Fthe threshold voltages with the weights being the latch rates. ’The transconductance terms have been distributed across two lines This implies that the sensitivity is less than the NFET threshold voltage mismatch by the factor m , / ( m p m,) for reasons of space. + SARPESHKAR et TABLE I1 PARAMETER VALUESFOR SIM~JLATIONS Fig. 3 0.7 1.0 2.5 3.57 5.0 Fig. 2 0.7 1.0 2.5 3.57 5.0 vTp(v) V,,(V) m,(x108 V/s) m,(xlO* V/s) c,, 1417 al.: MISMATCH SENSITIVITY OF LATCHED CMOS SENSE AMPLIFIER (fF) Fig. 5 0.5 0.5 5.0 5.0 5.0 Fig. 4 0.5 0.5 5.0 5.0 10.0 .,I 280 Fig. 6 1.0 0.5 5.0 2.5 10.0 P A 0 A 0 1 ' 0 I I I I 37 60 90 120 NMOS Sense Amplifier Redictions ([21). CMOS Sense Amplifier RcdIcrions. CMOS Sense Amplifier Simulation Rcsulls I I50 I I 180 210 NFET Thnrhold Mismavh (mV) Fig. 3. Sensitivity versus NFET threshold mismatch. Sensitivity denotes the magnitude of the minimum differential input signal 8[.,J0) = luz(0)- ul(0)( that can be correctly sensed. The NFET threshold mismatch refers to lVTN,- VTNll= 2 SV,,. The PFET threshold mismatch is set to zero for this simulation. The figure also shows the predictions of Ieda et al.'s [2] formula for an equivalent NMOS sense amplifier, i.e., one with just the NFET's, latched at the rate mSumand having all other parameters exactly as above. from (5). The simulations confirmed this to good accuracy (within 1%)as shown in Fig. 3. For an equivalent NMOS sense amplifier (the sense amplifier with no PFET's present, the same K,CL,CGN,SV,,, and latching rate mp + ms),the formula in [2] correctly predicts the sensitivity to This curve is also shown in Fig. 3 for be just 2 SV,,. comparison. For the case where the NFET threshold voltage mismatch is equal to the PFET threshold voltage mismatch, the formula predicts that the sensitivity is equal to the threshold voltage mismatch as in the NMOS sense amplifier. This was also confirmed by simulations, though the curve is not shown. B. Parasitic Capacitance Mismatch The criterion for successful sensing with parasitic capacitance mismatch is listed in the second row of (17). The effective parasitic mismatch 6CGEFFpresent in the dominant term is a weighted average of the PFET and NFET parasitic capacitance mismatches SC,, and SC,, , with the weights being the pull-up and pull-down latching rates m p and m,y,respectively, as stated in (6). The trade-off between speed and sensitivity is revealed in the Vs,, term. OJ I 2 I 4 I 6 I Values Rcdictui by Theory Simulation Results I I 8 10 12 Percentage Parasidc Capacitance Mismatch Fig. 4. Sensitivity versus parasitic capacitance mismatch. Percentage parasitic capacitance mismatch refers to IC,,, - C,,,I/CGP X 100 = IC" - C G N I l / C G N x 100. The parasitic capacitance mismatch agrees well with predictions at low-percentage mismatches and deviates more at higher values as seen from Fig. 4. This is expected since the first-order linear corrections predicted by perturbation theory are closer to reality if the perturbations are small. The formula is conservative by about 15% for the largest mismatch plotted. C. Transconductance Mismatch The criterion for successful sensing with transconductance mismatch is listed in the third and fourth rows of (17). The dominant term, involving S K E i F ,represents the influence of FET coupling to nodes 1 and 2 that acts with transconductance mismatch to hurt sensing. As can be seen from (7), it is a linear combination of the PFET and NFET mismatches with the linear constants being related to the squares of the pull-up and pull-down latching rates, m p and m,, respectively. Fig. 5 shows that the formula predictions are conservative by about 15% in the worst case. D. Load Capacitance Mismatch The criterion for successful sensing with load capacitance mismatch is listed in the last row of (17). Note that this equation predicts that whenever the latching rates are equal and the parasitic 'capacitances of the NFET's and PFET's are equal, the sense amplifier will be insensitive to load mismatch and will sense correctly even if there are large mismatches in load capacitance! Even if the latching IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 10, OCTOBER 1991 P / f :I/ NMOS Scnsc Amplifier Redicnnns ([21). A 0 CMOS Sense Amplifier Redictionr. CMOS Scnsc Amplifier Simulation ResulU. , 0 2 4 6 8 10 12 Percentage Load Mismatch I 2 I 4 I 6 I 1 I 8 10 12 Rrcentage TransconductanceMismatch Fig, 5. Sensitivity versus transconductance mismatch. Percentage X 100 = I K N z transconductance mismatch refers to IK,, - K&K K,,I/K x 100. rates and/or parasitic capacitances are not equal, CMOS sense amplifiers that have simultaneous activation are characterized by being far less sensitive to load mismatch than their older NMOS counterparts. This has been reported by Kraus and Hoffman [ 5 ] and confirmed clearly in our analytic formula. Fig. 6 shows the simulation results and predictions for sensitivity from the formula of this paper for the simultaneously latched CMOS sense amplifier. The formula is conservative by = 30% for the largest mismatch plotted. The figure also shows that the correct predictions for sensitivity in [2] for an equivalent NMOS sense amplifier (an NMOS sense amplifier with no PFET's present, with the same K,CL,CG,,GCL, and latching rate mp m,) are much larger. Section III-E contains a more detailed comparison between CMOS and NMOS sense amplifiers. CMOS is relatively insensitive to load capacitance mismatch, since movements in node voltages are relatively indifferent to the size of the load capacitance if charge is both added to and removed from a node. NMOS is more sensitive to load capacitance than CMOS since it can only sink charge, and node voltages at the lower capacitance node will be freer to drop than those at the higher capacitance node, causing an imbalance that affects the sensitivity. Delayed sensing schemes where the p latches are activated with some delay following the activation of the n latches or vice versa are also more sensitive to load mismatch than simultaneous latching schemes, since they involve a period when charge is only being sunk or sourced. The small sensitivity in simultaneous latching Fig. 6. Sensitivity versus load capacitance mismatch. Percentage load capacitance mismatch refers to IC,, - C,,I/C, x 100. The pull-up and pull-down latch rates differ greatly in this simulation in order to obtain a measurable secondary term, which is the only contributor to load capacitance sensitivity. T h e figure also shows the predictions of Ieda et al.'s [2] formula for an equivalent NMOS sense amplifier, as in Fig. 3. arises because the top-down asymmetry due to parasitic mismatch and/or latching rates implies that net charge is being sourced or sunk by the load, though at a far slower rate. It must be noted that the formula was derived for a worst-case scenario with c2 > ul. If the top-down asymmetry is such as to cause the symmetric solution to fall, the mismatch will actually aid the sensing in this case but hurt it if u2 < u l . The general rule is that the node with lower capacitance is better at sensing the direction in which the symmetric solution tends to go. E. Comparison with NMOS Sense-Amplifier Sensitiuity Ieda et al. [2] postulated an empirical formula for an NMOS sense a m ~ l i f i e r ,which ~ in the notation of this paper would read + where A was an empirical constant known to be = 0.5, and Note that VcHAR (as we have called it) is similar in form to the V,,, term in this paper (equation (13)) and that both terms enter the sensitivity formula in a similar fashion. The formula (18) does not contain a term for parasitic capacitance mismatch. The formula was known to be empirically accurate when C, >> C,. 30nly the N latch is used for sensing. 1419 SARPESHKAR el nl.: MISMATCH SENSITIVITY OF LATCHED CMOS SENSE AMPLIFIER CMOS (general case) Mismatch Threshold Voltage 26V,,,, CMOS (vertical symmetry) NMOS ([21) 2 SV, svTN 1 (ZiVSEN I ! E ( 2 5 ) / F1 7 Parasitic Capacitance Load Capacitance I 2( 0.5m,,, +0.5mC,, n m5um It is interesting to compare the largest terms in the CMOS formula of (17) with terms in the NMOS formula for each type of mismatch. Except for load capacitance mismatch, all these terms are the dominant terms of (17). The CMOS formula terms for threshold voltage mismatch, parasitic capacitance mismatch, and transconductance mismatch are proportional to effective mismatches, which are combinations of the respective PFET and NFET mismatches as seen from ( 5 ) to (7). While the NMOS formula has the same empirical prefactor A for transconductance and load capacitance mismatch, the CMOS formula may be viewed as having a different prefactor for each kind of mismatch, expressed in the dependence of SVTEFF, SCGEFF,and SK& on the latching rates in (5147). Thus, for example, in the special case that there is perfect vertical symmetry4 in the sense amplifier, i.e., m p = m,, C,, = C,, = C,, SV,., = SV,, = SV,, SC,, = SC,, = SC,, and SK, = 6 K , = S K , the CMOS formula in the notation of [2] would have an identical dependence on threshold voltage mismatch, a similar dependence on transconductance mismatch but with a prefactor of &/8 = 0.31, a dependence on parasitic capacitance = 1.25, and would mismatch with a prefactor of =/2 be totally insensitive to load mismatch. The sensitivity to load mismatch is drastically lower for CMOS than for NMOS since the contribution to sensitivity occurs only from a secondary term, and in the special case above, even this is 0. Note that there are no empirical constants in the CMOS formula. Table 111 summarizes the above comparisons. IV. OUTLINE OF THE DERIVATION It is the initial few nanoseconds, during which the differential voltage is rather small compared to a threshold voltage, that are important in deciding whether the amplification will proceed in the right direction. In almost all practical cases, the parametric mismatches are small enough that by the time the FET’s reach the linear region the differential voltage of 0.7-1.0 V (about one threshold voltage in magnitude) will continue to be amplified with‘Note that the term perfect verticd symmetry, defined above, has a different meaning than symmetric and vertically mntched in the caption to Fig. 1. out change in direction. Hence, for the purposes of computing sensitivity, it is assumed that all FET’s are in the saturation regime throughout. All second-order effects neglected in the simulations have been neglected here as well. In practice most sense amplifiers have an initial period of slow sensing followed by a period of fast sensing when the differential signal is sufficiently developed. Since sensitivity is affected almost only by the initial phase, the latching waveform referred to throughout this paper is the slow one and the latching rate is the slow sensing rate. The latching waveforms are produced in practice by a pull-up transistor connected to the top node and a pulldown transistor connected to the bottom node of the sense amplifier, which are turned on by activation of clocks at the time of sensing. This causes a very sharply sloping ramp-down in voltage at the bottom node and ramp-up at the top node until the transistors turn on, after which a more gradual linear slope is observed. Physically, since there is no real step, there is a time at which the FET’s turn on with no excess overdrive. This time is defined to be t = 0. In the derivation, the latching waveforms u,(t) and c,(t) are modeled as rising and falling forever with the slow sensing slopes m p and m,, respectively, rather than being terminated at V,, and GND, since it is only their initial functional dependence that is i m p ~ r t a n t The . ~ derivation does not include capacitive parasitic coupling while the transistors are off all gate-to-source capacitances are assumed to vanish for t < 0. A. Perturbation Theory for Differential Equations Suppose we have a vector differential equation where x is the vector that describes the state of the ‘Note that this treatment assumes that the NMOS and PMOS latches are activated simultaneously. Thus, the external pull-up and pull-down transistors, not shown in Fig. 1, that generate the latching waveforms must be sized appropriately so that the top node is pulled up one PMOS threshold voltage in the same time that the bottom node is pulled down une NMOS threshold voltage, i.e., m p / m , = V T p / VTN, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. IO, OCTOBER 1991 1420 system, U is the parameter vector, and f is the function describing the system. Suppose we know (in closed form or can compute by numerical integration) the response of to the parameter vector U,,, and the system x,,,(t) We desire to compute the reinitial condition x,,,(O). sponse of the system xn,,(t)+6x(t) to the parameter vector U,,, + 6u and initial condition x,,(O) + 6x(O), where 6u and are small enough that 6 x ( t ) may be treated as a first-order perturbation on the system. Perturbation theory then states that the first-order perturbation response 6 x ( t ) may be computed from the linear time-uarying vector differential equation [61, [71: both the n and p latches start conducting at the same time for the balanced symmetric case. In accordance with perturbation theory, a solution for the balanced symmetric case is first found and then the system is analyzed for perturbations about this. The latching waveforms are of the form7 cs( t ) = - V,, L',( The equations6 describing the circuit of Fig. 1 may be shown from Kirchoff's laws and the MOSFET equations in the saturation region to be de2 dt [ KP2 -= -( u 1 - c p 2 + V,,,) 2 KN2 - -( c 1 - LIS 2 - (25) - dt B. Solution of the Symmetric Equation (24) The symmetric solution occurs when r>,(t)= l , , ( t )= u S y M M ( tand ) from the above equations: -- where the matrices [ d f / d x ] and [ d f / d u ] are evaluated at known nominal values x,,,(t) and U,,, and the initial condition is given by 6x(O). Equation (21) is called the first cariational equation for the original system (20). In this paper, the voltage vector v ( t ) = ( u 2 ( t )u,(t)>r , represents the state of the network and the nominal solution uNoM(t)is the unstable perfectly symmetric solution obtained when all parameters are perfectly matched and u2(0)= cl(0). Under these conditions, c,(t) = Cl(t)= usyMM(t) and u,oM(t) = (uSyMM(t),c,yM,(t>>r. The Vettor U denotes the set of parameters in the circuit and is given by U = uSymm + 6u where uSymmdenotes the perfectly balanced set of parameters and 6u denotes the deviation from this. The term 6c2, = c2 - c', denotes the differential signal. m,t - + m,t. t ) = V,, ' L +'GN +'GP + CGPmpc1. CGNm.s + CGN + CGP . (26) The above equation is a nonlinear Ricatti equation. In general, this symmetric nonlinear equation cannot be solved in closed form and requires numerical integration. However, for the vertically matched case K , = K N = K , where the W / L ratios of the n and p transistors have been ratioed so that they have equal transconductance, the symmetric equation ( 2 6 ) becomes linear and reduces after some algebra to a linear equation of the form ~ ~ ' s Y M M + ate,,,, = gt + h dt where the parameters a, g , and h have been defined in Section 11-A. This equation has the solution u S Y M M t( ) = e p " ' i / 2 / ' e " T 2 / 2 ( g T+2h)dT 0 (28) since usyMM(0) = 0. v,N2)2 C. General Method for Calculating Sensitivity The general method for calculating the sensitivity of the system to its parameters given by parameter vector U with mismatch vector 6u is described here before solving specific cases. The first variational equation for the system equations (22) and (23) takes the form - K ( m , + ms>t 0 CL - K ( m , + m,)t c1. + C G N + cGN + cGP 0 + CGP (23) where it is assumed that the sense amplifier has turned on and operates in the saturation region. For simultaneous conduction, the waveforms u,(t) and u,(t> are such that 6Equations (22) and (23) assume all four transistors are on. As a result of parameter perturbations, there will be brief periods near t = 0 when some transistors are on and some are off. A correction to allow for this fact is given in [8, appendix C]. 'Note that the precharge voltage has been left out, as both the bit line and top and bottom latching nodes have been precharged to the precharge voltage prior to sensing. This shifts all voltages in the circuit by a constant equal to the precharge voltage, which is chosen as the reference value for potential-in the derivation. 1421 SARPESHKAR et al.: MISMATCH SENSITIVITY O F LATCHED CMOS SENSE AMPLIFIER where V u f , ( u ,d t ) , t ) is the vector d f l / d u and V u f 2 ( u , u ( t ) , t )is the vector d f 2 / d u , both of which are f l and f2 are evaluated at the symmetrical value uSymm, the functions on the right-hand sides of (22) and (23) respectively, and the superscript T denotes the transpose of a column vector Vuf. Subtracting rows, an equation for the differential voltage in terms of the parameters defined in Section 11-A is obtained: -'ufl( 7 'SYMM ( t , ') Ius,m) 9 (30) the solution to which is ously activated. However, the sensitivity is given by the term corresponding to load capacitance in (17) and is not 0 as predicted by the analysis in [51. The formula has some similarities with the empirical formula postulated by Ieda et al. [2] for an NMOS sense amplifier but contains no empirical constants, has a different "prefactor" for each kind of mismatch, and adds a term for parasitic capacitance mismatch. The new sensitivity formula also contains terms proportional to top-down asymmetries in the mismatches. These are usually small and may be neglected. The perturbation approach yields a general methodology for computing sensitivity. This paper has shown how it may be used to obtain closed-form solutions for the vertically matched CMOS sense amplifier, and the Appendix gives an approximate formula for the general case. APPENDIX (31) Assuming without loss of generality that 6u2,(0)> 0 for successful sensing, we require that 6u2,( m) > 0, so that the eventual perturbation is positive. Then the criterion for successful sensing translates to + APPROXIMATE SENSITIVITY FORMULA FOR THE GENERAL CASE( K P# K,) A detailed derivation of the formula to be quoted below can be found in [SI and [9]. Only the key ideas involved in the derivation and the formula are given here. It may be shown that the symmetric solution in this case has the same form as the symmetric solution (28) for the symmetric case ( K P= K,) if K is replaced b y K e f f = JK,K,, m f e , is replaced by f i f e t = ( d K , m , - G m s ) / ( K+ and (14)-(16) are then used to compute a, g , and h. The a, g, and h thus computed are denoted by 6,g, and h , respectively. The perturbation approach may then be used to show that the criterion for successful sensing may be approximated8 by K), The parameter vector 6u is picked to get an upper or worst-case bound for this criterion by ensuring that the integral in (32) is as large as possible. For the system under study, the parameter vector has 14 entries. For convenience, it is split into four separate vectors that separately parametrize the threshold voltages (four entries), parasitic gate-source capacitances (four entries), transconductances (four entries), and load capacitances (two entries), and the sensitivity is computed separately for each. Then, by the linearity of the perturbed system, the net sensitivity is computed by adding the separate sensitivities. The major mathematical hurdle involved was the closed-form evaluation of (32). These details are described in [81 and [91. a1/,pKpmP + S V I - N K N ~ , 6c2,(0) > 2 K F " ~ K+N m s - \ ( Kdiff (fifet KPmp + K N m s - Kdiff V. CONCLUSIONS The new formula (equation (17)) derived in this paper for a simultaneously latched CMOS sense amplifier and confirmed by simulations shows the following. The maximum of NFET mismatches and PFET mismatches does not determine the sensitivity, as may be intuitively expected. Rather, mismatches due to PFET's dominate in determining the sensitivity if the pull-up latching rate is higher than the pull-down latching rate, and NFET mismatches dominate otherwise. This dependence is expressed in (5)-(7). The load capacitance sensitivity for the CMOS case is substantially lower if the n and p latches are simultane- I 2msum + mcap) 2 ) msum (33) \ l+2i / 8 T ~ oapproximations are involved-one in the evaluation of the symmetric solution and one in the evaluation of a particular integral. The details are described in [81 and [91. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 10, OCTOBER 1991 1422 whe:re (34) (35) The criterion stated above contains the largest term for each kind of mismatch. Except for load capacitance mismatch, these terms are analogous to the dominant terms of (17). Note that each of these terms reduces to the largest terms in the old formula of (17) in the case that K , = K,. John L. Wyatt, Jr. (S’75-M’78) received the S.B. degree from the Massachusetts Institute of Technology (M.I.T.), Cambridge, the M.S. degree from Princeton University, Princeton, NJ, and the Ph.D. degree from the University of California at Berkeley, in 1968, 1970, and 1978, respectively, all in electrical engineering. After a post-doctoral year in the Department of Physiology at the Medical College of Virginia, he joined the faculty of the Electrical Eneineering and ComDuter Science Deoartment at M.I.T., where he is currently a Professor. His research interests include nonlinear circuits and systems and analog VLSI for real-time robotvision, [ l l W. T. Lynch and H. J. Boll, “Optimization of the latching pulse for dynamic flip flop sensors,” IEEE J . Solid-State Circuits, vol. SC-9, no. 2, pp. 49-54, 1974. [21 N. Ieda et al., “Single transistor MOS RAM using a short channel MOS transistor,” IEEE J . Solid-State Circuits, vol. SC-13, no. 2, pp. 218-224, 1978. N. N. Wang, “On the design of MOS dynamic sense amplifiers,” IEEE Trans. Circuits Syst., vol. CAS-29, no. 7, pp. 467-477, 1982. K. Natori, “Sensitivity of dynamic MOS flip-flop sense amplifiers,” IEEE Trans. Electron Deuices, vol. ED-33, no. 4, pp. 482-488, 1986. R. Kraus and K. Hoffman, “Optimized sensing scheme of DRAM’S,” IEEE J . Solid-State Circuits, vol. 24, no. 4, pp. 895-899, 1989. T. E. Stern, Theory of Nonlinear Networks and Systems. Reading, MA: Addison Wesley, 1965, pp. 228-239. G. Birkhoff and G. C. Rota, Ordinury Differential Equutions, 3rd ed. New York: Wiley, 1978, p . 163. R. Sarpeshkar, J. L. Wyatt, Jr., N. C. Lu. and P. D. Gerber. “Analysis of mismatch sensitivity in a simultaneously latched CMOS sense amplifier,” Microsystems Technology Labs., M.I.T., Cambridge, MA, VLSI Memo 90-603, 1990. [91 R. Sarpeshkar, J. L. Wyatt, Jr., N. C. Lu, and P. D. Gerber, “Analysis of mismatch sensitivity in a simultaneously latched CMOS sense amplifier,” submitted to IEEE Trans. Circuits Svst. Nicky C. Lu (S’76-M’81-SM’SS-F91) received the B.S.E.E. degree from National Taiwan University in 1975 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1978 and 1981, respectively. H e served in ROTC from 1975 to 1977. From 1978 to 1982 he was Research Assistant at the Stanford I C Lab and Associate Professor of National Chiao-Tung University. From 1982 to 1990 he worked for IBM, first as a Research Staff Member and then as Manager of a DRAM group at the T. J. Watson Research Center of IBM Research Division, Yorktown Heights, NY. After serving a year on the Technical Planning Staff for the IBM Director of Research, he joined IBM Technology Products Headquarters as Program Manager responsible for improvements of development and management processes in semiconductor, packaging, and design automation areas. Then he joined the Etron group, where he is now President of Etron Research Inc., U.S.A. and Etron Technology, Inc., Taiwan, R.O.C., specializing in VLSI chip design and technology. His technical interests focus on VLSI memory chip design and technology, 3 D device structures, and ASIC design. He has authored over SO technical papers and more than 12 U S . patents. Dr. Lu has received a Stanford Fellowship, numerous IBM awards which include several Outstanding Innovation and Technical Achievement Awards, and one IBM Corporate Award to recognize his contributions to memory technology. H e has served on the ISSCC Technical Program Committee since 1987, and as Chairman of the memory subcommittee since 1989. H e also served on the Technical Program Committees of the International Symposium on VLSI Technology, Systems and Applications, and the 1990 Symposium on VLSI Circuits. H e was a Guest Editor for the 1989 Memory and Logic Special Issue of the I E E E CIRCUITS.H e is a member of Sigma Xi, Phi JOURNALOF SOLID-STATE Tau Phi, and an IEEE Fellow for his contributions to semiconductor memory design and technology. Rahul Sarpeshkar was born in Bangalore, India. H e received the Bachelor’s degrees in electrical engineering and physics, both from the Massachusetts Institute of Technology, Cambridge, in 1990 H e is currently a second year graduate student in the Department of Computation and Neural Systems, California Institute of Technology, Pasadena, in Prof Carver Mead’s lab. His research interests are in the field of andlog VLSI and neural system\. Mr. Sarpeshkar is a member of Tau Beta Pi and Sigma Pi Sigma. This work, conducted during his internship at IBM’s T. J. Watson Re.search Center and stay at M I T., was the subject of his bachelor’s thesis and received an award for thesis excellence from the M.I.T. Department of Electrical Engineering and Computer Science. Porter Dean Gerber received the B S degree in mathematics from the California Institute of Technology, Pasadena, in 1962, and the M.S. and Ph.D. degrees in applied mathematics from the Courant Institute of Mathematical Sciences in 1965 and 1968, respectively H e spent one year at Aerospace Corporation in El Segundo, CA, working in numerical analysis and large-scale scientific computation. H e joined IBM Corporation in 1968, where he has done applied work in electron-beam lithography and theoretical work in the explicit solution of quadratic differential equations. H e is a Research Staff Member in the Mathematical Sciences Department at the IBM Thomas J. Wdtson Research Center, Yorktown Heights, NY. ACKNOWLEDGMENT The authors thank Dr. L. Terman at the IBM T. J. Watson Center for his suggestions and advice on this publication, and D. Standley at M.I.T. for his help. REFERENCES