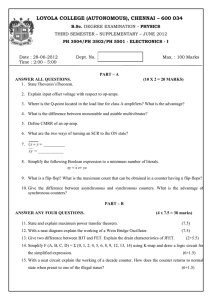

The Electronics Handbook

advertisement