APPLICATION NOTE

Timing and Synchronization Division

8V49NS0312 Evaluation Board rev B. Short Form User Guide

Quick Start: Powering Up the Board

(1)

(2)

(3)

(4)

(5)

(6)

(7)

Configure the lab power supply to 3.3V with a 700mA limit. Turn off the output.

Set POWER_SEL (JP21) to select VCC_INPUT.

Remove all output terminations.

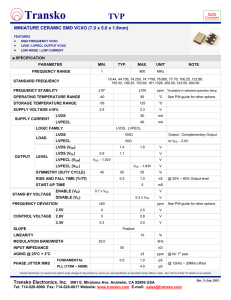

Set Dip Switch selectors to the positions shows in Figure 1.

Connect VEE to the GND jack (J22).

Connect the 3.3V source to POWER (J90)

Turn on the Power Supply. The current should measure ~503mA

Optional (for I2C programming through Timing Commander)

(8) Connect a cable from a PC to the USB port.

Once correct operation is verified, set the power supply limit for the number of outputs to be active.

The board ships with a 50MHz crystal and with the DIP Switch settings from Figure 1 it will be configured

as follows:

QA1=QA2=QB1=QB2=156.25MHz, LVDS levels

QC0=QC1=QD0=125MHz, LVDS levels

QD1= High Impedance

When evaluating performance with the default hardware configuration, it is recommended that all active

outputs be terminated 50ohms to GND by either terminator plugs or an instrument.

Bank A: this device supports four outputs for bank A, but only QA1 and QA2 have been routed. This bank’s

termination is configured for LVDS operation and will not switch if set to LVPECL levels unless the

terminations are modified. For LVPECL operation, please consult the “Output Configuration” section of this

document.

Bank B: this device supports four outputs for bank A, but only QB1 and QB2 have been routed. This bank’s

termination is configured for LVPECL operation. For LVDS operation, please consult the “Output

Configuration” section of this document.

Bank C: this bank’s termination is configured for LVDS operation and will not switch if set to LVPECL

levels unless the terminations are modified. For LVPECL operation, please consult the “Output

Configuration” section of this document.

Bank D: QD0 is terminated for LVDS operation and will not switch if set to LVPECL levels unless the

terminations are modified. For LVPECL operation, please consult the “Output Configuration” section of this

document.

8V19NS0312 Evaluation Board User Guide

June 2016

Board Overview

Use the following diagram to identify: power supply jacks, USB connector, input and output SMA

connectors, etc.

Figure 1. Evaluation Board Top View

A

CLK

QA1

QB1

C

QA2

B

QB2

D

QC0

QD0

QC1

HMH MHMMH

L L L MMMMM

G

E

REVISION A 10/13/2015

J

H

F

2

©2014 Integrated Device Technology, Inc.

8V19NS0312 Evaluation Board User Guide

June 2016

Legend

Inputs

CLK

nCLK

Clock input line. Can be configured for differential or single-ended input.

nClock input line.

Outputs

QA1

QA2

QB1

QB2

QC0

QC1

QD0

QD1

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Can be configured for either LVPECL or LVDS output levels.

Single-ended LVCMOS output.

Other

A

B

C

D

E

F

G

H

J

USB connector

8V49NS0312- the device to be evaluated

Through-hole HC-49 Crystal Socket (Optional)

SMD 50MHz Crystal

Dip Switch for DC control signals (NAx, NBx, NCx, NDx)

Dip Switch for DC control signals (FINx, REF_SEL)

Power Select (Default is 3.3V input)

Power Jack

Ground Jack

REVISION A 10/13/2015

3

©2014 Integrated Device Technology, Inc.

8V19NS0312 Evaluation Board User Guide

June 2016

For more questions or support, feel free to contact us at clocks@idt.com

CORPORATE

HEADQUARTERS

6024 Silver Creek Valley

Road

San Jose, CA 95138 USA

for SALES:

1-800-345-7015 or

408-284-8200

fax: 408-284-2775

www.idt.com

for Tech Support:

email: clocks@idt.com

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the

products and/or specifications described herein at any time and at IDT’s sole discretion. All information in

this document, including descriptions of product features and performance, is subject to change without

notice. Performance specifications and the operating parameters of the described products are determined in

the independent state and are not guaranteed to perform the same way when installed in customer products.

The information contained herein is provided without representation or warranty of any kind, whether

express or implied, including, but not limited to, the suitability of IDT’s products for any particular purpose,

an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This

document is presented only as a guide and does not convey any license under intellectual property rights of

IDT or any third parties. IDT products are not intended for use in life support systems or similar devices

where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the

health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an

express, written agreement by IDT.

Copyright 2014. All rights reserved. Product specifications subject to change without notice. Integrated

Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service

marks used herein, including protected names, logos and designs, are the property of IDT or their respective

third party owners.

Rev. 02-27-2014

REVISION A 10/13/2015

4

©2014 Integrated Device Technology, Inc.