Document

advertisement

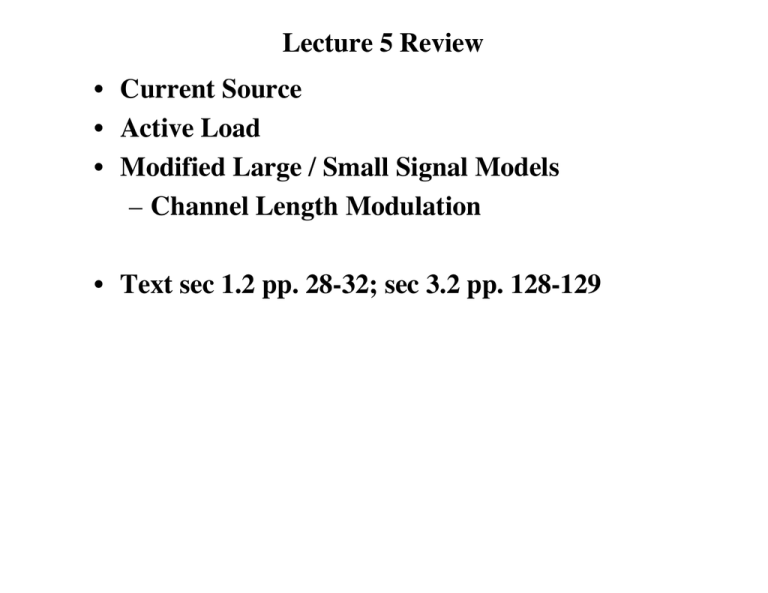

Lecture 5 Review

• Current Source

• Active Load

• Modified Large / Small Signal Models

– Channel Length Modulation

• Text sec 1.2 pp. 28-32; sec 3.2 pp. 128-129

Current source

• Ideal goal

• Small signal

model:

Open circuit

“RD=∞”

Realizing current source: MOSFET

• Large signal nonideality: Compliance range

• “Looks like” current source only for VDS>Veff

MOSFET ID-VDS characteristic for fixed VGS

• Small-signal nonideality: slope in active region

Cause: Channel length modulation

Channel length modulation

Channel length modulation

Modify small-signal model: Finite rds current source

• Slope = ∆I/∆V

rds =

DV

DI

SLOPE =

DI

1

=

DV rds

• Ideal:

zero slope

fi rds = ∞

Caution: rDS(on) vs. rds confusion!

rDS(on)

– Triode region

– Large signal

– True resistance

(V-I through origin)

rds

– Active region

– Small signal

– Models nonideality

of current source

Refined MOSFET Small Signal Model

•

•

•

•

Add rds in parallel with gmvgs current source at output

SAME FOR N-ch, P-ch

How to relate rds to DC operating point?

Example: gm = 2ID/Veff

ID- VDS Characteristic for Different VGS

"Family" of curves

ID- VDS Characteristic for Different VGS

Extrapolate backward: intersect at VDS-axis

1/slope provides small signal resistance rds

• Intersect at -1/l

Slope:

1

ID

1

=

fi rds =

rds 1 l

lI D

MOSFET small signal model

2I D

gm =

Veff

rds =

1

lI D

Increasing Gain

• Typical gain (resistive load)

– Lab 4 example: |av | ≈ 2

– Class example: |av | ≈ 11.1

• How to increase av?

Transconductance gm

• Definition

dID

gm =

dVGS

Transconductance gm

• Definition

• ID from

Square law:

• gm in terms of

W/L, Veff

dI D

gm =

dVGS

È

˘

dID

d Í m nCox W2

2

=

VGS - Vtn ) ˙

(1

dVGS dVGS Í 2

L2 4243 ˙

Veff

Î

˚

W2

gm = m nCox

Veff

L2

Summary of gm expressions

• All equivalent!

choose whichever

gives easier math

• Can’t memorize?

rederive from

definition of gm

dID

gm =

dVGS

W2

gm = m nCox

Veff

L2

gm =

2I D

Veff

W

gm = 2mnCox ID

L

Common source circuit (Lab 4)

Setting operating point:

Adjusted function generator offset for DC

output at midpoint of signal swing

Common source circuit (Lab 4)

• DC operating point

• Chosen for “halfway”

between rails

• ID=1.25mA

• Veff ≈ 2.0V (depends

on parameters)

VOUT = VDD - I D RD

VOUT = +2.5V

VDD - VOUT

ID =

RD

5V - 2.5V

=

= 1.25mA

2kW

Common source circuit (Lab 4)

• Small signal gain

magnitude = 2.5

• Not impressive!

gm =

2I D 2(1.25mA)

=

Veff

2.0V

gm = 1.25mA / V

av = -g m RD = -(1.25mA/ V)(2 kW)

av = -2.5

How to increase av?

Look at gain expression:

av = gm RD

Increase RD

• New RD = 10kΩ (5X old value)

• Problem:

VOUT = VDD - I D RD

DC operating point

VOUT = 5V - (1.25mA)(10kW)

1442443

• Violates condition for

12.5V

active region: triode! V

OUT = -7.5V ?

• DC operating point

stuck at negative rail

Look at problem symbolically

• Use gm=2ID/Veff

• IDRD = DC drop on load

• Optimal bias at output:

constrained to VDD / 2

• ID, RD not involved!

2ID

gm =

Veff

2I R

av = gm RD = D D

Veff

VDD

ID RD =

2

V

av = DD

Veff

• Value of approximate symbolic approach

vs. “exact” numerical results from simulation

How to increase gain (resistive load)

• increase VDD

– usually fixed by

application, process

• decrease Veff

– does increase gm

– but ...

VDD

av =

Veff

Problems decreasing Veff

• Veff, W/L gm expression:

W

• 2X increase in gm:

gm = 2mnCox ID

4X increase in size

L

(can’t increase IDRD)

• Increased area:

cost penalty

• Increased capacitance

speed penalty

• Veff < ≈ 200 mV: subthreshold region

– Not square law: gm expressions invalid

Increase av: Different approach

• Give up on resistive load ...

• What is highest resistance?

Increasing av: Different approach

• What is highest resistance?

• Infinite: open circuit

• Problem: no path for ID

• Any circuit element that:

– provides DC current, but

– is open circuit in small signal model?

Current source!

• Open in small

signal model

• Realizing current

source: MOSFET

Lab Circuit: MOSFET with active load

• Small signal model

for M1

• Thevenin equivalent

“looking into”

drain of M2

(see text sec. 3.1)

Small signal model

M1 common source

M2 Thevenin

equivalent

Simplify small signal model

Combine rds1, rds2 in parallel

Small signal gain

vout

= av = -gm1 (rds1 rds2 )

vin

Current source load: Large signal considerations

Output swing limits

• Top:

M2 “crash” into triode

• Bottom:

M1 crash into triode

Common Source with Active Load

• DC Sweep Schematic

Active Load Simulation Result (DC Sweep)

Determining DC Operating Point

Set small

signal vin = 0

Determining DC Operating Point

• Active region:

Veff determines ID

• Correct VIN:

M1, M2 “agree”

• Example:

Veff1 = 1.0V

ID = 100 µA

If DC bias at input is “wrong”?

• Current source

"disagreement"

• KCL crisis at output:

2µA, nowhere to go

• What happens?

If DC bias at input is “wrong”?

• Capacitance

at output node Vout

• 2µA flows into cap,

charges up

fi VDS1 increases

fi I1 increases

• fi VDS2 decreases

fi I1 decreases

• Changes in VDS

cause changes in ID

until “agreement” is reached: ID1 = ID2

How much change in VDS?

• Changes in VDS cause changes in ID until

“agreement” is reached: ID1 = ID2 BUT

• Active region: ID is a weak function of VDS

• Large change in VDS for small change in ID

• Output very sensitive to changes in ID:

• Small ∆Veff at input fi Small ∆ID fi

Requires large ∆VDS at output for ID agreement

Good: high voltage gain

Bad: tricky to get correct input bias point

Frequency Domain Considerations

• Ideal op-amp goals:

– Infinite gain

– Infinite bandwidth

• Active load helps gain

• What about bandwidth?

Frequency Domain Analysis

• Start simple:

Assume single

CL at output

• (Ignore MOS

capacitances

for now …)

• Find transfer

function vout/vin

Small signal model

• Combine rds1||rds2 = rout

Simpler small signal model

• Combine rout CL into impedance ZL

Simplified Small Signal Model

• Small signal gain: vout/vin = av = -gmZL

• Frequency dependence of ZL provides

frequency dependence of transfer function

Closer Look at ZL:

• Impedance is parallel

combination of rout, 1/sCL

ZL = rout

1

1

=

1

sCL

+ sCL

rout

rout

ZL =

1 + srout CL

Behavior of ZL over frequency:

• Let s=jw

rout

ZL =

1 + jwrout CL

• Low frequency limit:mostly rout

1

rout

w <<

fi ZL =

ª rout

routCL

1 + jwrout CL

• High frequency limit: mostly CL

1

rout

rout

1

w >>

fi ZL =

ª

ª

routCL

1 + jwrout CL jwroutCL jwC L

Transfer function

• Substitute in ZL

vout

- gmrout

= - gm ZL =

vin

1 + jwrout CL

• Magnitude

vout

gm rout

=

vin

1 + (wrout CL )2

Bode Plot of Transfer Function Magnitude

vout

gm rout

=

vin

1 + (wrout CL )2

Magnitude vs. Frequency (log-log plot)

Bandwidth: w3dB

3-dB Frequency / Bandwidth

• Frequency at which magnitude is 3 dB down

(reduced by factor 1/√2)

vout

MAX

= gm rout AT w = 0

vin

vout

1

THEN AT w3dB,

=

gm rout

vin

2

1

gmrout

1

gmrout =

fi w 3dB =

2

2

routC L

1+ (w 3dBroutCL )

Revisit Bode Plot:

• Gain, Bandwidth inversely related!

Unity Gain Frequency wT / Gain-Bandwidth Product

• wT : Frequency at which magnitude is 1

Use approximation wT >> 1/routCL

1=

gm rout

1+ (wT rout CL )

2

ª

gm rout

(wT rout CL )

2

gm

fi wT =

CL

• Gain x Bandwidth Product

†

av = gm rout

w 3dB

1

=

rout CL

1

gm

fi gm rout ⋅

=

123 rout CL

CL

GAIN

123

BANDWIDTH

†

• Independent of rout!

– Poorly controlled rout OK

Summary: Active Load

• Active load DC considerations:

– Output swing limited by triode “crash”

– To voltage within Veff of rail

• Active load good news / bad news:

– Good news: high gain

– Bad news: very sensitive to input DC bias

Massage small signal gain result

• Small signal gain

• Look at parallel

combination

• Substitute

expression for rds

av = gm1( rds1 rds2 )

1

rds1 rds 2 =

1

1

+

rds1 rds2

1

rds1 rds 2 =

l 1ID + l 2 ID

1

rds1 rds 2 =

(l1 + l2 ) ID

Massage small signal gain result

• Small signal gain

• Substitute for gm,

parallel rds

• ID drops out!

av = gm1( rds1 rds2 )

2I

1

av = D

Veff1 (l1 + l 2 )I D

4244

3

{ 14

gm1

rds1 rds2

2

av =

(l1 + l2 )Veff1

Only l, Veff to work with

Improve Gain

• Reduce Veff

– Minimum ≈ 200 to 300mV (subthreshold)

– May not want to go that low (W,L too big)

• Reduce l1, l2

– How? Where does l1 come from?

Square law model with channel length mod

mn Cox W

ID =

(VGS - Vtn )2 1 + l VDS - Veff

2 44

L

14

424444

3

[ (

)]

I D -sat

ID-sat term (at pinchoff) + "extra"

Square law model with channel length modulation

mn Cox W

2

ID =

(VGS - Vtn ) 1 + l VDS - Veff

2 44

L

14

424444

3

[ (

I D -sat

• Fractional extra part is l(VDS-Veff)

• Meaning of l:

Fractional change in current ID per

volt change in VDS

)]

What causes change? Where does l come from?

• Change in effective channel length L

• One way to reduce l: longer L

• Change ∆L represents smaller fraction

After some semiconductor physics ...

• Definition of l

• Fractional

change

l=

DID DL

=

ID

L

l=

• Semiconductor

physics ...

(see J&M p. 26)

DI D ID

DVDS

1 DL

L DVDS

DL

=

DVDS

l=

1

L

2KS e 0

1

qNSUB 2 VDS - Veff

2KS e 0

1

qNSUB 2 VDS - Veff

• KS Silicon dielectric constant 11.8

• NSUB Substrate doping units /cm3

Sanity check: 1E+14 to 1E+17

• ∆VDS from active-triode edge to “large” VDS

• Caution: consistent length units on L, NSUB, e0

Substrate doping NSUB parameter

• Needed for SPICE

Extraction procedure:

1) Calculate slope from ID-VDS plot

2) rds = 1/slope (small signal model)

3) Calculate l

4) Calculate NSUB

Example

VDS-ID data from Lab 5 for P-channel MOSFET:

1) Calculate slope from ID-VDS plot

2) rds = 1/slope (small signal model)

3) Calculate l

ID = 482 µA

1

1

1

l=

=

=

= 0.052V -1

I D ⋅ rds ( 482mA)( 40.2kW) 19.4V

†

4) calculate NSUB

l=

1 2K Se0

1

L qN SUB 2 VDS - Veff

0.052V

-1

2(11.8)(8.85E -12F / m)

1

1

=

(1E - 5m) (1.6E -19coul ) N SUB 2 4.48V - 0.84V

N SUB = 3.32E + 22 m -3 = 3.32E +16 cm -3

†

VDS = 4.48 V

• For CD4007, L = 10µm = 1.0E-5m

• VDS, Veff for largest VDS data point

Simulation exercise

• Add NSUB to N-channel, P-channel models

• DC sweep for CS Amplifier with Active Load

Common Source with Active Load (DC)

• Sweep input over full range 0 to +5V

DC Sweep Around Operating Point